【新人ブログ ミンガラバー】VHDL初級編 part.5 ~テストベンチ作成~

ミンガラバー(Mingalaba)! 皆さんこんにちは!シーです。

VHDL初級編 part.5となりました。今回で初級編も最後となります。

VHDLについて最初よりは理解できたのではないでしょうか。

それでは、始めましょう!

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。

目次

テストベンチ(スティミュラスファイル)とは

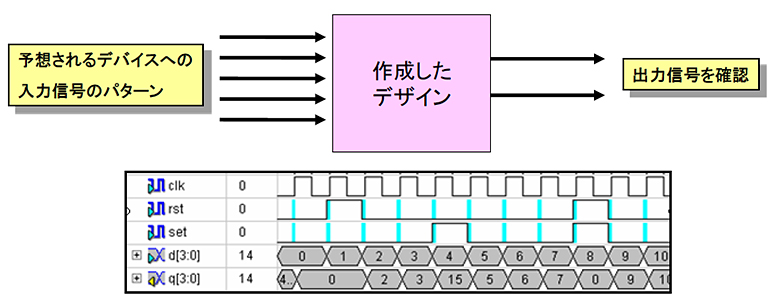

論理回路設計が仕様通りに作成されているか確認する際に、通常はシミュレーションを行いますが、テストベンチ(スティミュラスファイル)はシミュレーションで使用する確認用の入力信号データのことです。

今回は回路が正しく動いているかを確認するために、 テスト信号を入力するVHDLプログラムを作成します。

テストベンチのイメージは他のVHDL回路と同じですが、中身は上位階層を作成して、直接テスト信号を入力するイメージです。

図 1-テストベンチ

演習(5):テストベンチを理解する

事前条件

今回の演習では

- 1.Vivado® Design Suite HLx Edition

- 2.Windows 10 インストール済みPC

が必要となります。

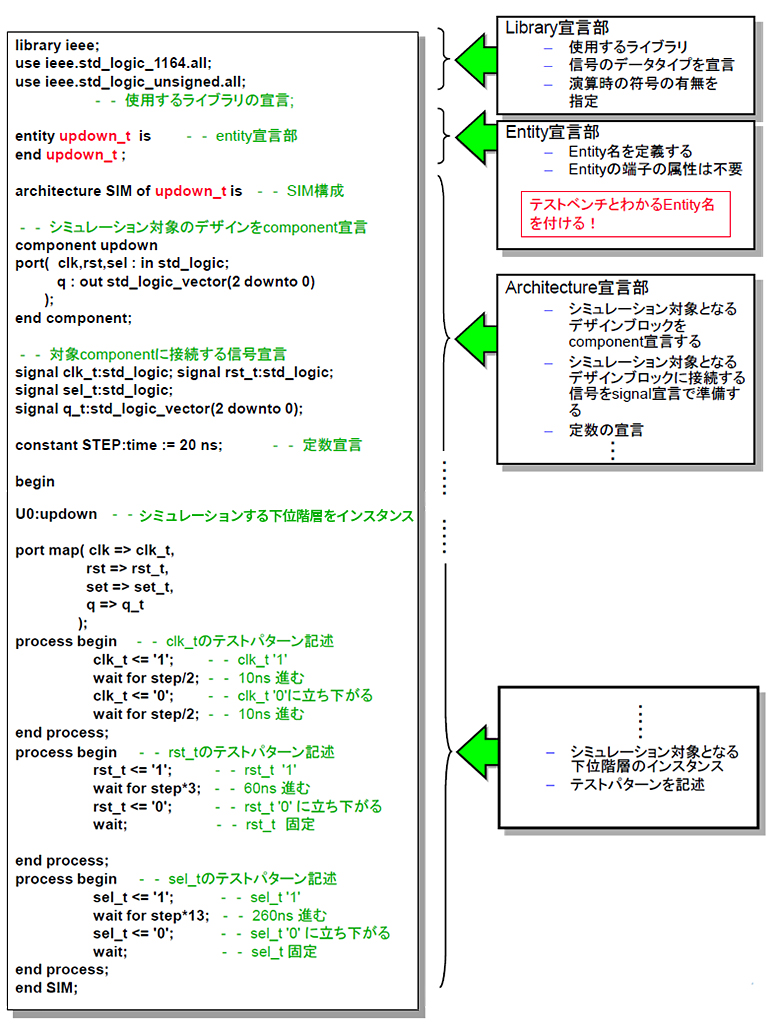

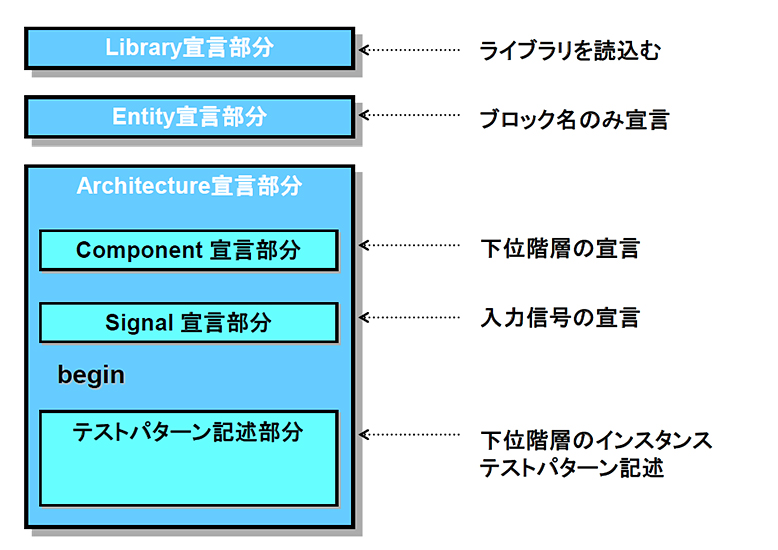

テストベンチファイルの全体構造

図 2-テストベンチファイルの全体構造

テストベンチファイルの書式構造

図 3-テストベンチファイルの書式構造

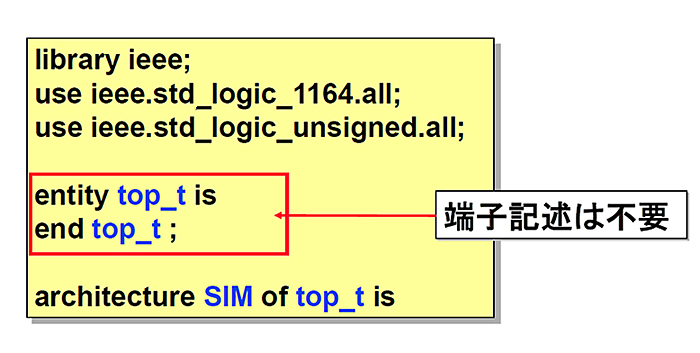

Library宣言 & Entity宣言

記述内容は論理記述用と同じです。

図 4-テストベンチのLibrary宣言 & Entity宣言記述例

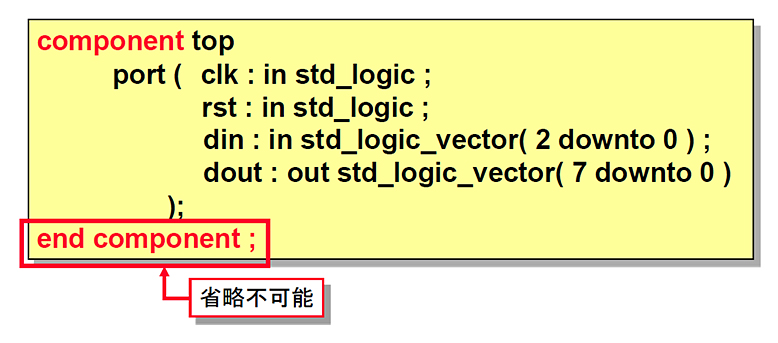

Component宣言

シミュレーションの対象となるブロックを宣言します。

デザイン全体をシミュレーションする場合、デザイン回路のTopを指定します。

図 5-テストベンチのComponent宣言記述例

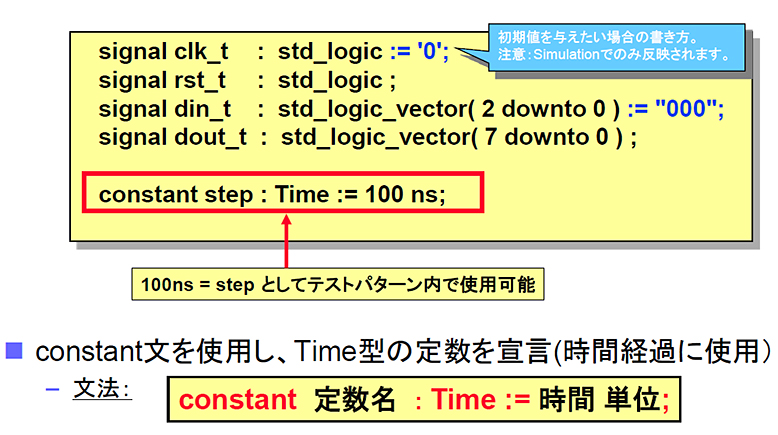

Signal宣言

インスタンスするデザインの入出力端子に対応する信号を宣言します。

これらをデザインと接続し、テストパターンを入力します。

信号名には元の回路の信号と接続しやすいため、元の信号名の最後に(_t)を追加して名前を作成するのが多いです。

例:テストされる元の回路の信号名:clk

テストベンチで接続するための信号名:clk_t

図 6-テストベンチのSignal宣言記述例

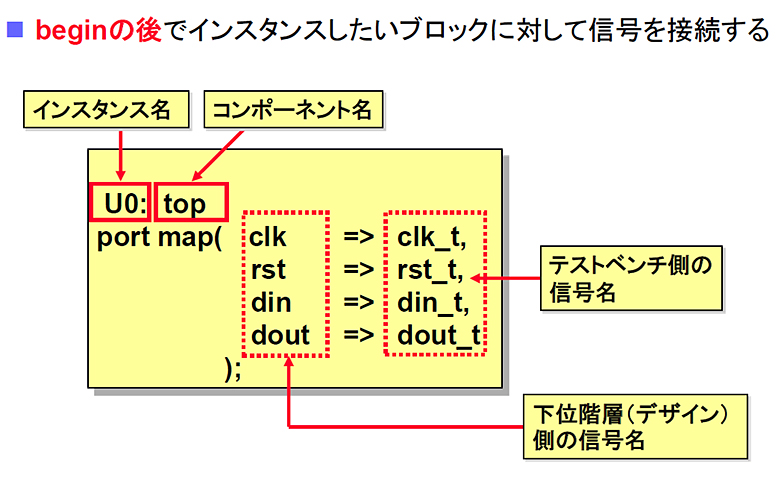

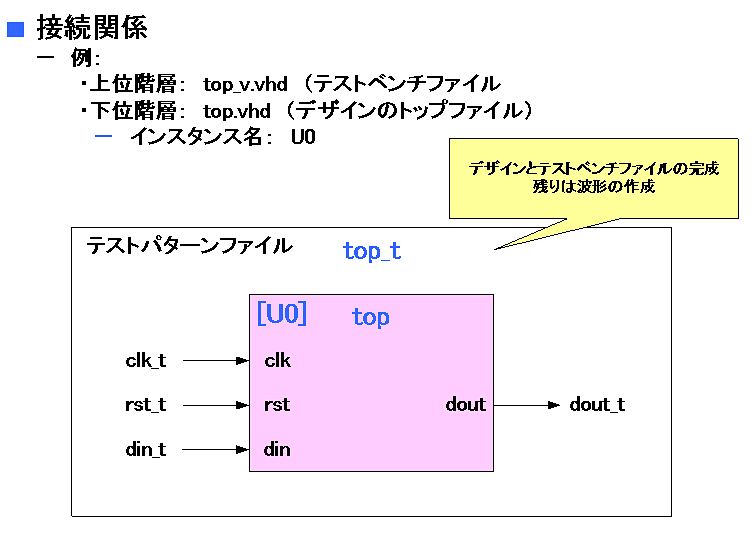

下位階層のインスタンス

図 7-テストベンチの下位階層のインスタンス①

図 8-テストベンチの下位階層のインスタンス ②

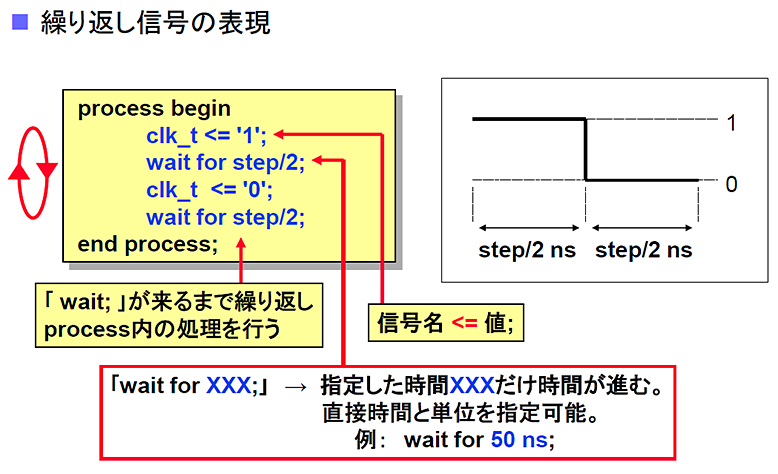

クロック信号の入力

基本的には、テストベンチに以下の3つを記述する必要があります。

- クロック信号の作成

- リセット信号の入力

- ターゲットの回路に入力信号の作成

図 9-クロック信号の入力

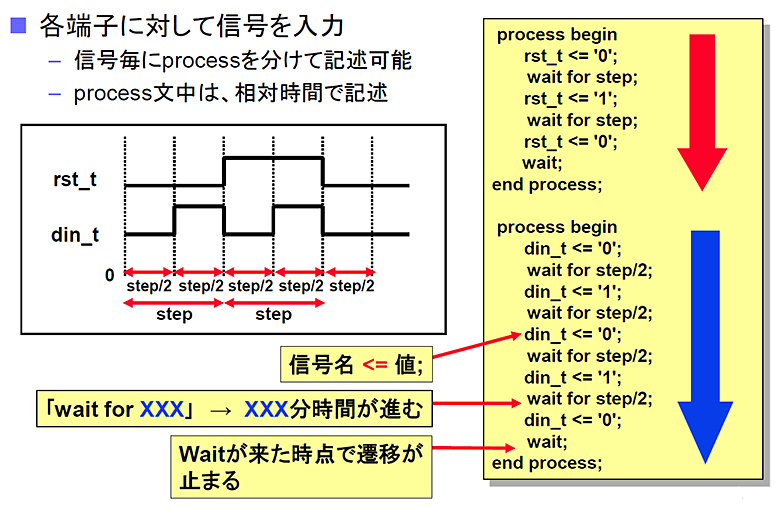

信号の入力

図 10-信号の入力

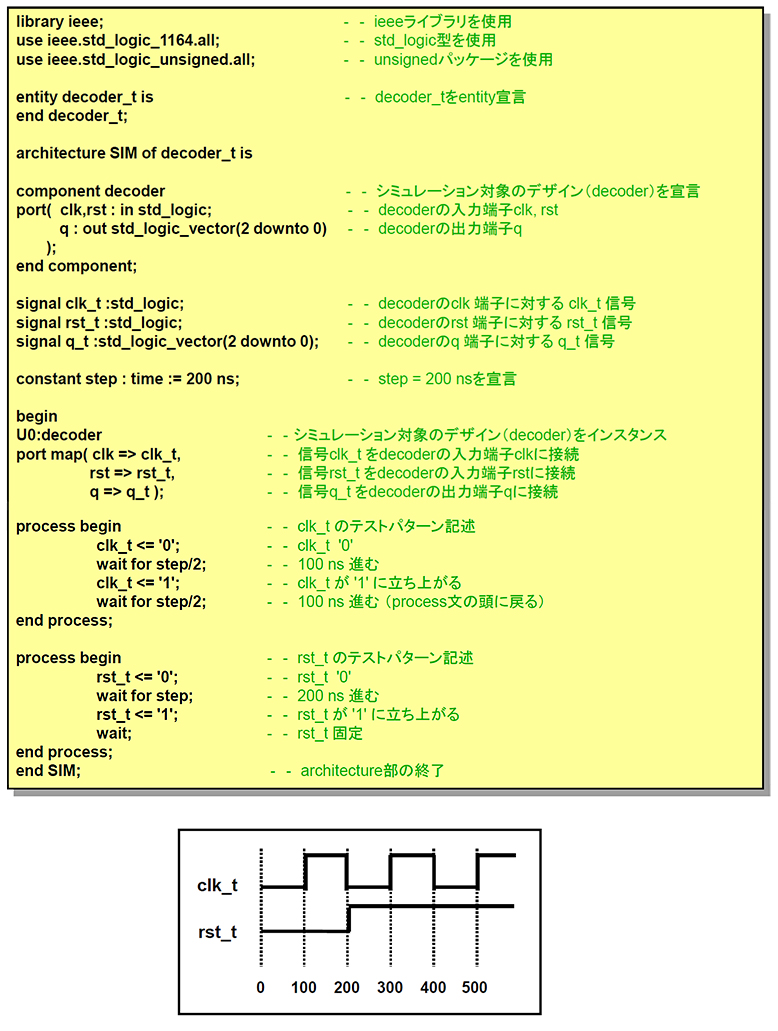

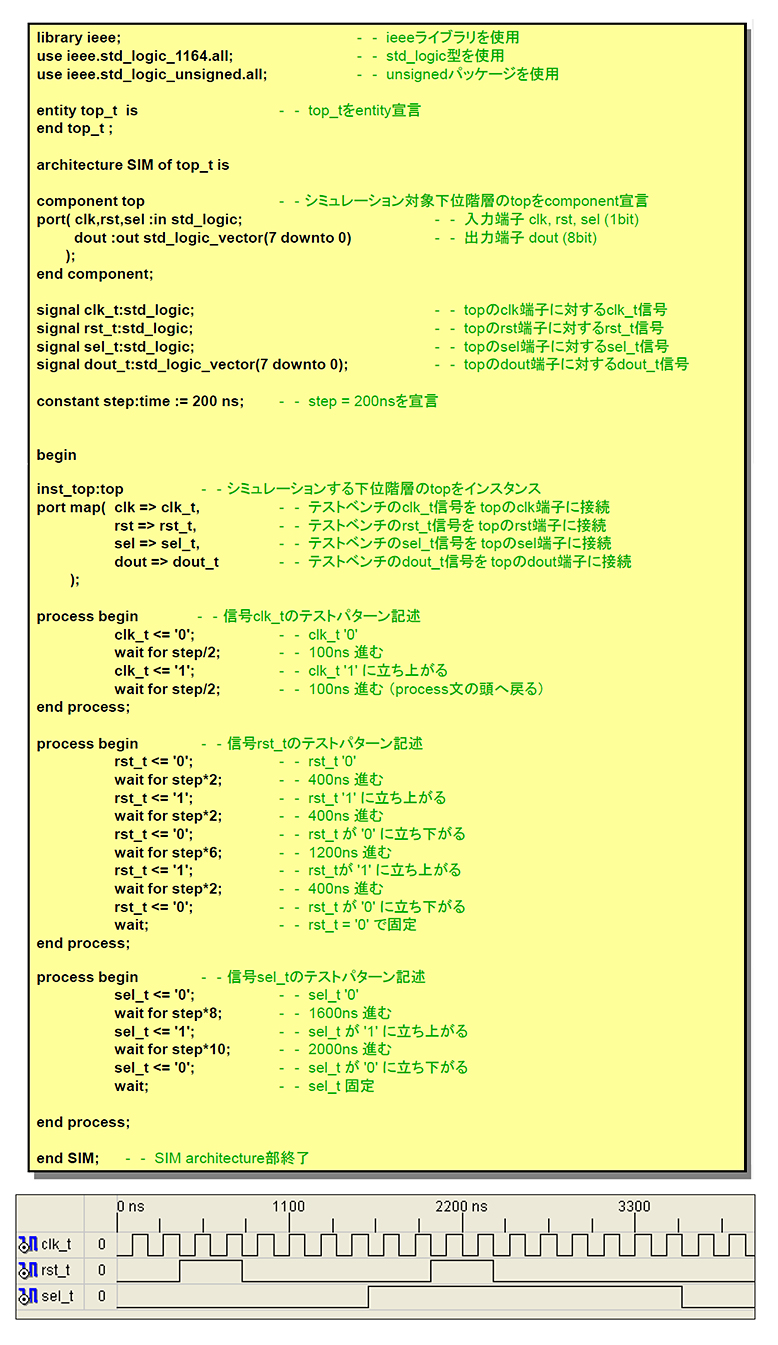

テストベンチ記述例

図 11-テストベンチ記述例

課題

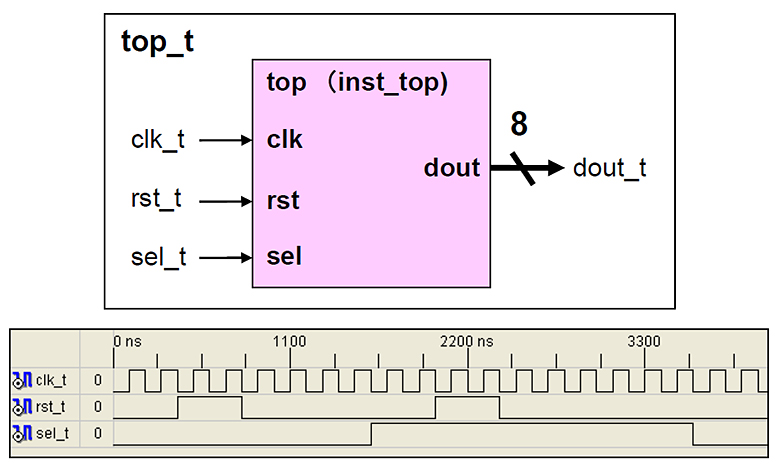

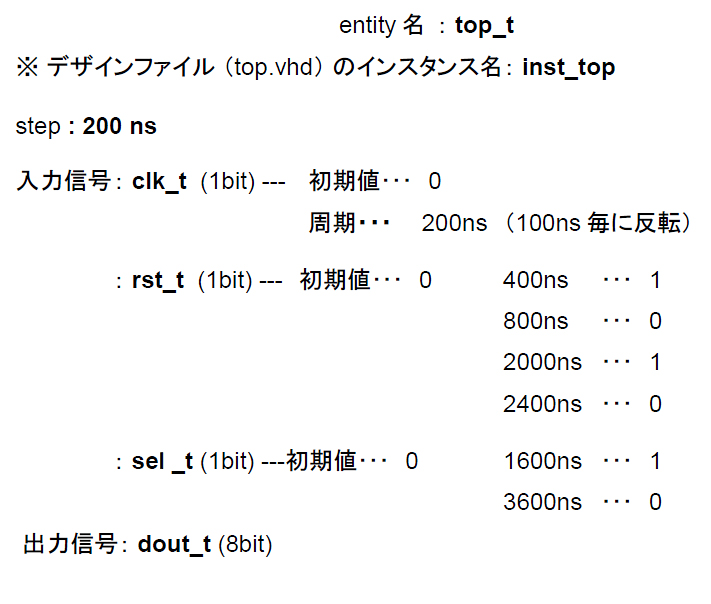

演習(4) で作成したデザインファイル(top.vhd)に対するテストベンチファイル(top_t.vhd)を作成し、Check Syntax後、Behavioral Simulationを実行してデザインの動作を確認してください。

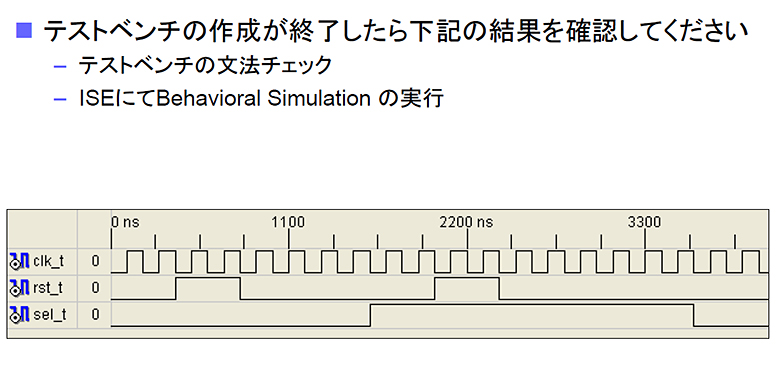

図 12-topテストベンチのイメージ図とテストパターン波形

図 13-演習(5)内容

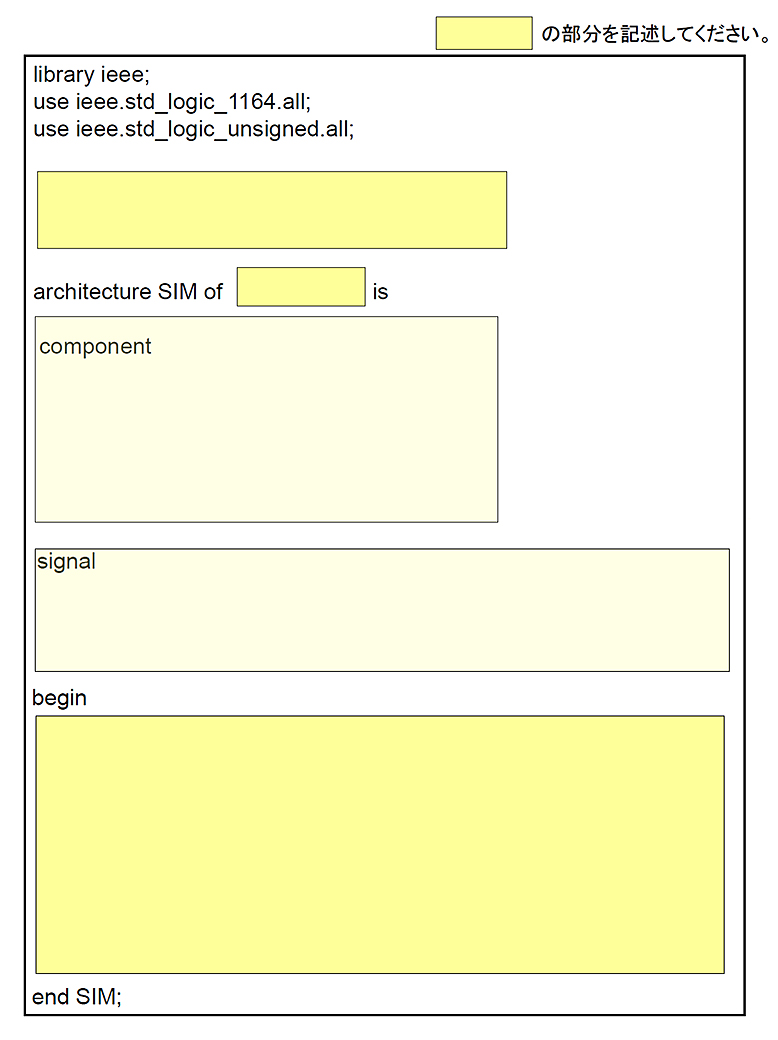

図 14-テストベンチ演習

図 15-テストベンチ演習の波形

Vivado® Design Suite の作業手順

作業手順は以下の通りです。

- テストベンチの作成

- テストベンチの追加

- テストベンチの完成

- シミュレーションの実行

1.テストベンチの作成

手順1

演習(1)での「Vivado® Design Suite の作業手順」 >「2.新規プロジェクト作成」 の手順を参照し以下のファイルをプロジェックトに作成します。

保存場所:C:\Home\VHDL (自分で適当にしても構いません)

ファイル名:top_t.vhd

手順2

以下のソースコードを記入するか、又はコピーしてからか貼り付けしてください。

library ieee; -- ieeeライブラリを使用

use ieee.std_logic_1164.all; -- std_logic型を使用

use ieee.std_logic_unsigned.all; -- unsignedパッケージを使用

-- top_t の entity 部分 Start↓

-- top_t の entity 部分 End↑

-- top_t の architecture 部分 Start↓

architecture SIM of is

begin

end SIM; -- top_t の architecture 部分 手順3

作成したファイルを保存します

2.テストベンチの追加

手順1

演習(3)の「1.updown.vhdファイルの追加」の手順 の手順を参照して、 以下のファイルをプロジェックトに追加します。

保存場所 :C: \Home\VHDL (自分で作成したファイルの保存場所)

ファイル名 :top_t.vhd

3.テストベンチの完成

手順1

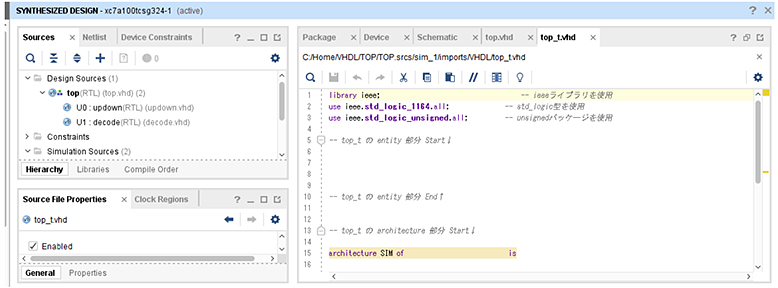

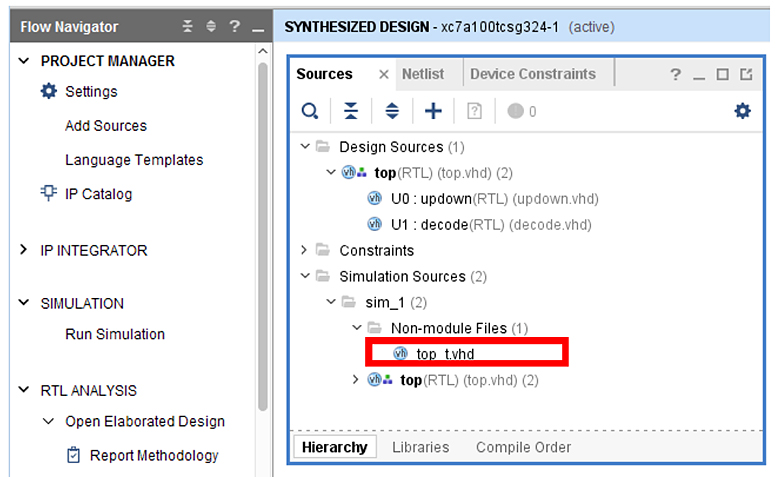

ファイルを開きます。

Sourceウィンドウに表示されている top_t.vhdファイルをダブルクリックします。

図 16-Simulation Sourceを表示

手順2

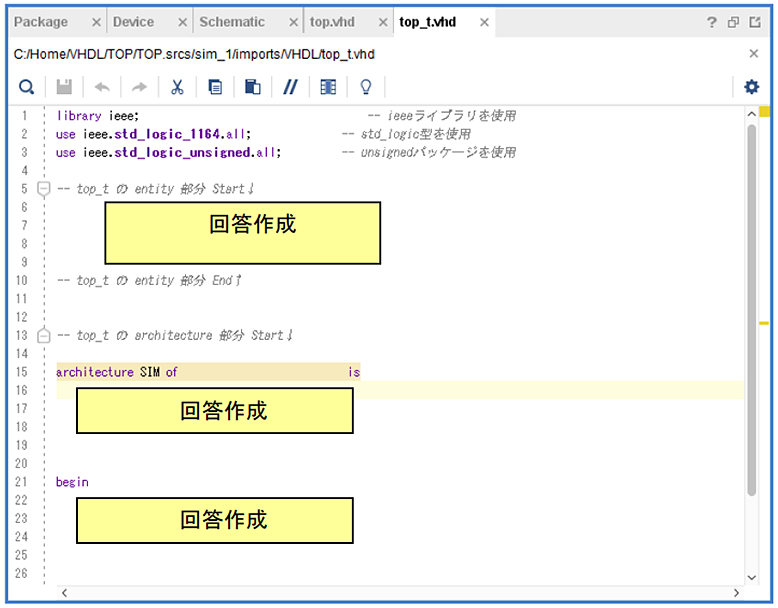

ファイルが開き、作成途中のテストベンチ記述が表示されます。

※画像クリックで大きな画像が表示されます。

図 17-テストベンチを表示

手順3

テストベンチを完成させます。

ファイル内の空欄を埋めて、ファイルを完成させて、保存してください。ファイルを保存する際、メニューバー:File - Save File As を選択するか、 又は、 “保存”ボタン をクリックしてください。

をクリックしてください。

図 18-ファイル編集画面

4.シミュレーションの実行

手順1

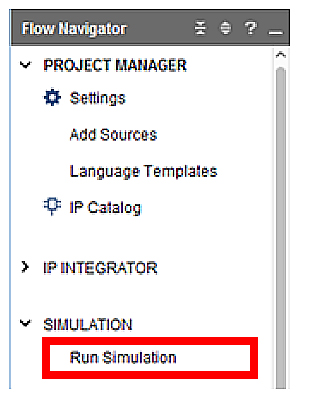

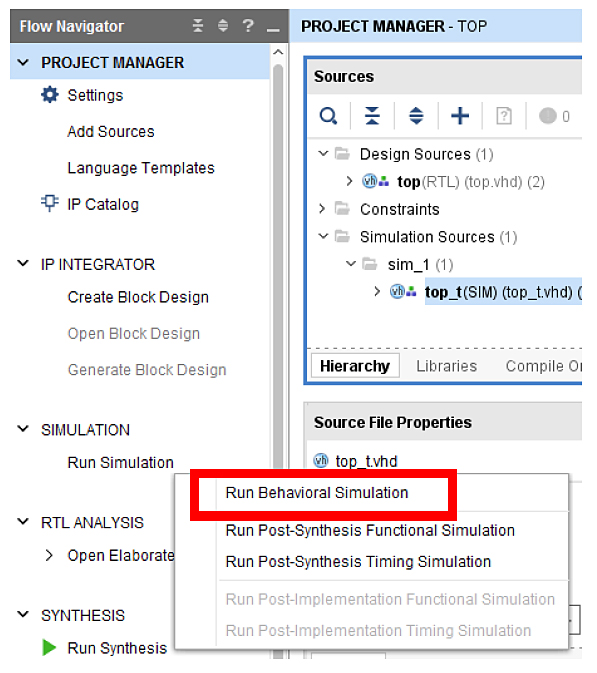

シミュレーションを実行します。

Run Simulation をクリックします。

図 19-Run Simulationの実行

手順2

シミュレーション種別選択して実行します。

Run Behavioral Simulationを選択します。

図 20-Run Behavioral Simulationの実行

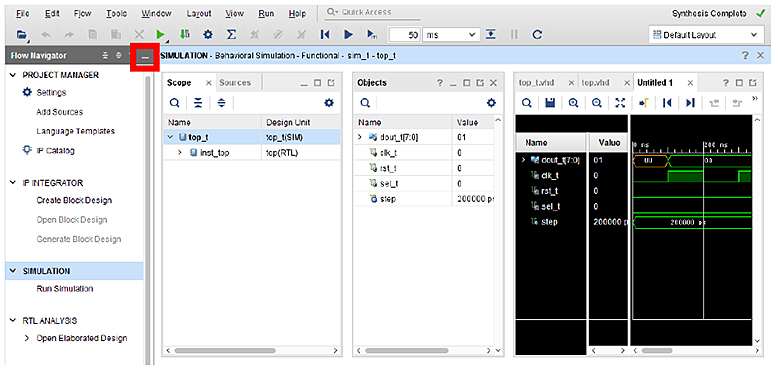

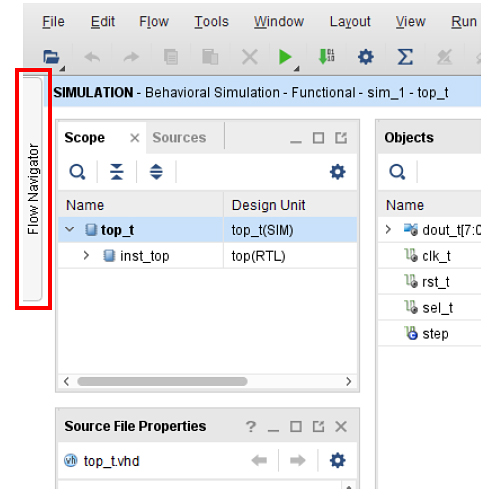

手順3

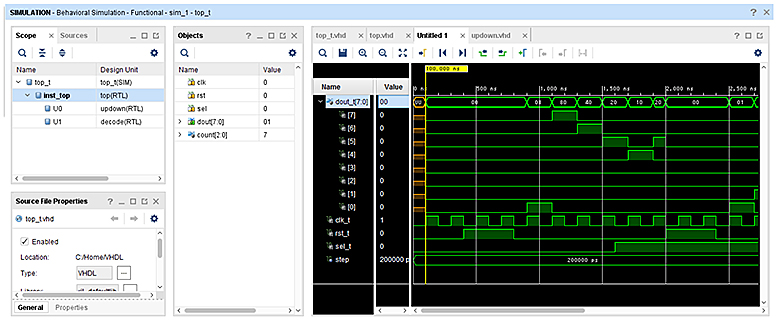

シミュレーション画面が起動します。

画面が見やすいように、Flow Navigatorの右端の  アイコンをクリックして、折りたたんでおきます。

アイコンをクリックして、折りたたんでおきます。

※画像クリックで大きな画像が表示されます。

図 21-Run Behavioral Simulationの実行画面

なお、折りたたんだ「Flow Navigator」は、縦になったタブをクリックすると元に戻ります。必要に応じて、元に戻してください。

図 22-Flow Navigatorの折りたたみ状態

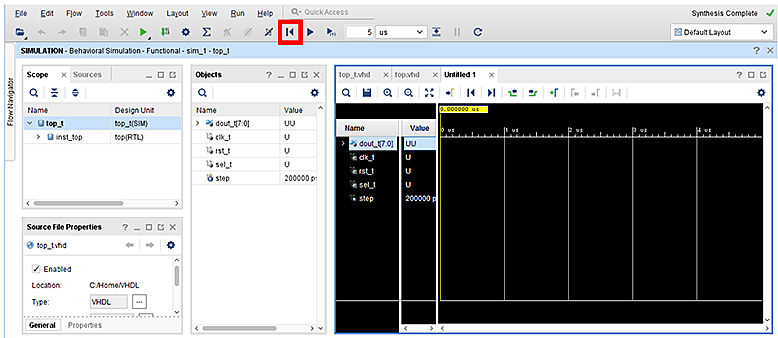

手順4

シミュレーション時間を0時間に戻します。

Restartアイコン  をクリックしてください。

をクリックしてください。

※画像クリックで大きな画像が表示されます。

図 23-シミュレーションのRestart

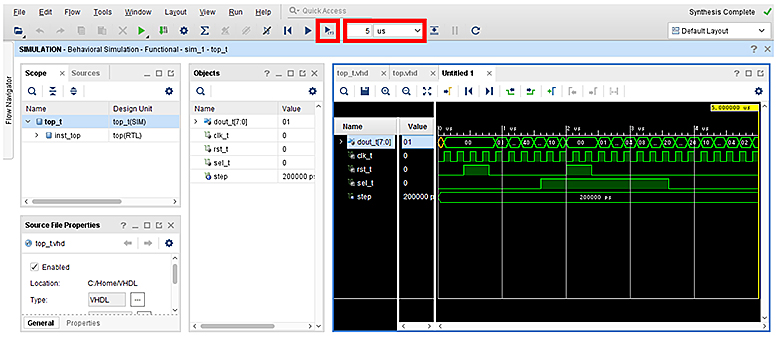

手順5

シミュレーション実行時間を5nsに設定して、 Run for timeアイコン  をクリックしてシミュレーションを5ns実行します

をクリックしてシミュレーションを5ns実行します

※画像クリックで大きな画像が表示されます。

図 24-5ns期間のシミュレーション実行

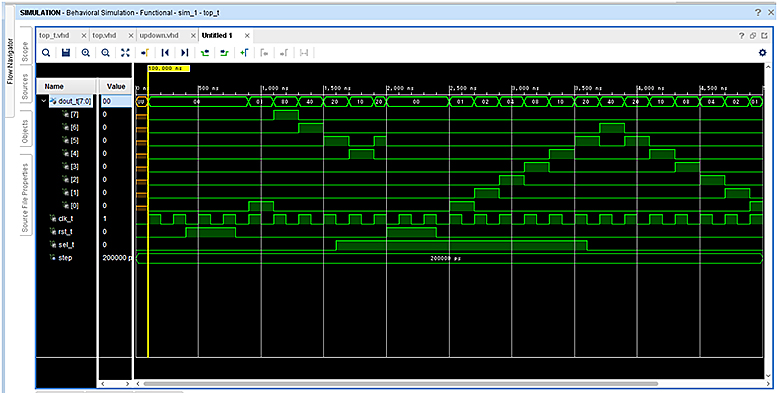

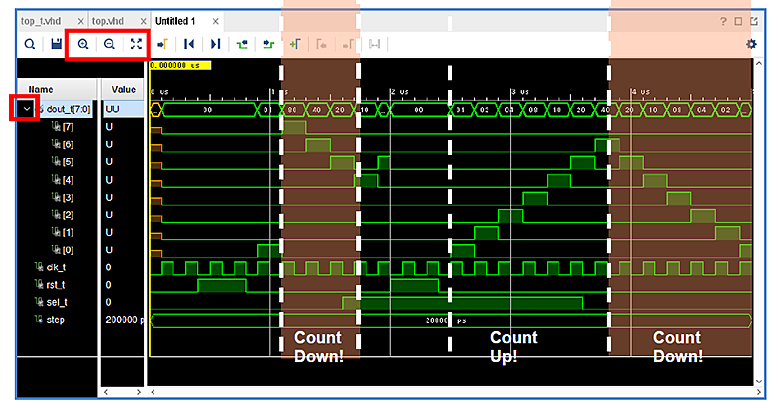

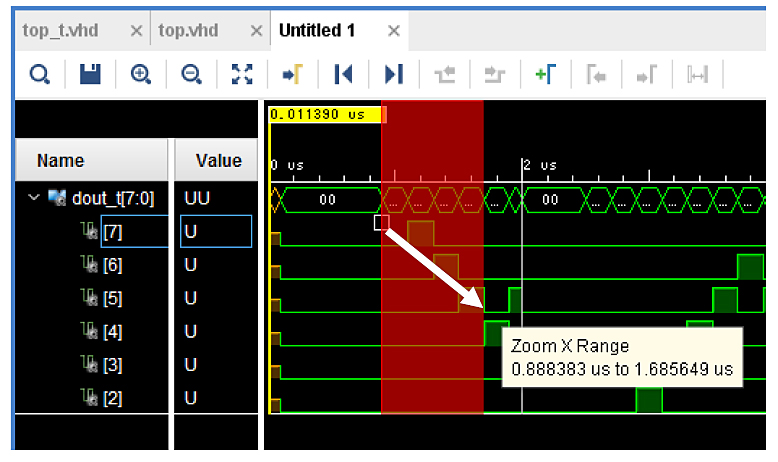

手順6 バス信号の展開表示

dout_t[7:0]信号の左側の  アイコンをクリックして、信号を展開表示します。

アイコンをクリックして、信号を展開表示します。

以下のシミュレーション結果となっていることを確認します。

図 25-シミュレーション結果波形

以下のアイコンで、波形の拡大、縮小、及び、シミュレーション波形の全体表示ができます。

![]()

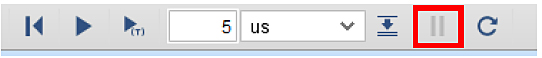

手順7

シミュレーション結果が期待通りではなかった場合、要因を特定し、それぞれの問題箇所を修正します。

- テストベンチ

- RTL

修正が完了したら、 Relaunch Simulationアイコン  をクリックして、テストベンチとRTLを再コンパイルして、再度シミュレーションを実行します。

をクリックして、テストベンチとRTLを再コンパイルして、再度シミュレーションを実行します。

特定範囲に波形拡大

波形表示ウィンドウで、右クリック+ドラッグをすることで、指定範囲を拡大することもできます。

図 26-シミュレーション波形拡大

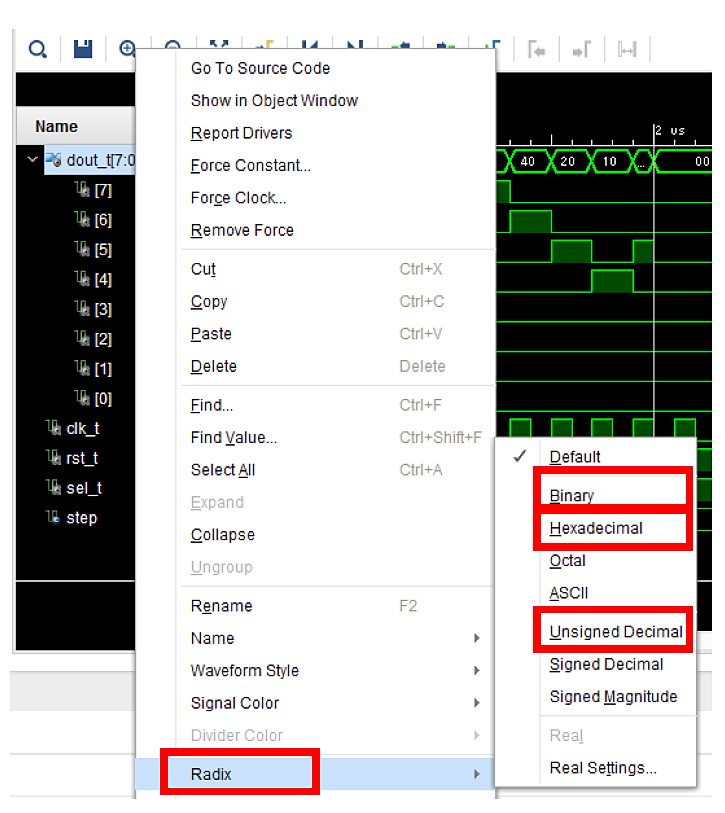

表示信号の10進数、2進数、16進数表示

信号名を選択して右クリックメニュー > Radix を変更することで、波形の表示形式を変更できます。

Hexadecimal :16進数

Unsigned Decimal:10進数

Binary :2進数

図 27-Radix選択メニュー

波形ウィンドウの最大化

波形表示ウィンドウを最大化、  アイコンをクリックすると、波形表示ウィンドウのみを表示できます。

アイコンをクリックすると、波形表示ウィンドウのみを表示できます。

※画像クリックで大きな画像が表示されます。

図 28-シミュレーション波形通常

波形表示ウィンドウの元のサイズに戻す、  アイコンをクリックすると、元に戻ります。

アイコンをクリックすると、元に戻ります。

※画像クリックで大きな画像が表示されます。

図 29-シミュレーション波形拡大

演習解答

図 30-演習(5)解答

作業を振り返って

テストベンチは、自分が作成した回路や動作不正の回路などの動作確認をしたい場合に、いろいろな信号を入力してテストするために作成される上位階層です。

テストベンチの記述も理解できたと思いますが、理解できない場合は練習が重要です。

今まで紹介した演習はすごく基本的な記述で、もし興味があればより有用なパターンを探して使用してみてください。

最後までお付き合いいただきありがとうございました!

何かご質問や不明点などがありましたら、いつでもご連絡ください。

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。

これからもTECHブログを通じて、皆様の設計にお役立てできればと思います。 VHDLの使い方、設計に関する問い合わせなどありましたら、ご連絡ください。