【新人ブログ ミンガラバー】VHDL初級編 part.4 ~階層設計~

ミンガラバー(Mingalaba)!

皆さんこんにちは!シーです。

VHDL初級編もpart.4となりました。今回の項目は「階層設計」です。

早速ですが、始めましょう!

このブログは「FPGA設計ブログ一覧」の

1. コーディング・IP設定・プリミティブ設定 のひとつです。

目次

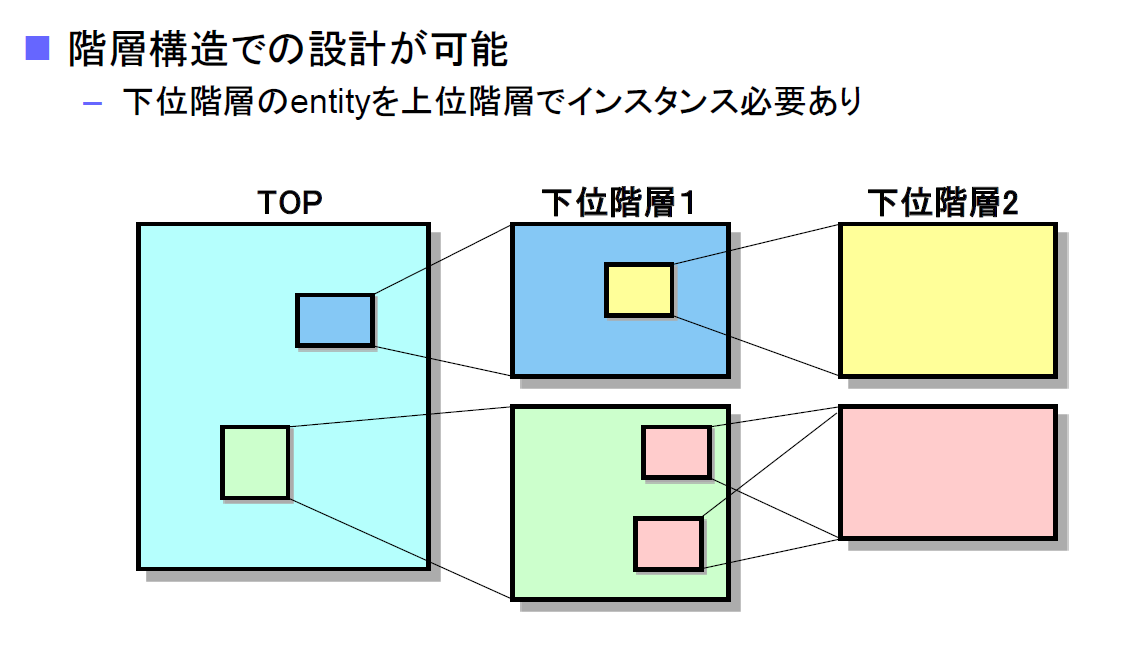

階層設計概要

階層設計について簡単に説明します。

演習(1)から(3)までに作成した回路は基本的な回路です。

回路の機能を使用して別の回路と組み合わせたい場合、機能が使用される回路は、下位階層となります。

機能を使用するために作成した回路は、上位階層となります。

上位階層と下位階層の関係を設計することが階層設計となります。

図 1-階層設計ブロック図

演習(4):下位階層のインスタンスを理解する

事前条件

今回の事前条件として、

1.Vivado® Design Suite HLx Edition と

2.Windows 10 インストール済みPC が必要となります。

下位階層

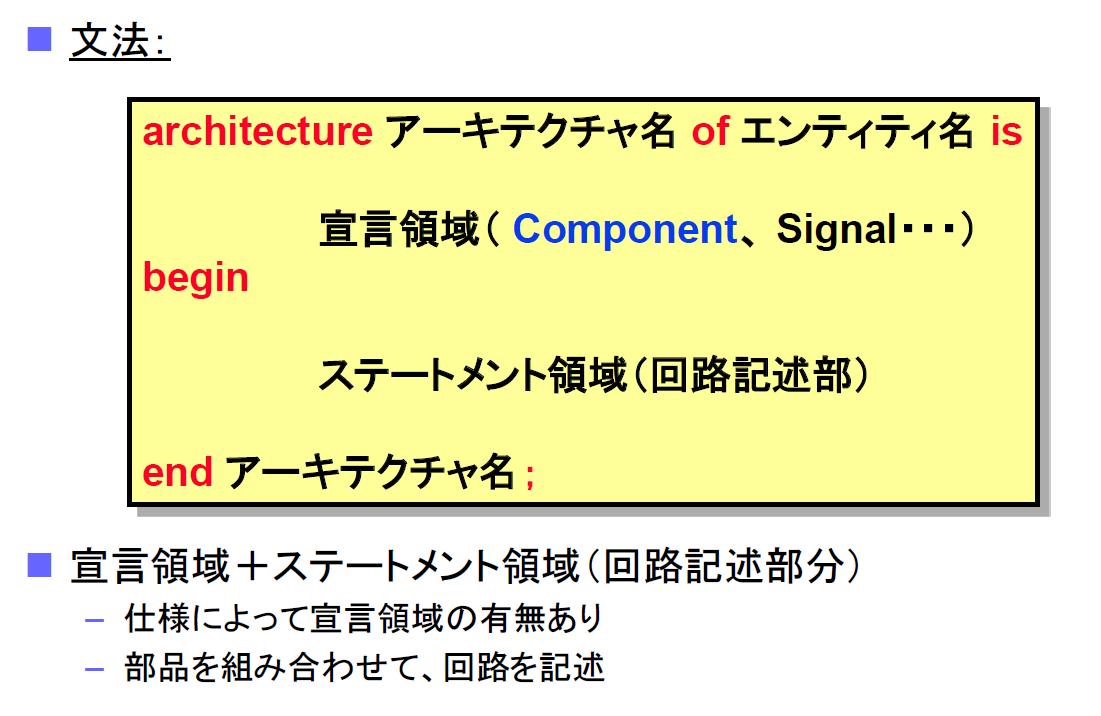

[復習] Architectureの書式

図 2-Architectureの書式

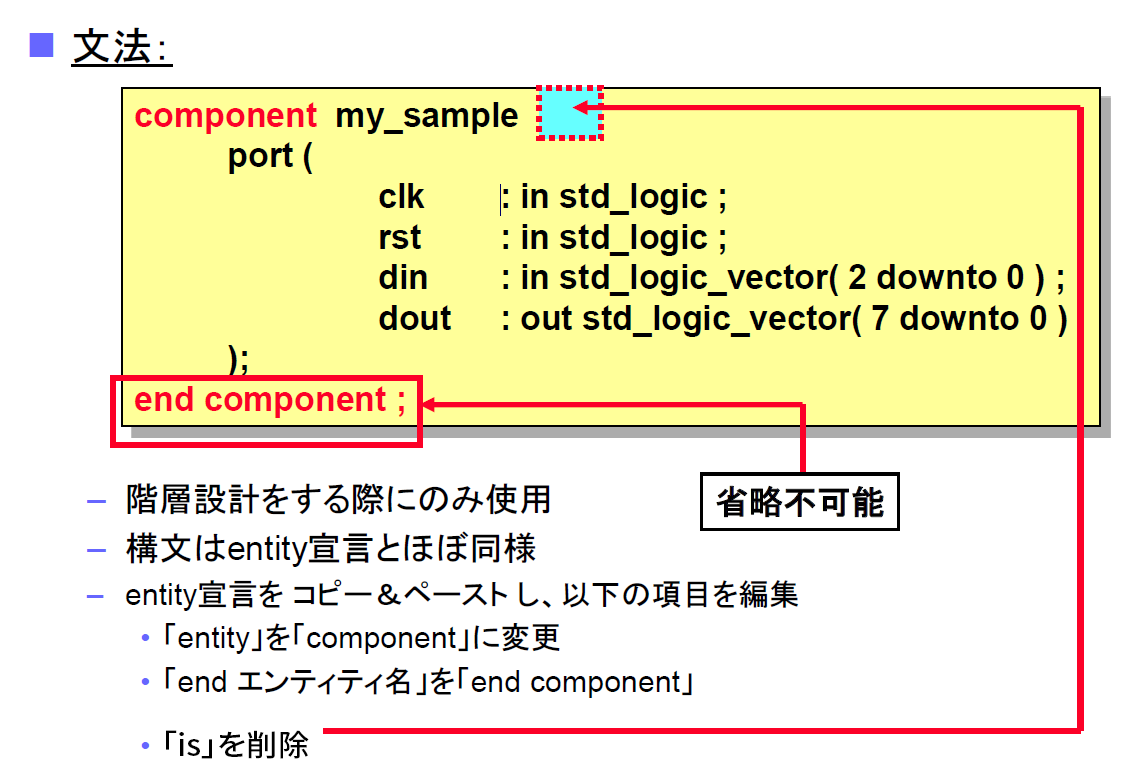

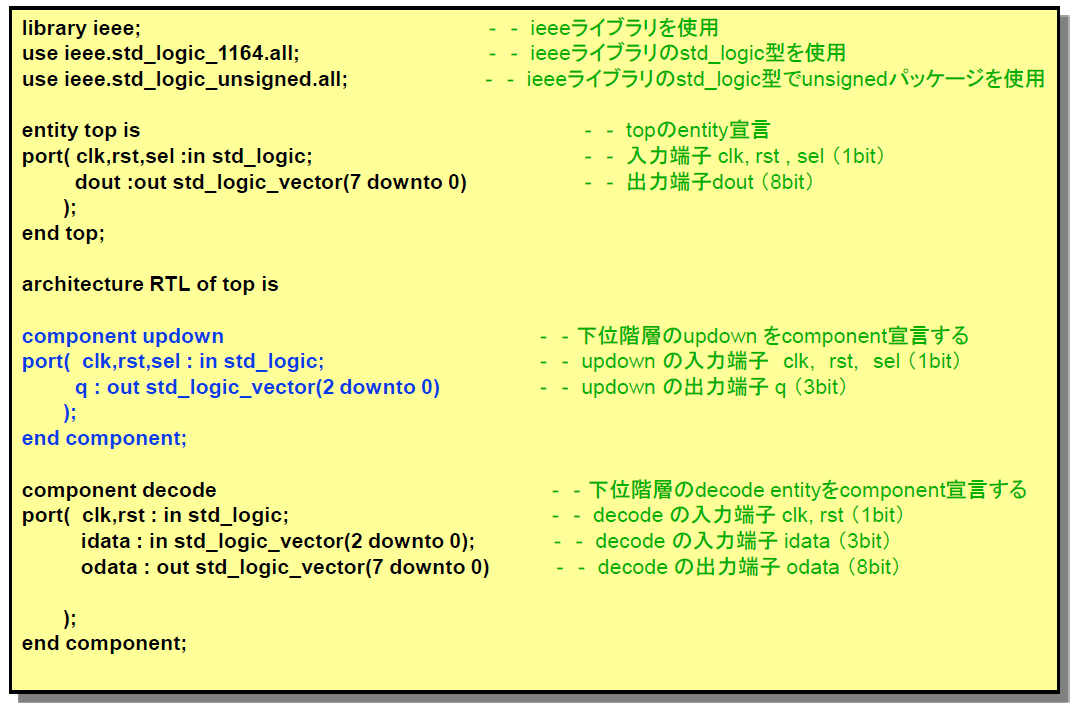

Component宣言部分

図 3-Component 宣言部分

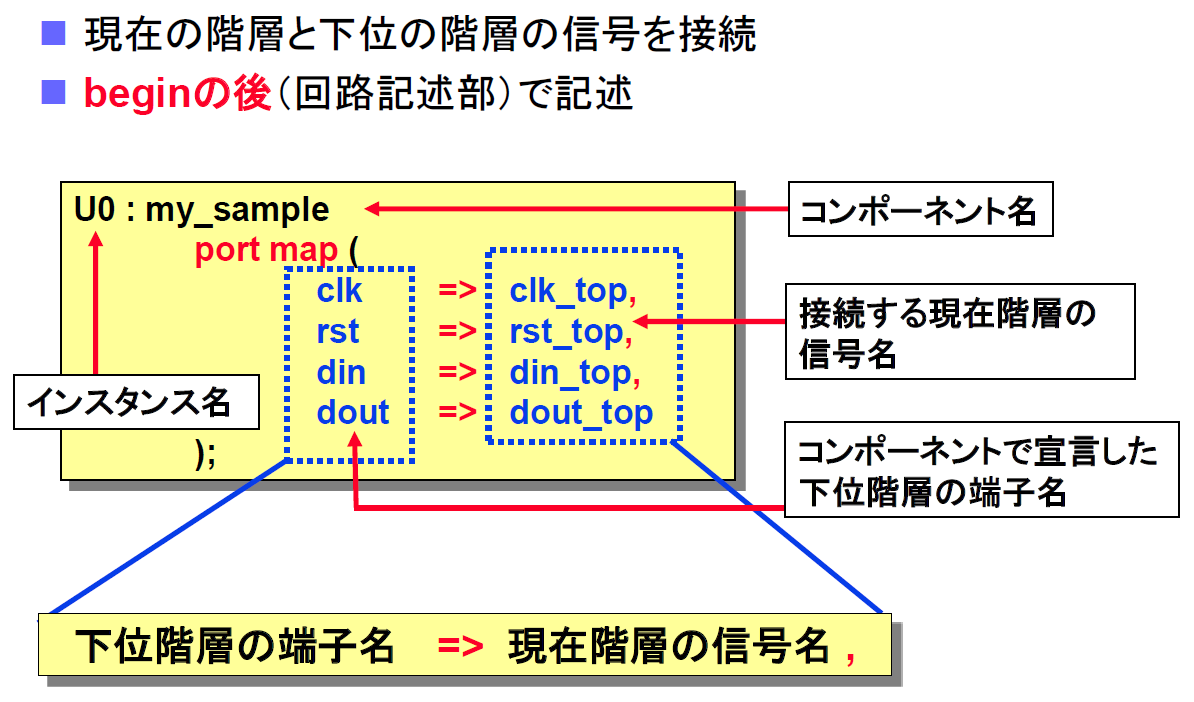

下位階層のインスタンス

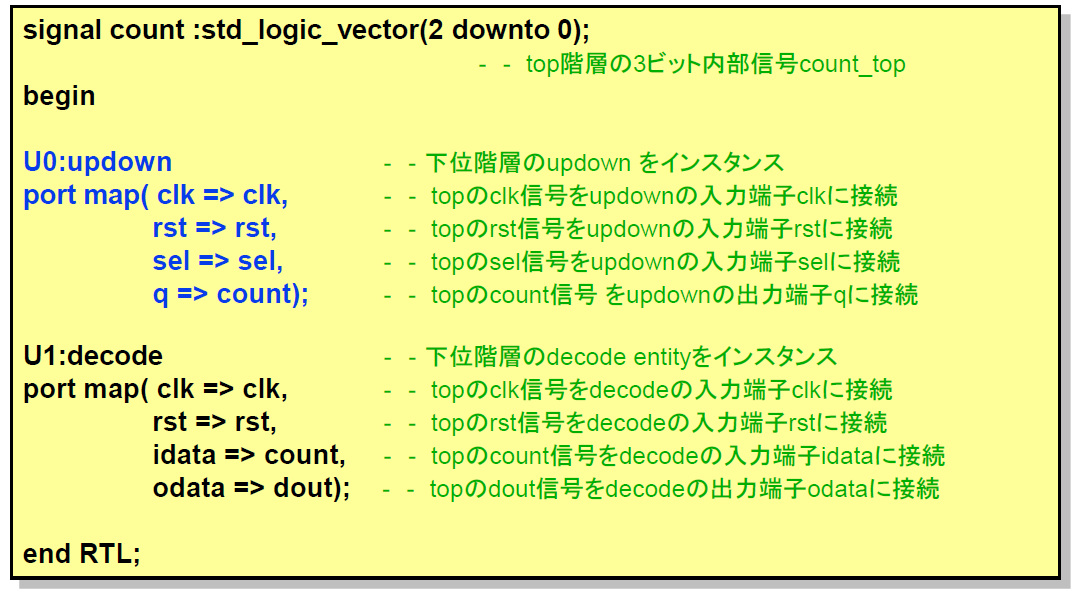

図 4-下位階層のインスタンス

課題

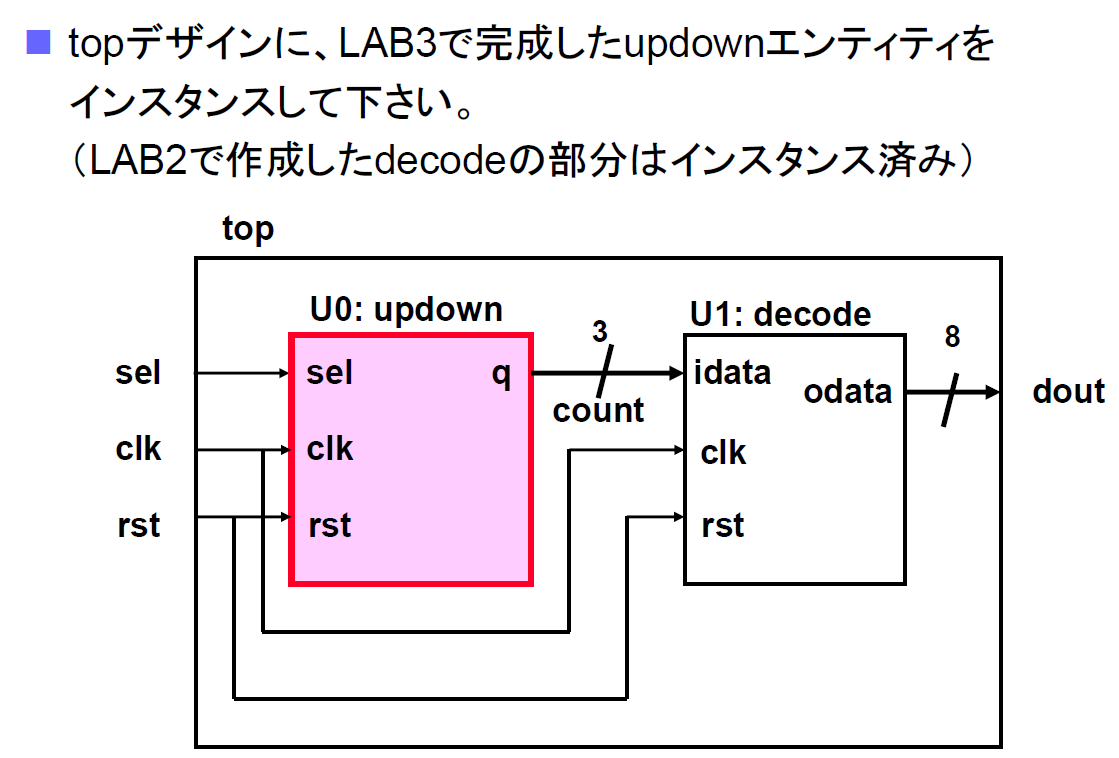

topデザインに、演習(3)で完成したupdown エンティティをインスタンスしてください。

※演習(2)で作成したdecodeの部分はインスタンス済み

図 5-下位階層のインスタンス演習ブロック

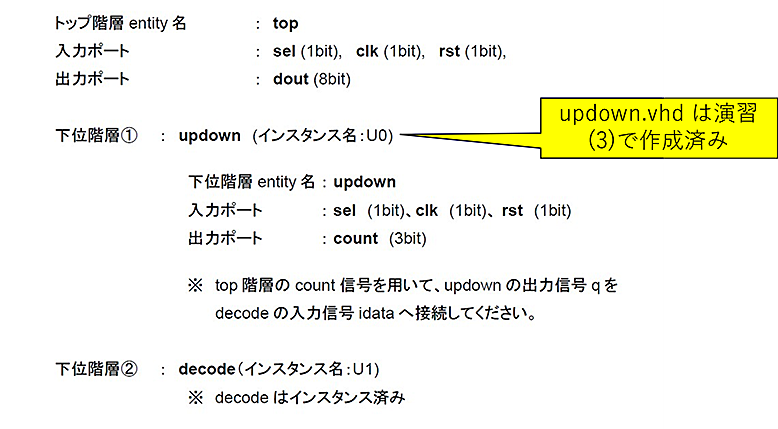

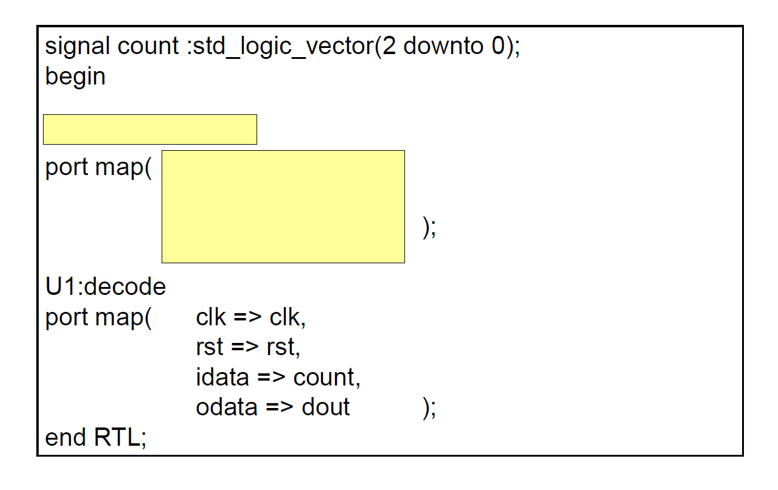

図 6-下位階層のインスタンス演習内容

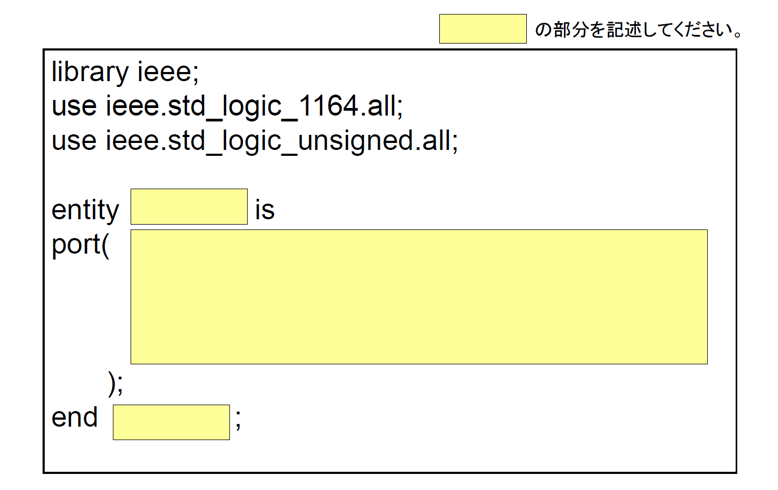

図 7-下位階層のインスタンス演習(1/3)

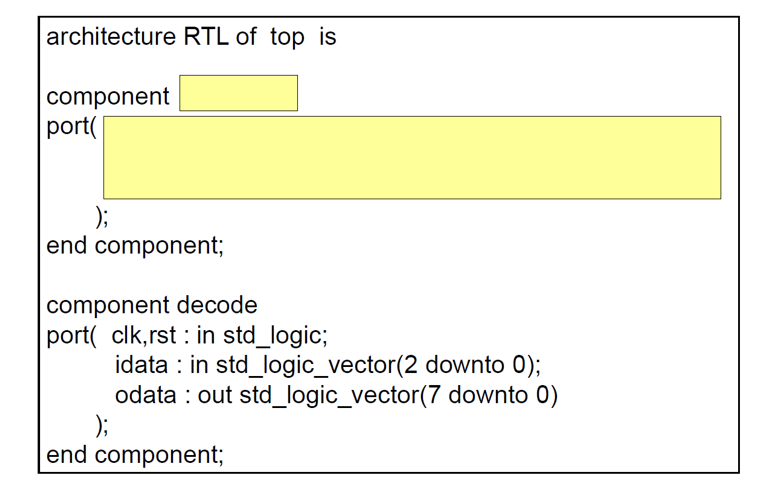

図 8-下位階層のインスタンス演習(2/3)

図 9-下位階層のインスタンス演習(3/3)

インスタンスが終了したら下記の結果を確認してください。

- Vivado®によるHDL文法チェック

- Vivado®で論理合成

- RTL Viewerにて論理合成結果の確認

複雑な回路記述例&注意点

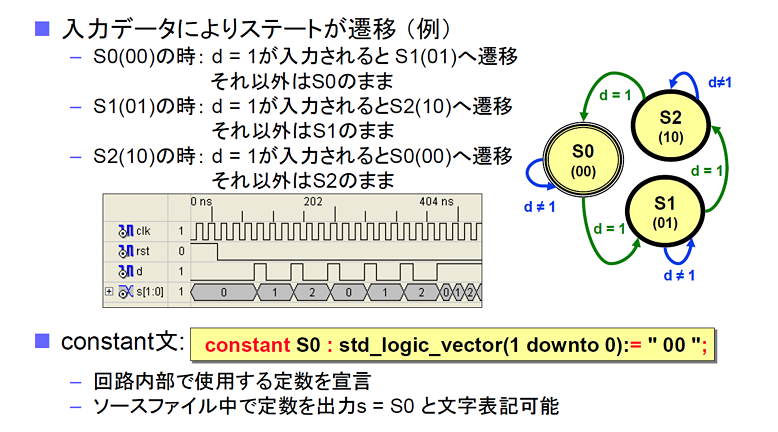

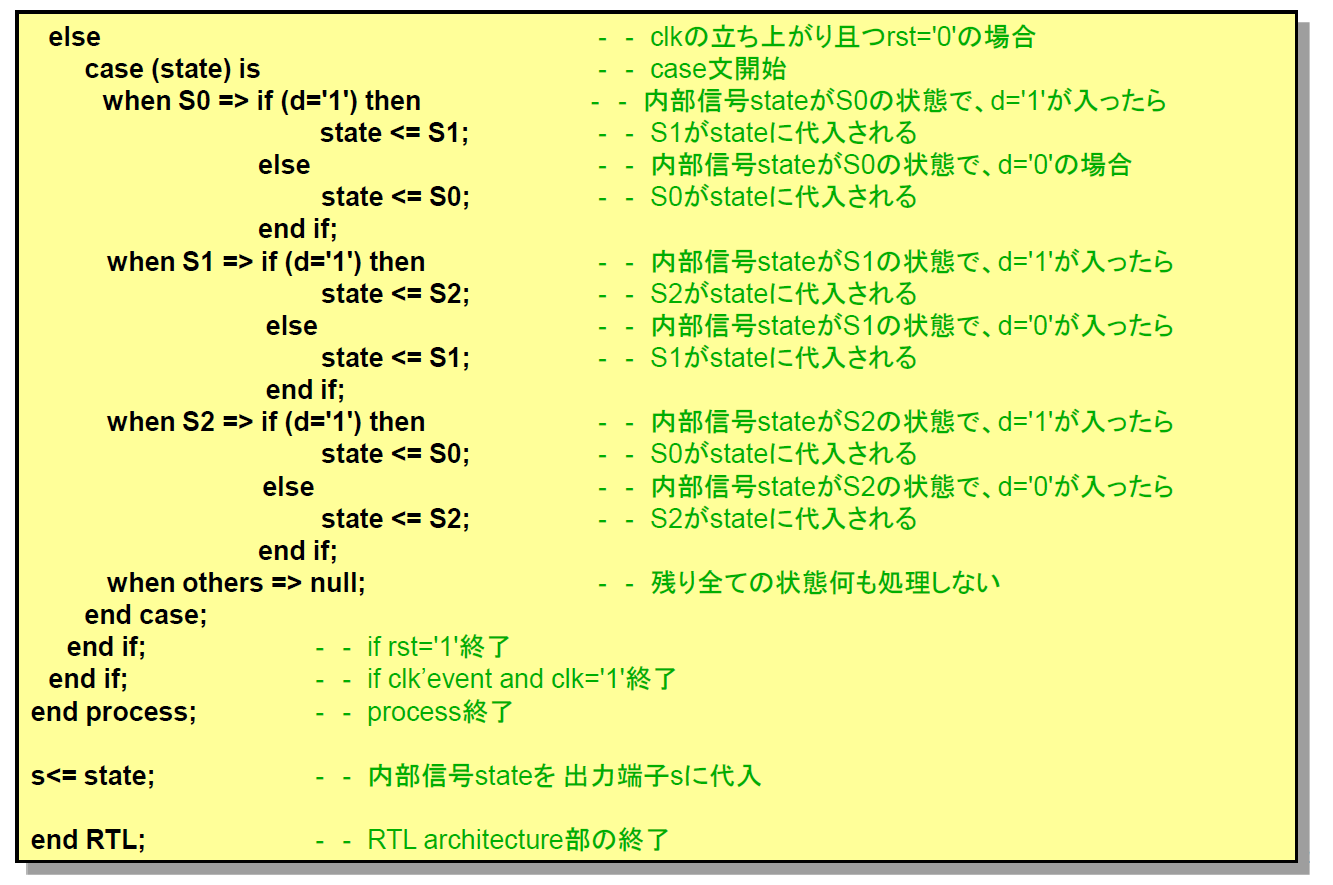

ステートマシン(状態遷移)

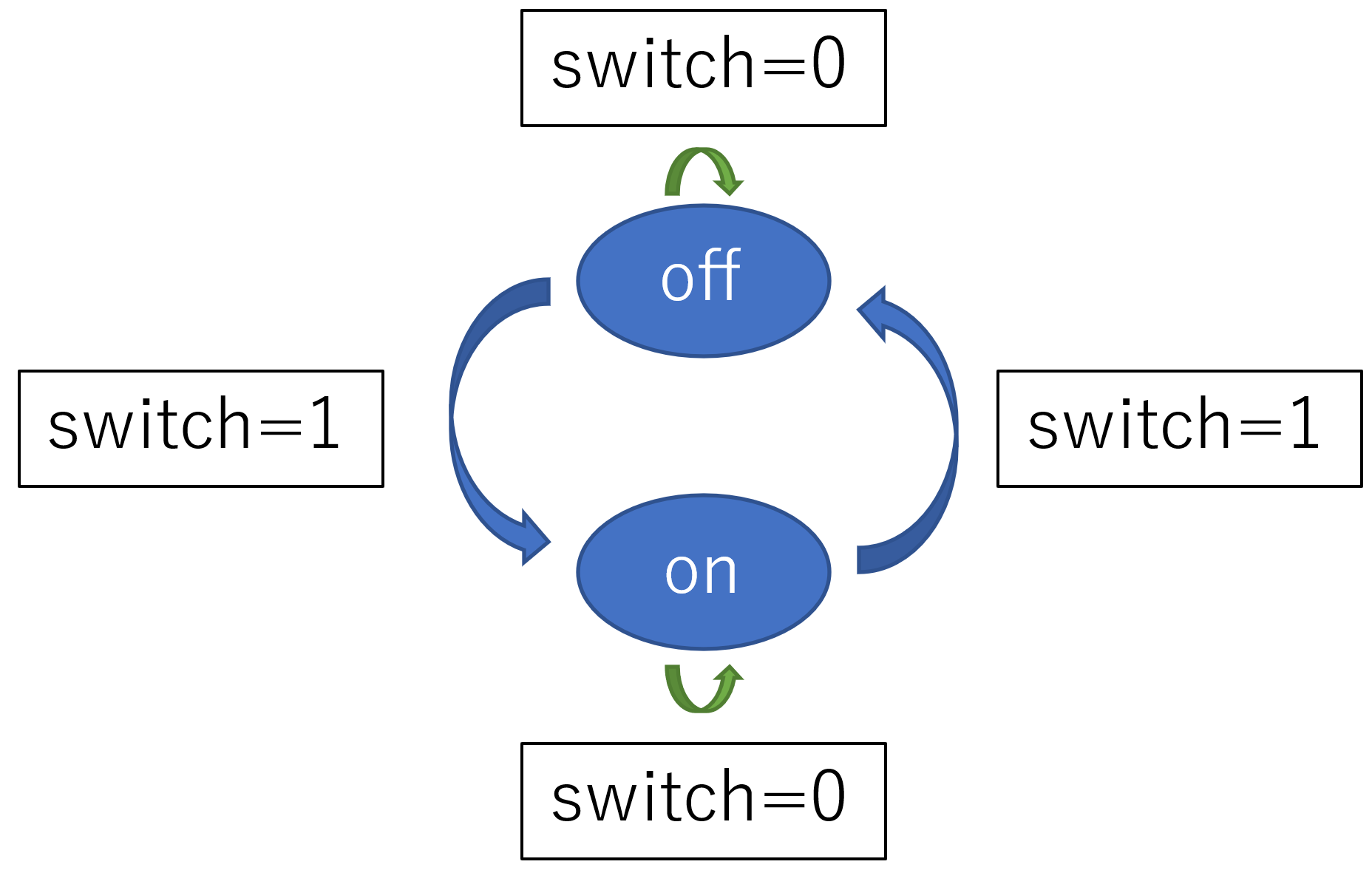

ステートマシンとは、ある状態がどう移り変わるかを考えて、図面化したものです。

例えば、プッシュ・スイッチ・ライトの場合は、「on」の状態 と「off」の状態があります。最初は、「off」の状態とします。

それから、スイッチをクリックすれば、一回「switch」の値が「1」となりまして、ライトは「on」の状態に変わります。

それからは、switchの値は「0」のままですので、「on」の状態から変わりません。

また、「on」の状態にもう一回スイッチをクリックすれば、一回「switch」の値が「1」となりまして、ライトは「off」の状態に変わります。

それからは、switchの値は「0」のままですので、「off」の状態から変わりません。

それは、下記の図みたいな形で表示されることができます。

図 10-ライトスイッチの簡単なステートマシン

ステートマシンを最初に作成してプログラムを作成すると、エラーも少なくなり、プログラムが作成しやすくなります。

図 11-ステートマシン(状態遷移)

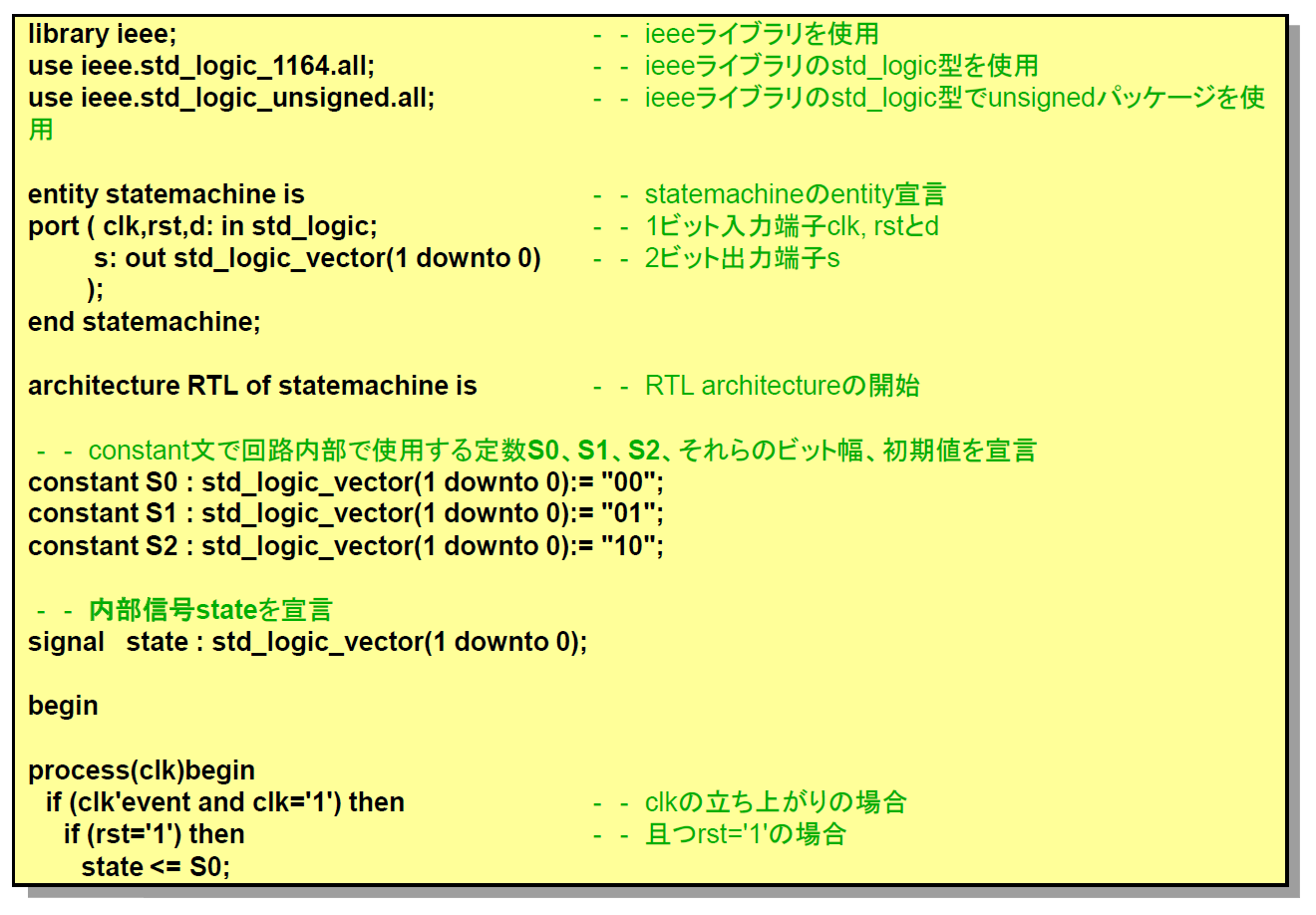

図 12-ステートマシン記述例(constant文)1/2

図 13-ステートマシン記述例(constant文)2/2

組織でコーディングする際に気を付けること

- コメント入力

> 仕様書の内容を記述する気持ちでコーディング - 可読性を考慮

> インデント、記述位置 - 書式を統一

> 名前の付け方を部署・会社単位で統一

Vivado® Design Suite の作業手順

作業手順は以下の通りです。

- 1.top.vhdファイルの作成

- 2.top.vhdファイルの追加

- 3.top.vhdファイルの完成

- 4.VHDL文法チェック

- 5.論理合成の実行

1.top.vhdファイルの作成

手順1: 演習(1)での「Vivado® Design Suite の作業手順」>「2.新規プロジェクト作成」の手順を参照して、以下のファイルを作成します。

保存場所 :C: \Home\VHDL (任意の場所を選択しても構いません)

ファイル名 :top.vhd

手順2:以下のソースコードを記入するか、コピーしてから貼り付けしてください。

library ieee; --ieeeライブラリを使用

use ieee.std_logic_1164.all; --ieeeライブラリのstd_logic型を使用

use ieee.std_logic_unsigned.all; --ieeeライブラリのstd_logic型でunsignedパッケージを使用

entity is --topのentity宣言

port( --1ビット入力端子clk, rst, sel

--8ビット出力端子dout

);

end top;

architecture RTL of top is

component --下位階層の updown をcomponent宣言する

port( --updown の1ビット入力端子 clk, rst, sel

--updown の3ビット出力端子 q

);

end component;

component decode --下位階層の decode をcomponent宣言する

port( clk,rst : in std_logic; --decode の1ビット入力端子 clk, rst

idata : in std_logic_vector(2 downto 0); --decode の1ビット入力端子 idata

odata : out std_logic_vector(7 downto 0) --decode の3ビット出力端子 odata

);

end component;

signal count :std_logic_vector(2 downto 0); --top階層の3ビット内部信号 count

begin

--下位階層のupdownをインスタンス

--updownをインスタンス名U0でインスタンスする

port map( --topの入力端子clk を updownの入力端子 clk に接続

--topの入力端子rst を updownの入力端子 rst に接続

--topの入力端子sel を updownの入力端子 sel に接続

--topのsignal信号count を updownの出力端子 q に接続

);

--下位階層のdecodeをインスタンス

U1:decode --decodeをインスタンス名U1でインスタンスする

port map(clk => clk, --topの入力端子clk を decodeの入力端子 clk に接続

rst => rst, --topの入力端子rst を decodeの入力端子 rst に接続

idata => count, --topのsignal信号count を decodeの入力端子 idata に接続

odata => dout --topの出力端子dout を decodeの出力端子 odata に接続

);

end RTL; --architecture領域終了手順3:作成したファイルを保存します。

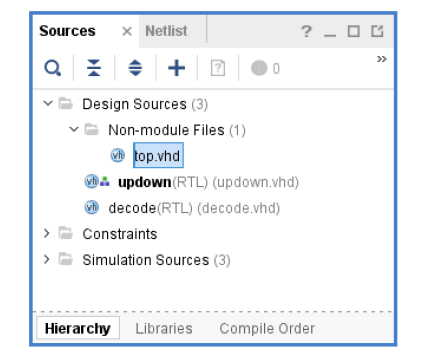

2.top.vhdファイルの追加

手順1:

演習(3)の「1.updown.vhdファイルの追加」 の手順の手順を参照して、以下のファイルをプロジェックトに追加します。

保存場所 :C: \Home\VHDL (自分で作成したファイルの保存場所)

ファイル名 :top.vhd

3.top.vhdファイルの完成

手順1:ファイルを開きます。Sourceウィンドウに表示されているtop.vhdファイルをダブルクリックします。

図 14-Sourceウィンドウ

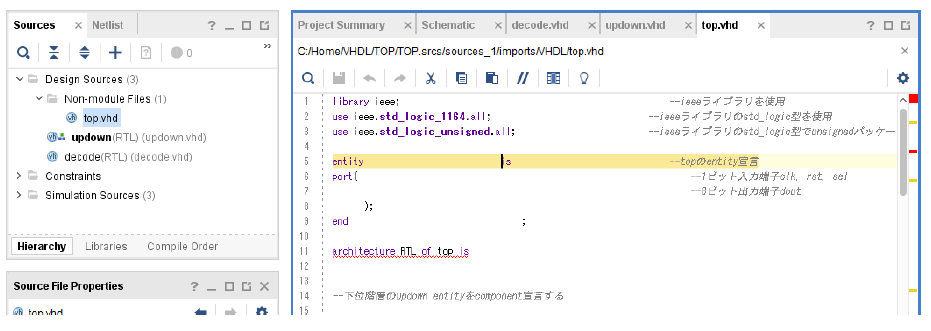

手順2:top.vhdファイルが開き、未完成の回路記述が表示されます。

図 15-テキストエディタ画面

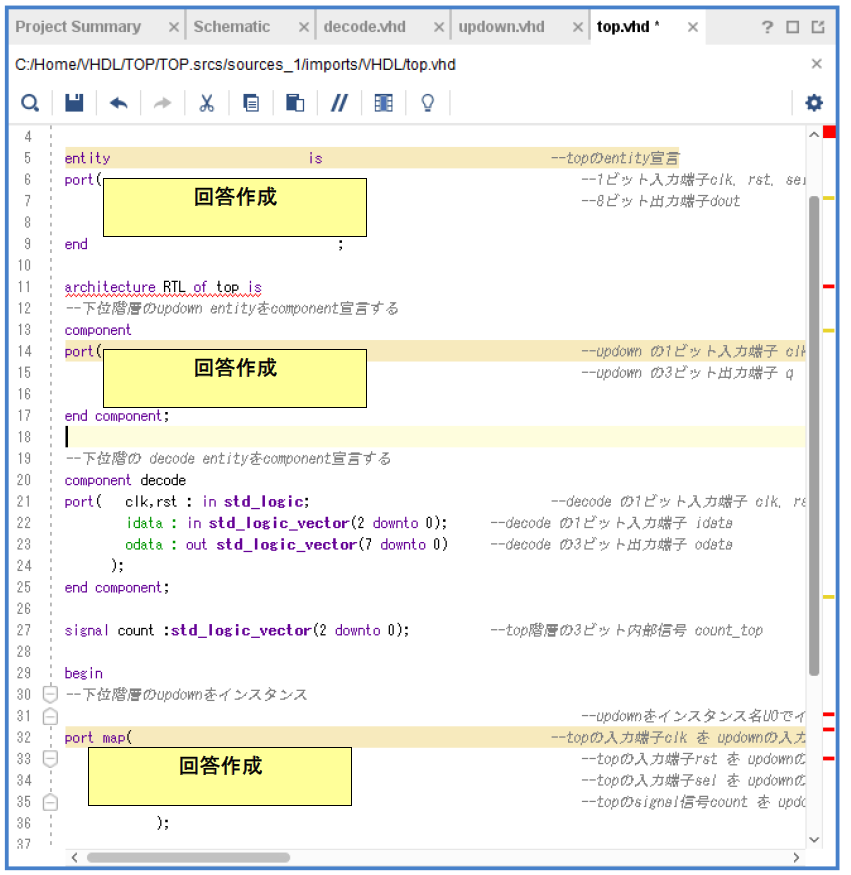

手順3:ソースコードを完成させます。

top.vhdファイル内で、topのentity とupdown.vhdのインスタンスを部分記述し、ファイルを完成させたのち、保存してください。

ファイルを保存する際、メニューバー:File-Save File Asを選択する又は“保存”ボタンをクリックしてください。

図 16-ファイルの Open

4.VHDL文法チェック

手順1:演習(2)の「VHDL文法チェック」を参照して、文法チェックOKまで実行してください。

5.論理合成の実行

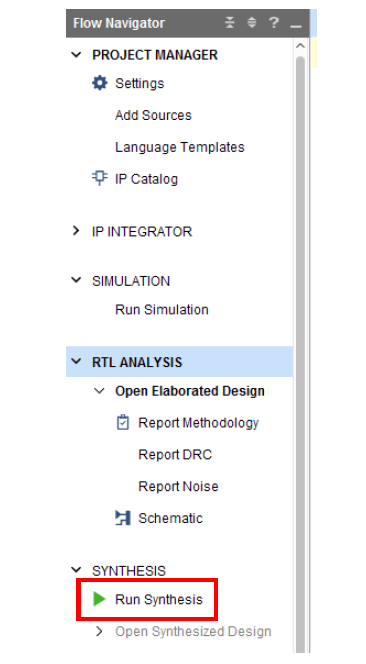

手順1:Flow Navigatorウィンドウで、Run Synthesizeを実行してください。

図 17-論理合成の実行

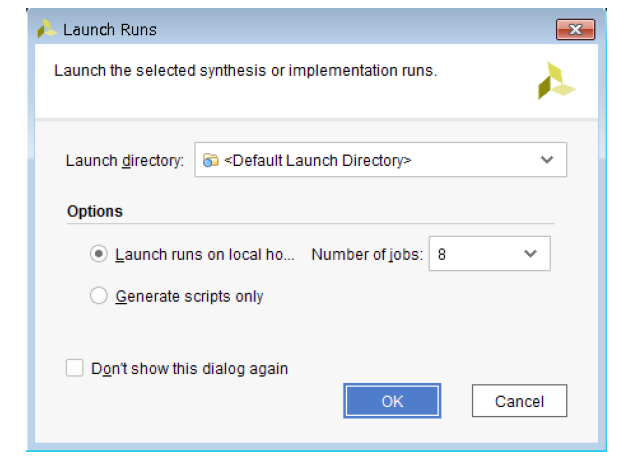

手順2:論理合成の実行ダイアログ

以下ダイアログが表示されるので、OKをクリックします。

図 18-論理合成の実行ダイアログ

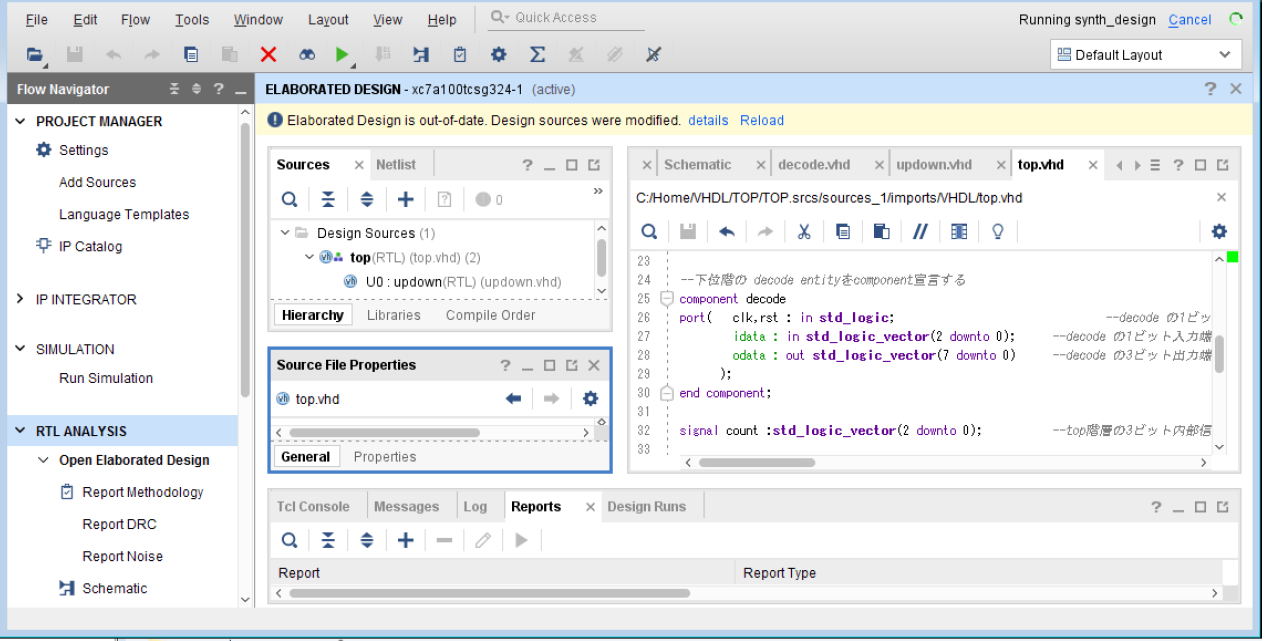

手順3:論理合成の実行待ち

Vivado® の右上の アイコン![]() が回転している時は、Synthesizeの実行中です。

が回転している時は、Synthesizeの実行中です。

図 19-Synthesize実行中の表示

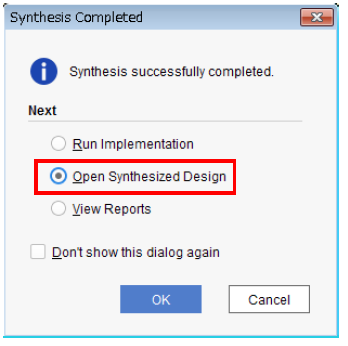

手順4:論理合成の完了ダイアログ

以下ダイアログが表示されたら、Open Synthesized Designを選択し、OKをクリックします。

図 20-論理合成の完了ダイアログ

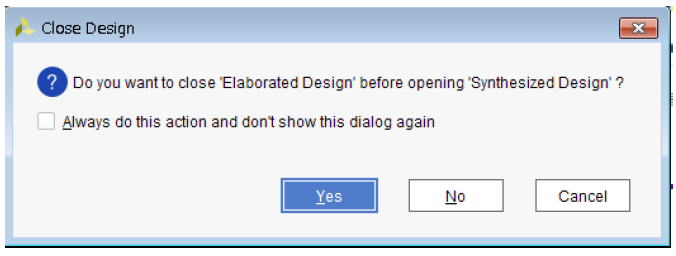

手順5:Elaborated Designを閉じるダイアログ

以下ダイアログが表示されたら、Yesをクリックします。

図 21-Elaborated Designを閉じるダイアログ

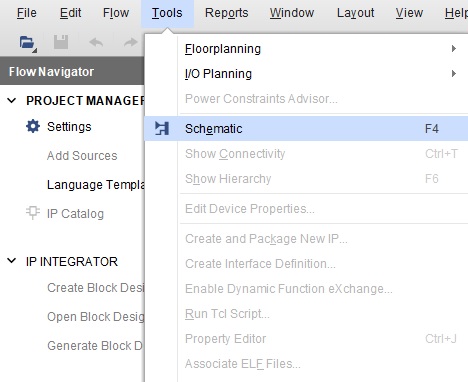

手順6:回路図の表示

メニューバーより、Tools→Schematicを選択し、回路図を表示します。

図 22-Schematicメニュー画面

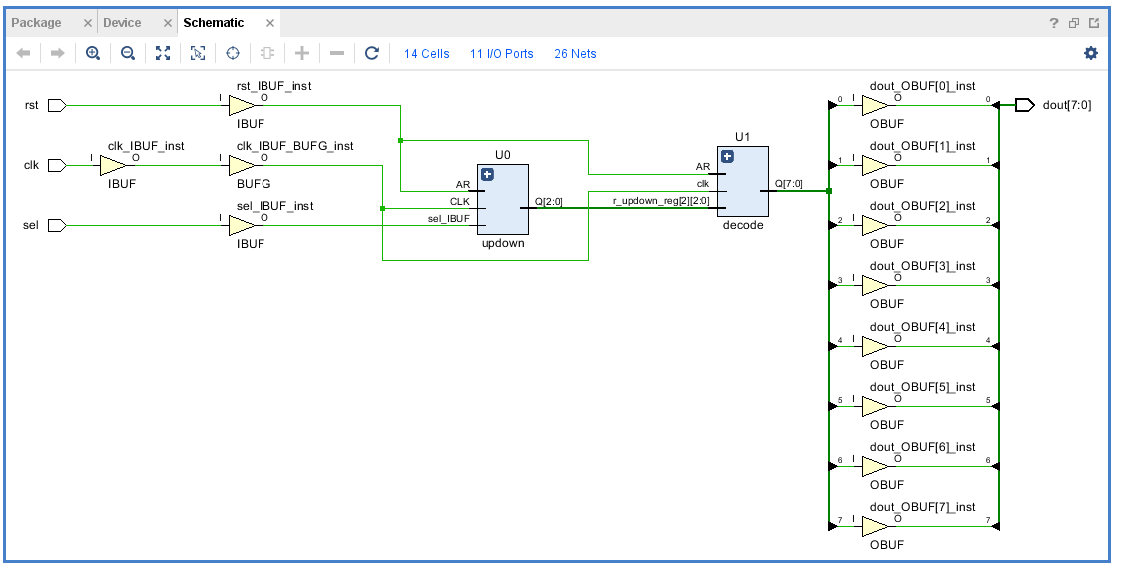

手順7:回路図の確認

updown、decodeモジュールが以下のように接続されていることを確認します。

図 23-Schematicの表示

接続されていない信号がある場合は、デザインのインスタンスや信号接続が正しく記述されていない可能性があります。デザインファイルの見直し、修正をしてください。

修正したら、手順4「VHDL文法チェック」を再度実行し直してください。

デザインの確認ができたら、Schematicウィンドウを閉じてください。

演習解答

図 24-下位階層インスタンス演習(1/2)

図 25-下位階層インスタンス演習(2/2)

作業を振り返って

階層設計は、複数の下位階層を組み合わせて設計します。同じ下位階層を複数利用できるので新しく作成することなく利用ができます。

ステートマシンについては、ある状態がどう移り変わるかを、図面化したものです。

最後までお付き合いいただきありがとうございました!

次回演習(5)は「テストベンチ作成」です。

次回も是非ご覧ください。

このブログは「FPGA設計ブログ一覧」の

1. コーディング・IP設定・プリミティブ設定 のひとつです。

これからもTECHブログを通じて、皆様の設計にお役立てできればと思います。 VHDLの使い方、設計に関する問い合わせなどありましたら、ご連絡ください。