【新人ブログ ミンガラバー】VHDL初級編 part.3 ~順序回路~

ミンガラバー(Mingalaba)!

皆さんこんにちは!シーです。

VHDL初級編もpart.3となり、少しずつ難しくなりますが、頑張って説明します!

今回は「順序回路」です。早速、始めましょう!

このブログは「FPGA設計ブログ一覧」の

1. コーディング・IP設定・プリミティブ設定 のひとつです。

目次

前回のブログの課題解答

前回 の課題解答になります。

皆様は正解できましたでしょうか?

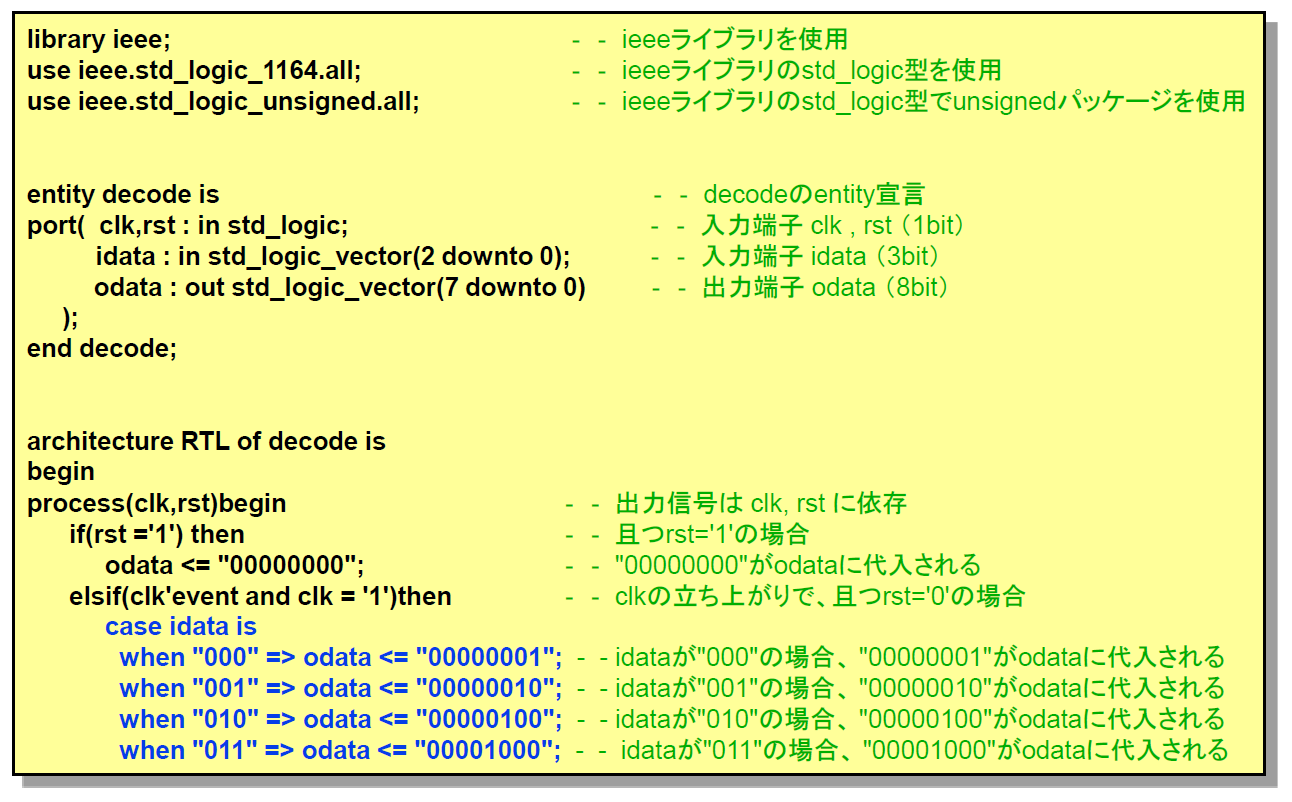

図1-前回の課題解答(組み合わせ回路演習)1/2

図2-前回の課題解答(組み合わせ回路演習)2/2

わからなかった方は、是非前回ブログ を確認してみてください。

順序回路とは

順序回路とは、現在の入力値のみならず、過去の入力値を保存して、出力を決定する論理回路です。

例えば、テレビでチャンネルを変更する時に、“up”ボタンを押すとします。

その場合、現在のチャンネルによってその次のチャンネルが変更されます。

現在のチャンネルが1なら2に変わります。順序回路はそのイメージです。

演習(3):順序回路を理解する

事前条件

今回の事前条件としては、

- 1.Vivado® Design Suite HLx Edition

- 2.Windows 10 インストール済みPC

が必要となります。

順序回路演習

クロックの記述

クロック:回路が動作するタイミングのきっかけになる信号です。

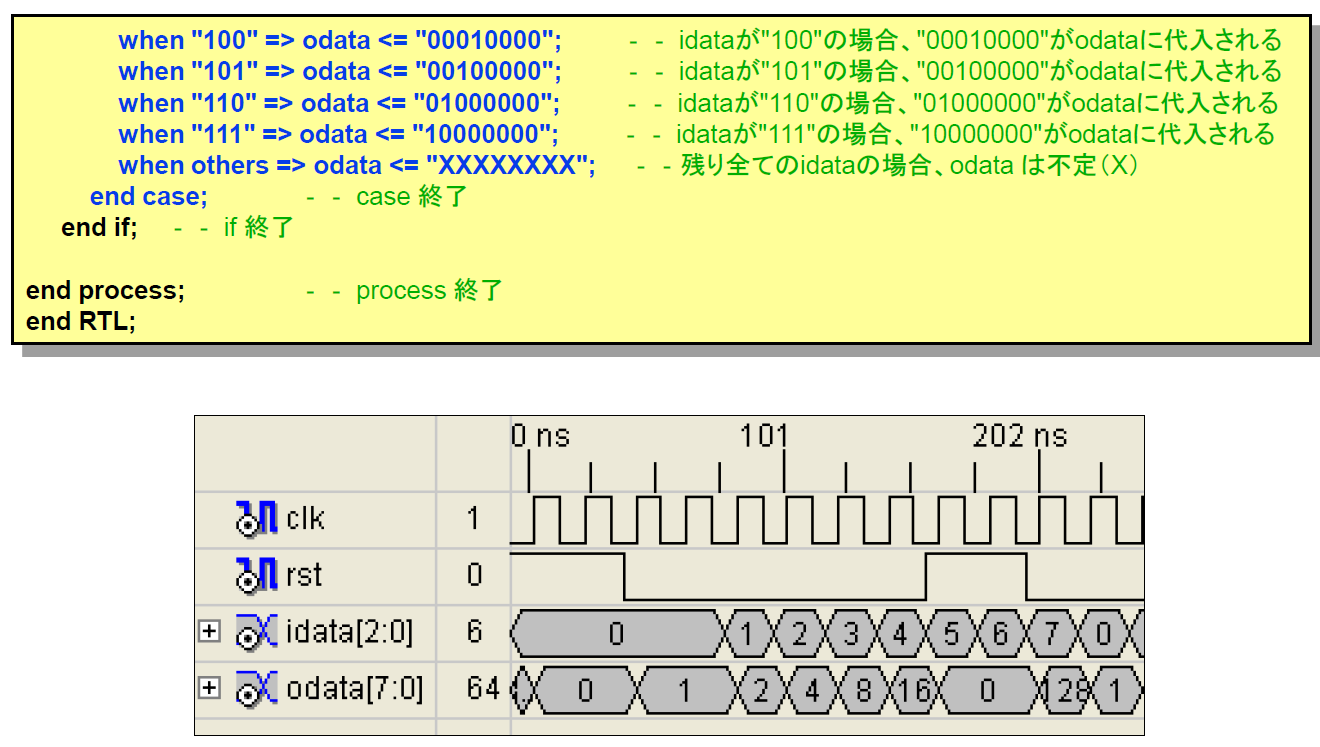

図 3-クロック信号

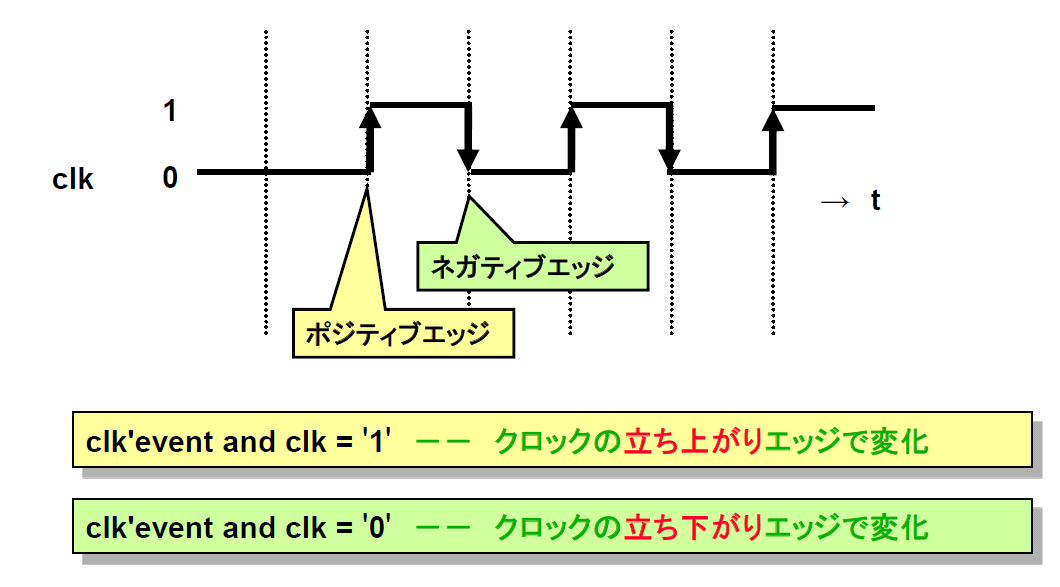

レジスタの記述方法

- process文とif文を使用してレジスタを記述します。

- process文のセンシティビティ・リストにclkが必須です。

- clk’event以下に信号名を記述することでレジスタを認識されます。

- 「if (clk’event and clk = ‘1’) then」の意味は:

- -clk’event : クロックに変更がある。

- -and: 論理の ‘and’

- -clk = ‘1’: クロックの値が ‘1’の場合。つまり、clkが立ち上がる時。

- -全体意味: “もしクロックに変更点があって、 ‘1’になると、次のコードを実行してください。”

図 4-clk記述方法

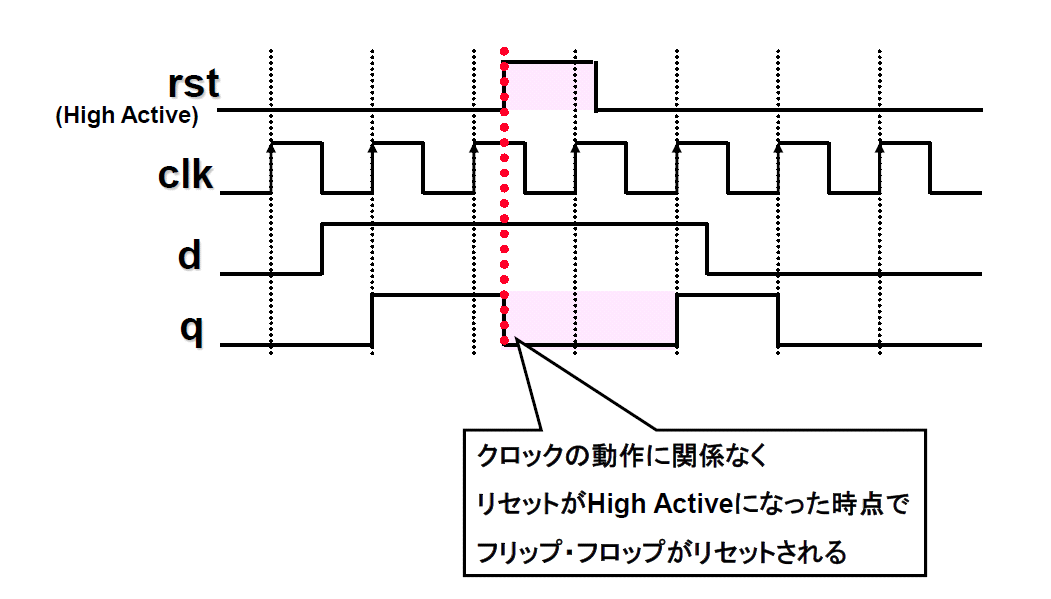

非同期リセット付きDFF

非同期とは

- クロックと関係なく、リセットがHigh Activeになった時点で反映

- DFF : D-flip flop(Delay flip flop)、FPGAの中に主に使われるデバイスです。

図 5-非同期リセット

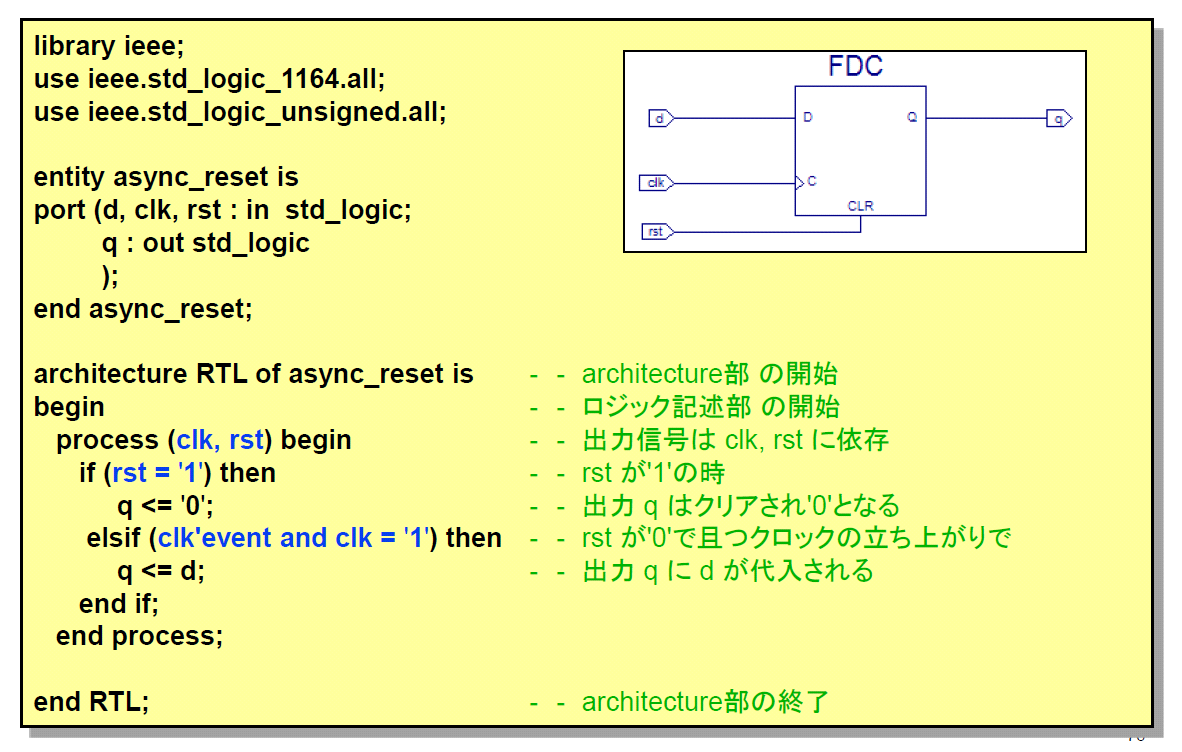

図 6-非同期リセット付きDFFのコード

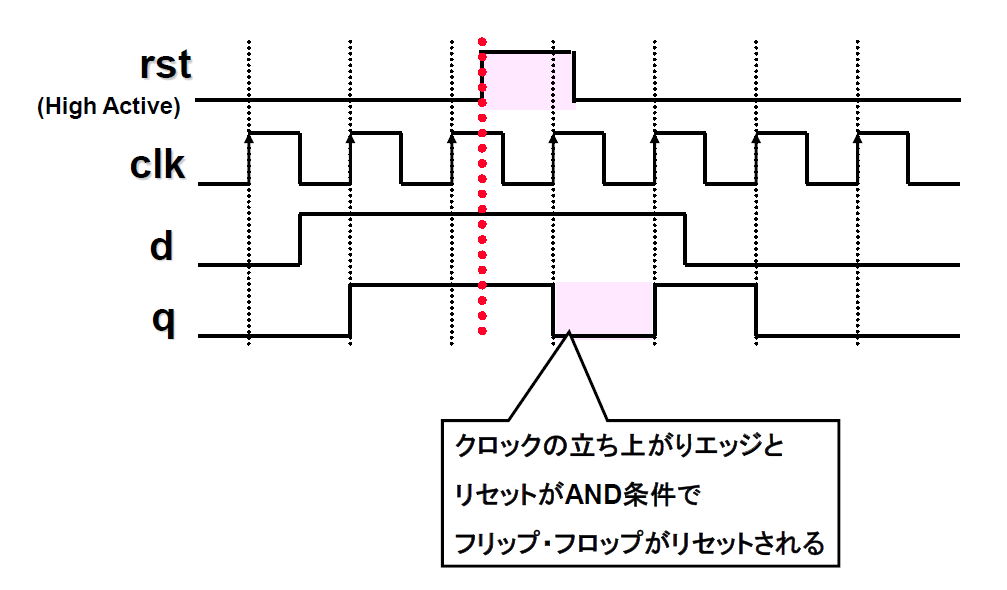

同期リセット付きDFF

同期とは

- クロックの立ち上がりエッジでリセットが反映します。

- つまり、リセットが ‘1’になっても、クロックの立ち上がりエッジではないと、動作しません。

- クロックが ‘1’の状態ではありません。クロックが ‘0’から ‘1’に”変更される時点”です。

※順序回路はこの時に利用されます。

clkの前の入力、 ‘0’を保存して、今の入力は ‘1’になると “期待の変更点だよ“って伝えます。

図 7-同期リセット

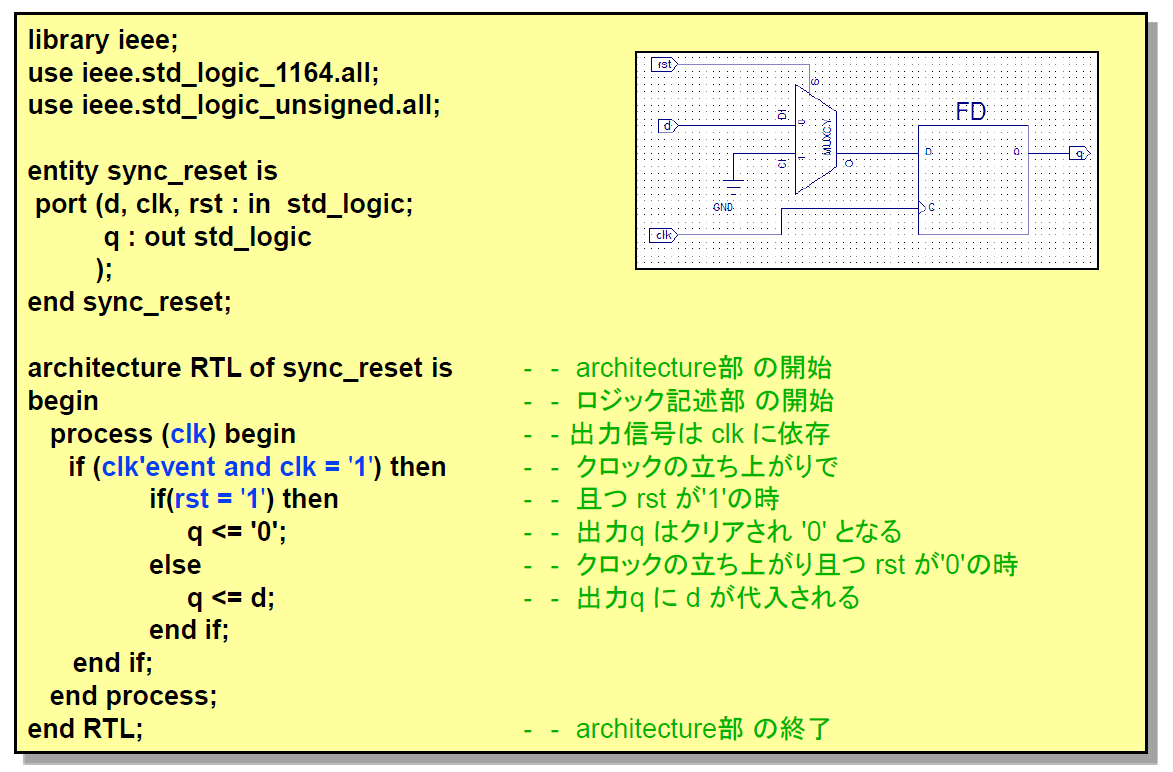

図 8-同期リセット付きDFFのコード

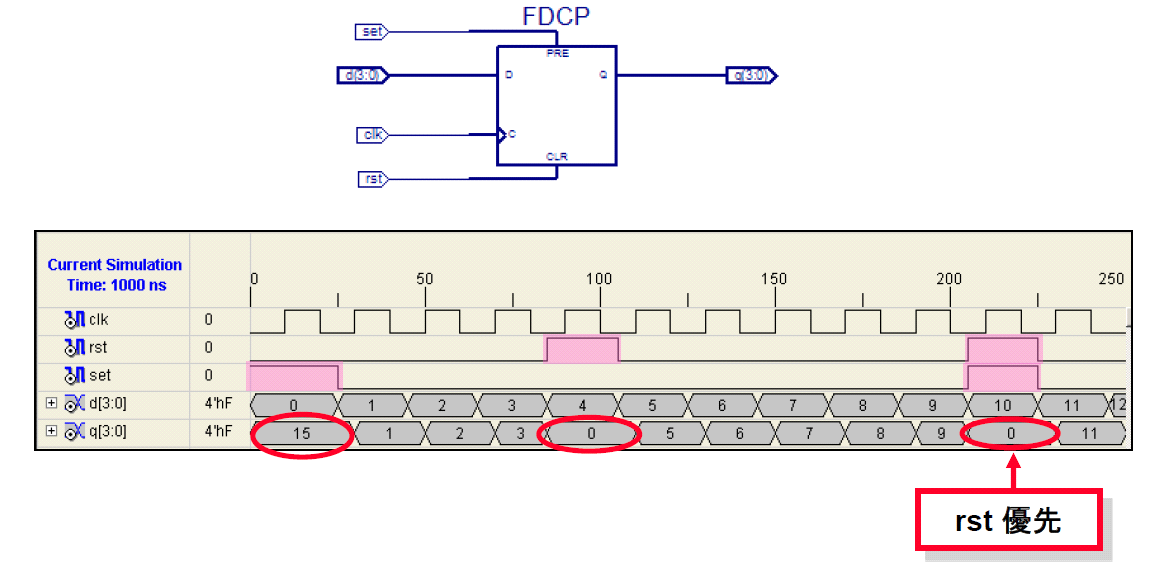

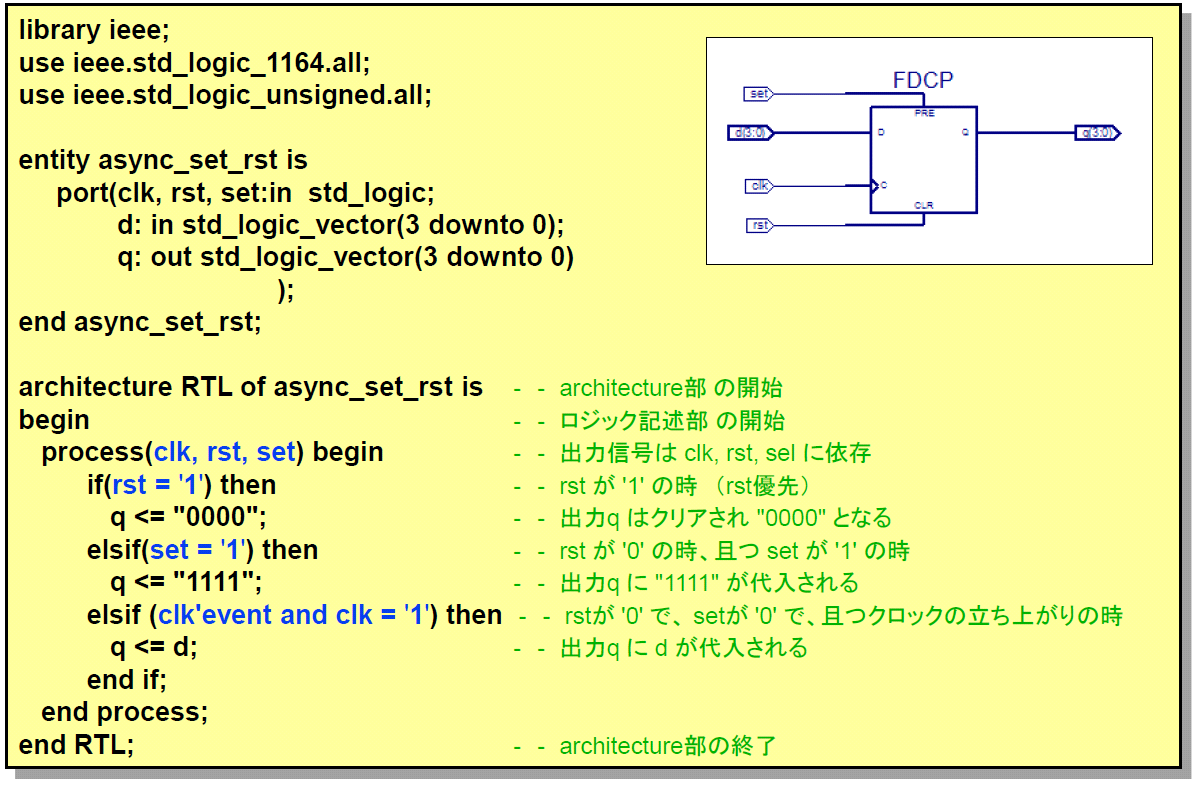

非同期セット&非同期リセット付きDFF

if文の記述順により、優先順位が決定します。

例:非同期セット/非同期リセットが同時にアクティブになった場合、 リセットを優先するようなプライオリティがあります。

図 9-非同期セット&非同期リセット付きDFF

図 10-非同期セット&非同期リセット付きDFF

順序回路記述例①

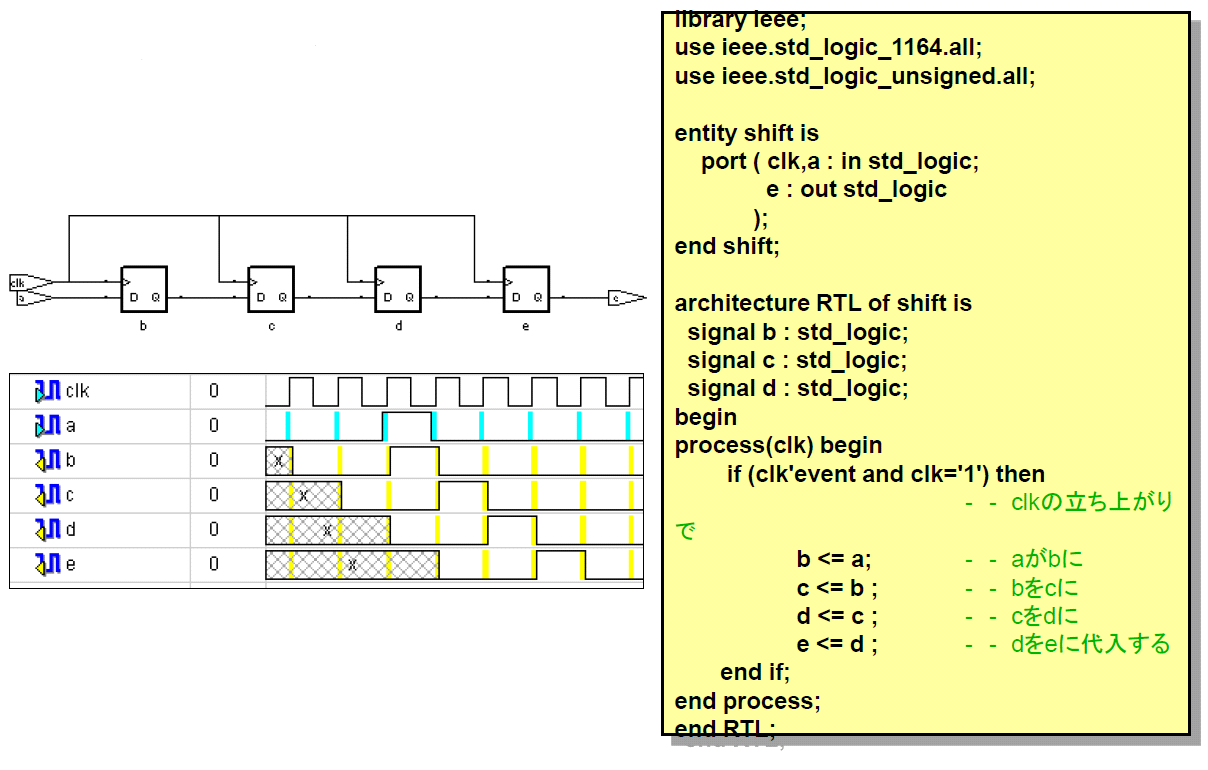

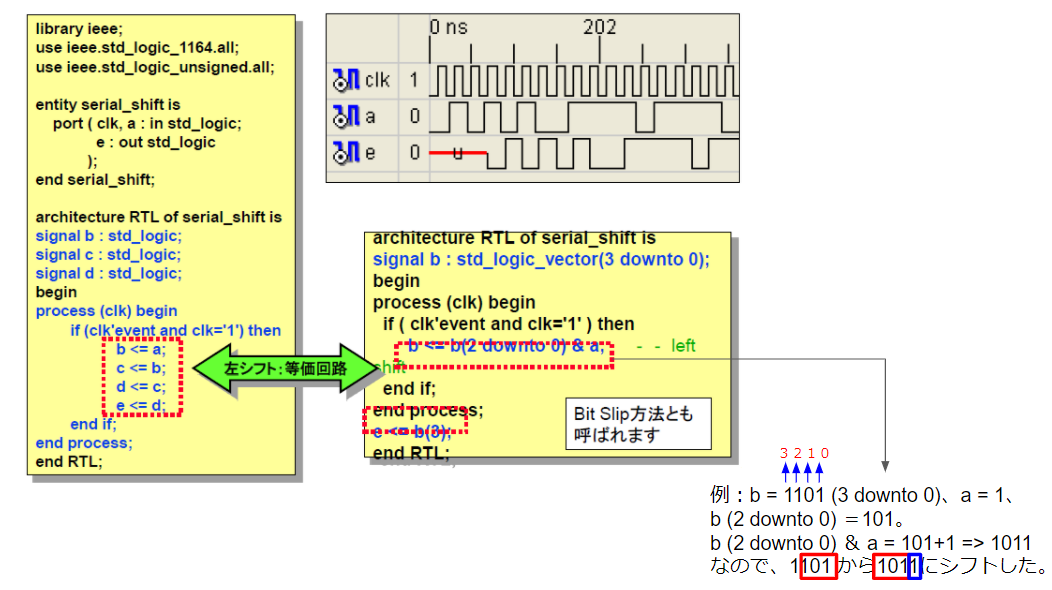

シフトレジスタ

- データを1クロック毎に移動させる回路です。

図11 -順序回路記述例①

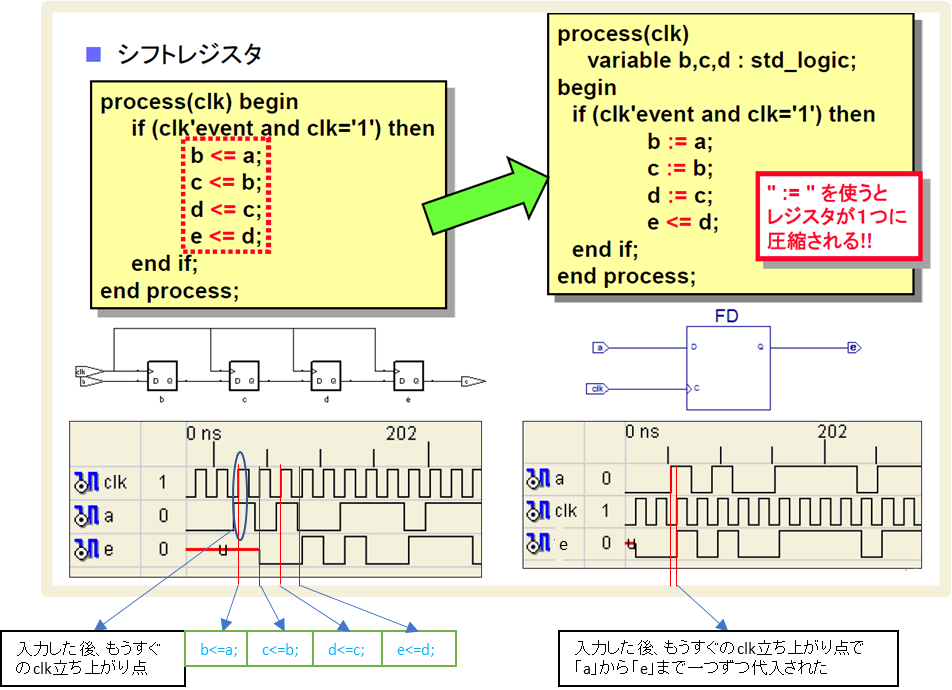

シフトレジスタ記述時の注意点

シフトレジスタ

図12 -シフトレジスタ記述時の注意点

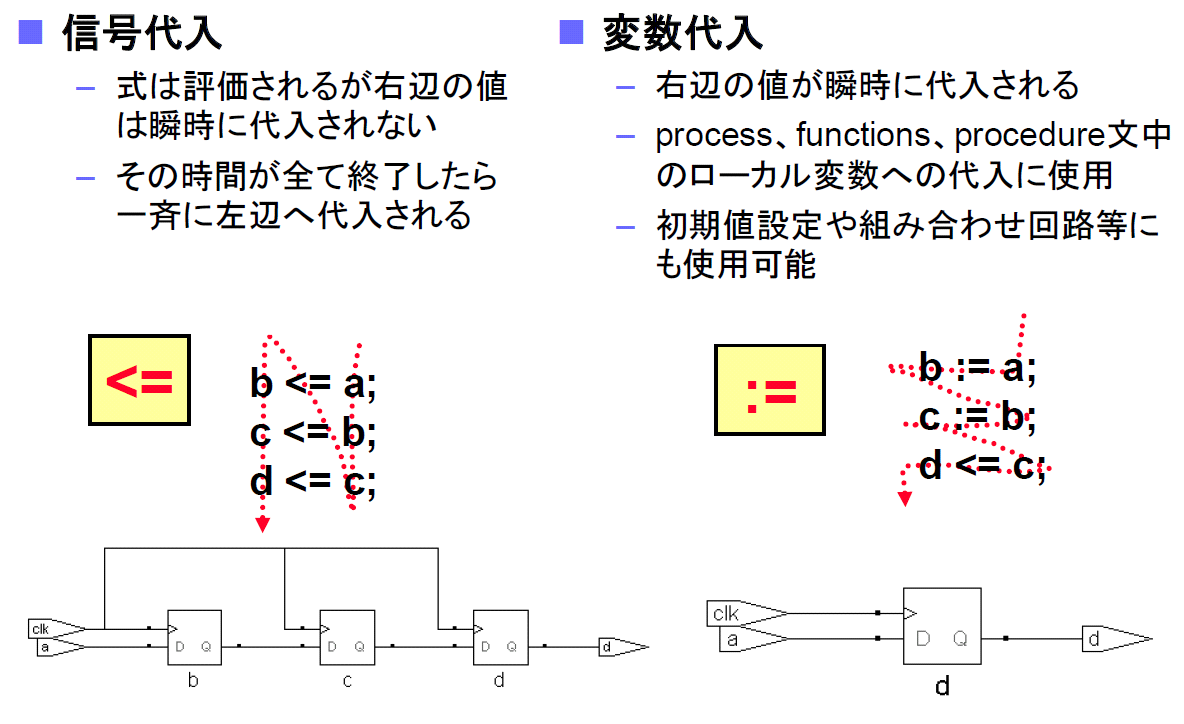

信号代入と変数代入

図13 -信号代入と変数代入

順序回路記述例②

図14 -順序回路記述例②

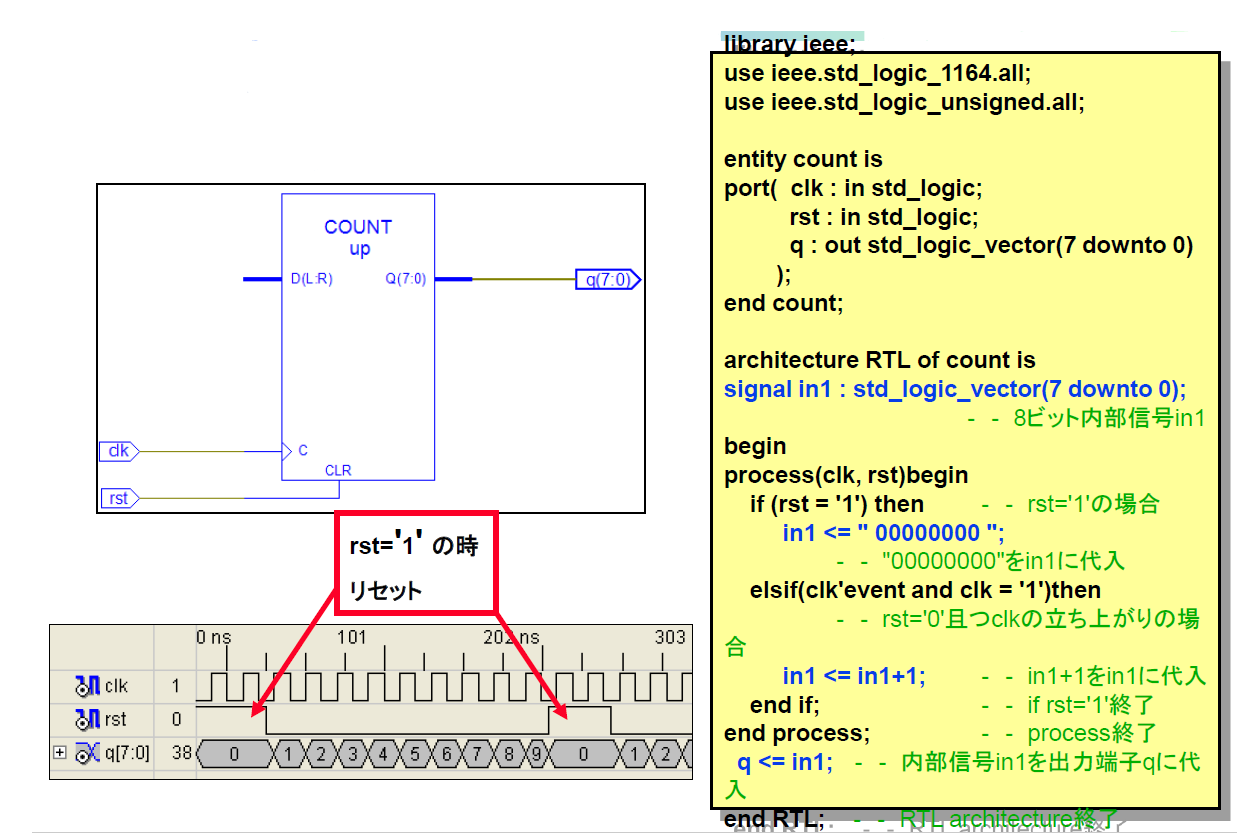

順序回路記述例③

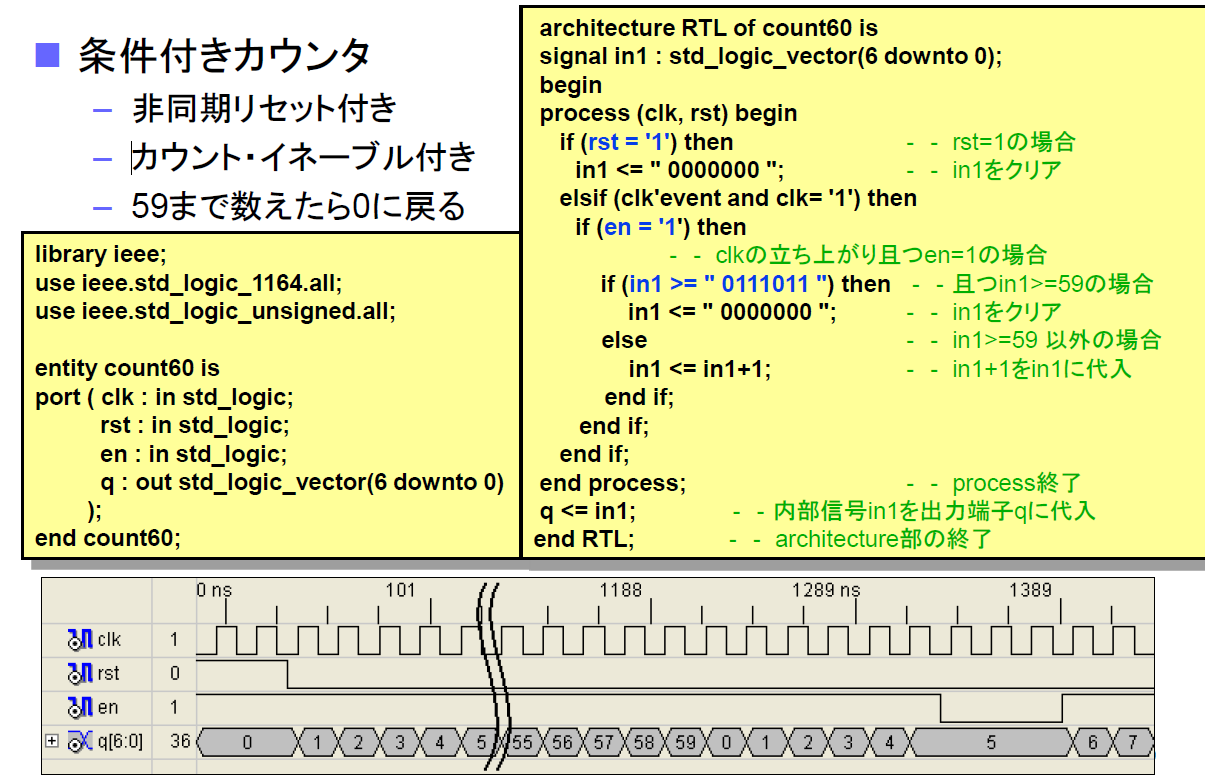

カウンタ

- 数を数えるものです。

図15 -順序回路記述例③

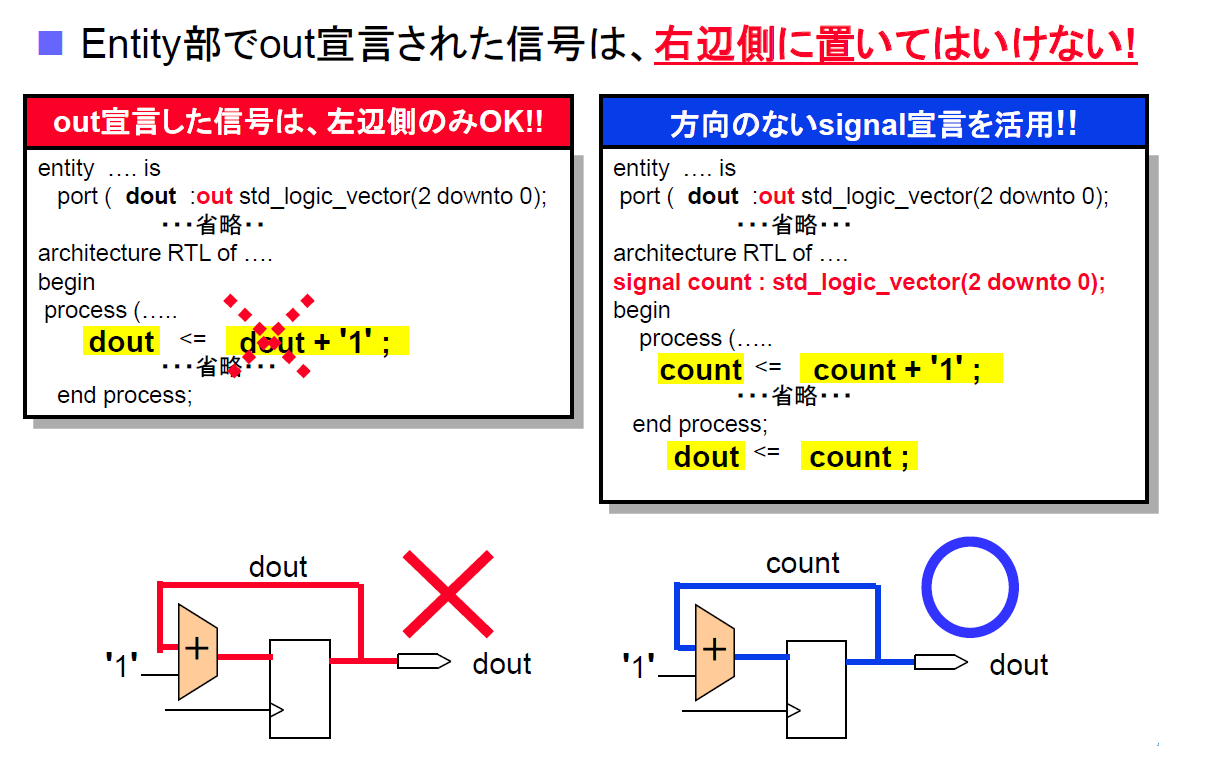

カウンタ記述時の注意事項

図16 -カウンタ記述時の注意事項

順序回路記述例④

図17 -順序回路記述例④

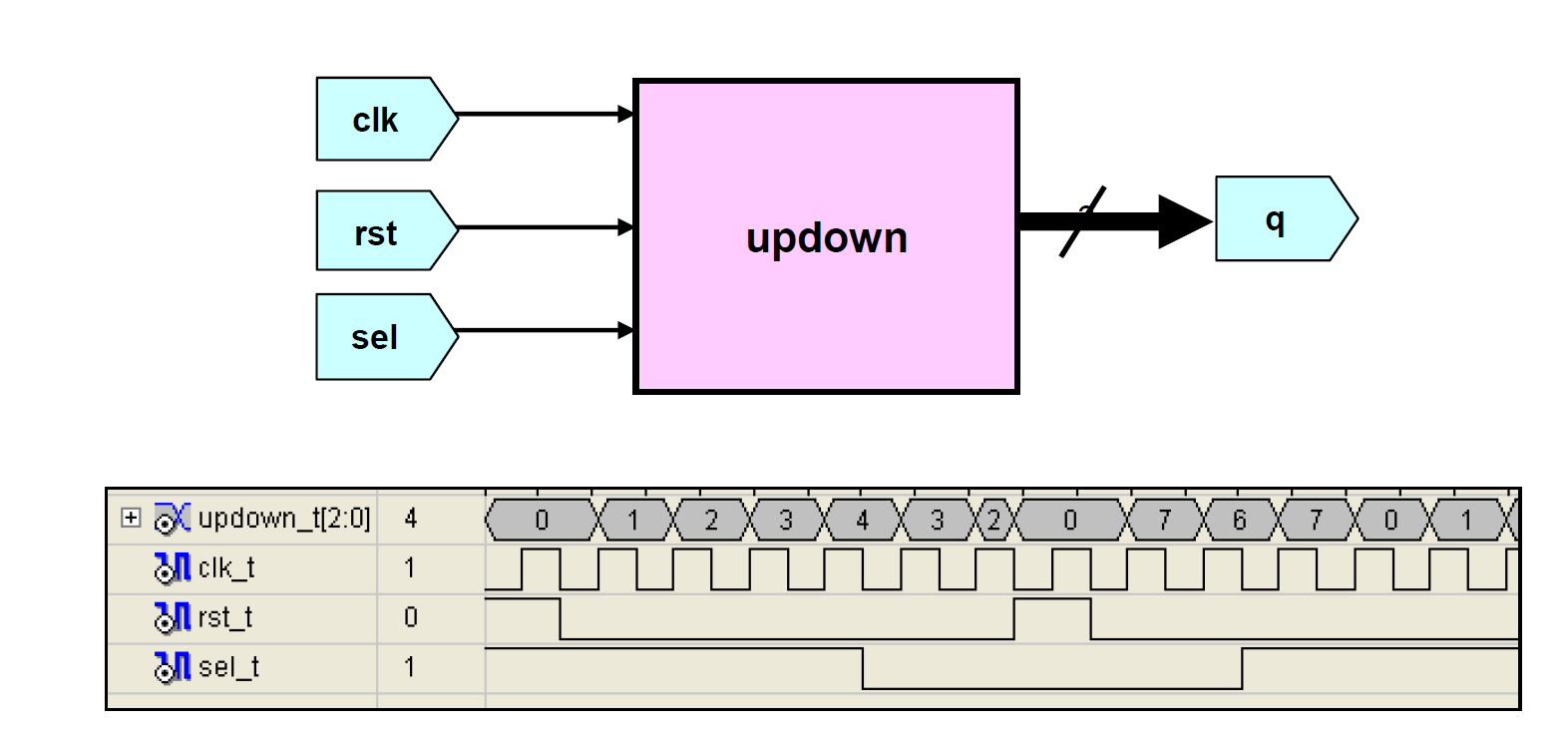

課題

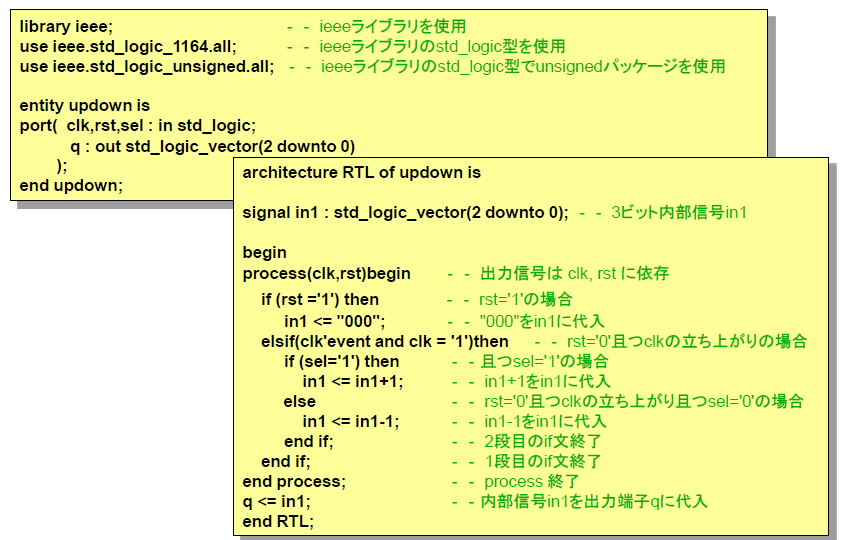

下記仕様の3ビットアップダウンカウンタを作成してください。

| entity名 | : | updown |

| 入力 | : | clk, rst, sel |

| 出力 | : | q(3bit) |

| 内部信号 | : | in1 (3bit) |

- rst = 1:カウンタを0クリア

※注意:rst は非同期信号 - sel = 1:カウントアップ / sel = 0:カウントダウン

※注意:selは同期信号

図18 -順序回路演習

Vivado® Design Suite の作業手順

作業手順は以下の通りです。

- updown.vhd ファイルの追加

- updown.vhd ファイルの完成

- VHDL文法チェック

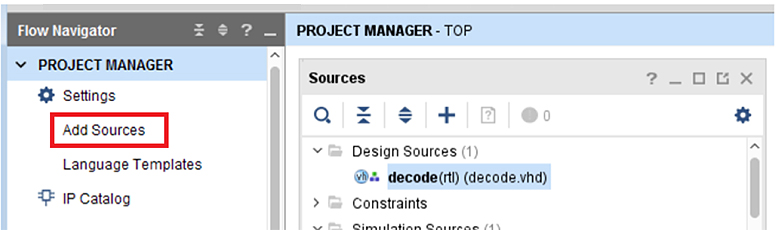

1.updown.vhdファイルの追加

手順1:Add Source をクリックします。

図19 -ファイルの追加

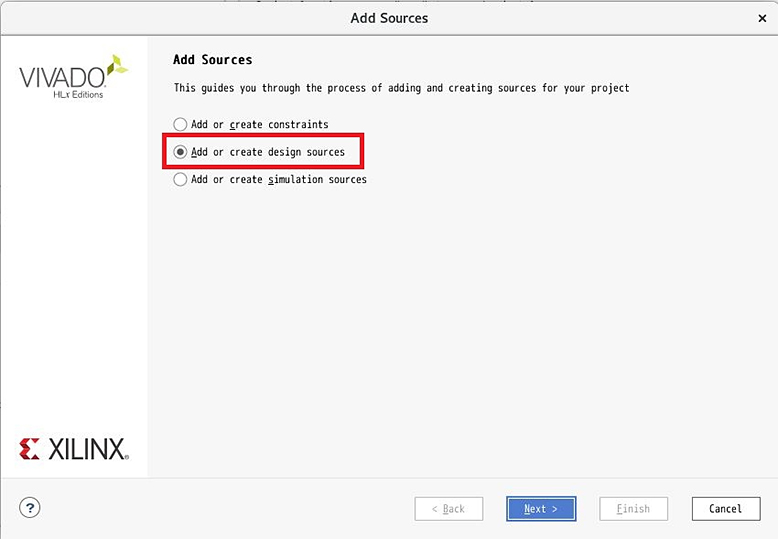

手順2:Add Source ダイアログが開きます。

以下を選択して、Nextをクリックします。

図20 -ファイルの追加ダイアログ

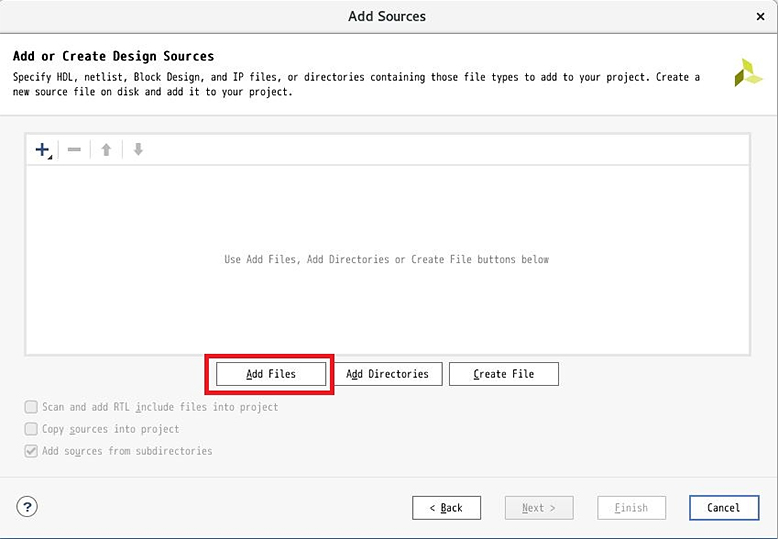

手順3:追加するファイルを指定するダイアログが表示されます。

Add Files をクリックします。

図21 -追加ファイル指定ダイアログ

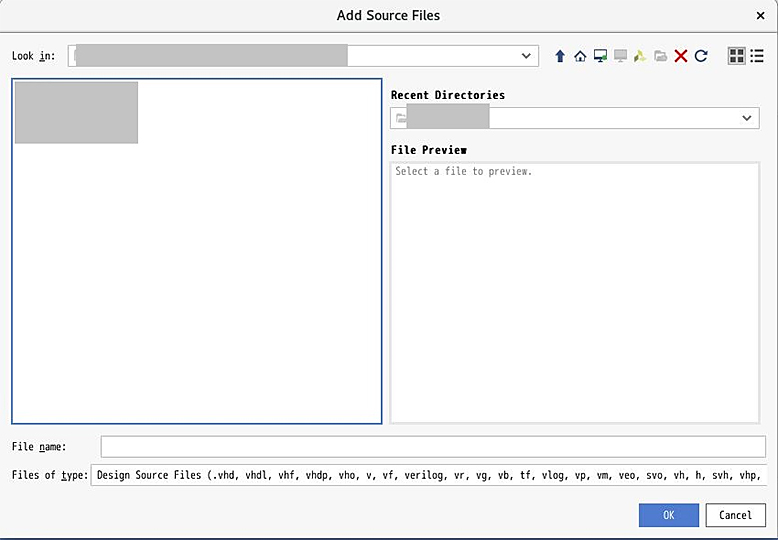

手順4:ファイルを選択するダイアログが開きます。

以下ファイルを選択して、OKをクリックします。

フォルダ:C:\Home\VHDL(自分で作成した場所)

ファイル:updown.vhd

※上記ファイルが表示されない場合は、選択されているフォルダ位置を確認してください。

図22 -ファイル選択ダイアログ

手順5:ファイルが追加されたら、Finishをクリックします。

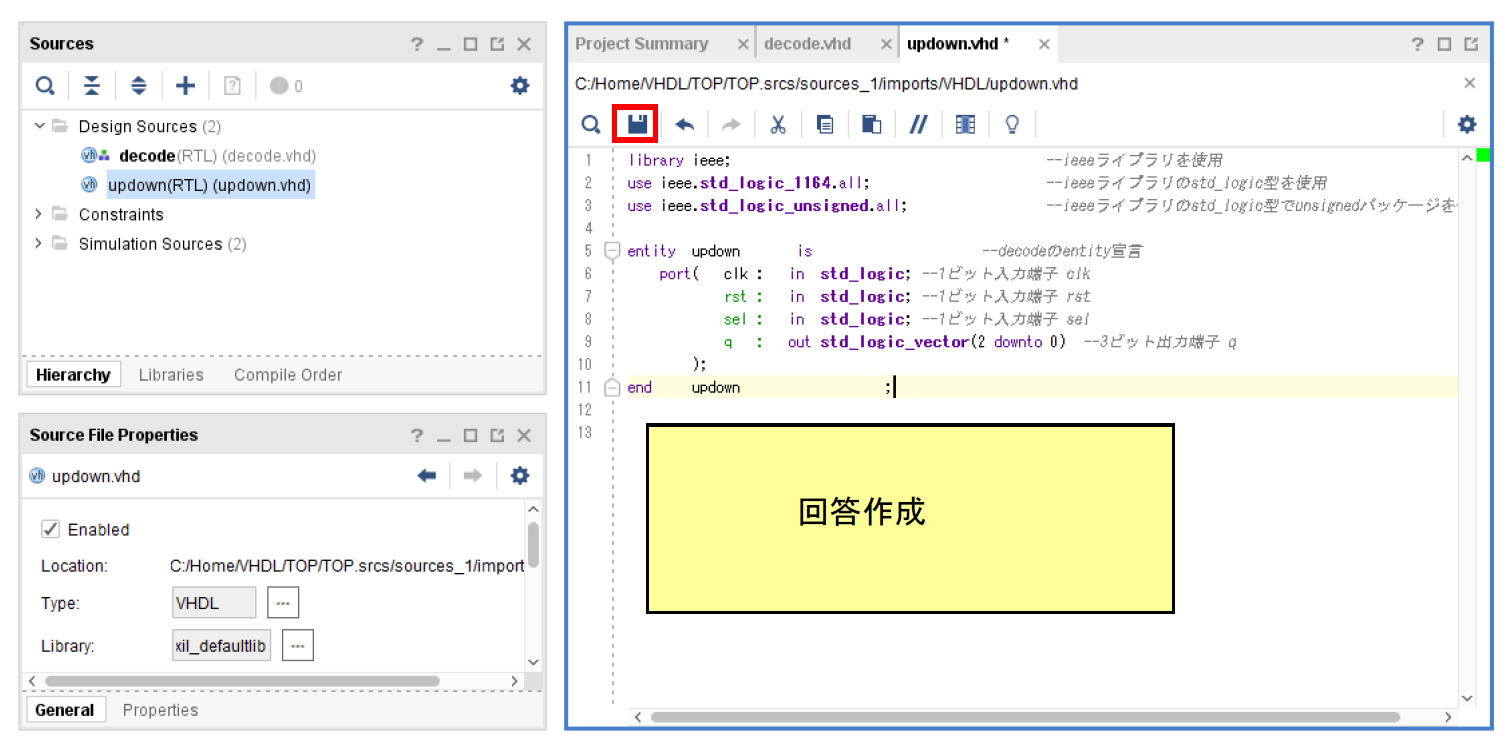

2.updown.vhdファイルの完成

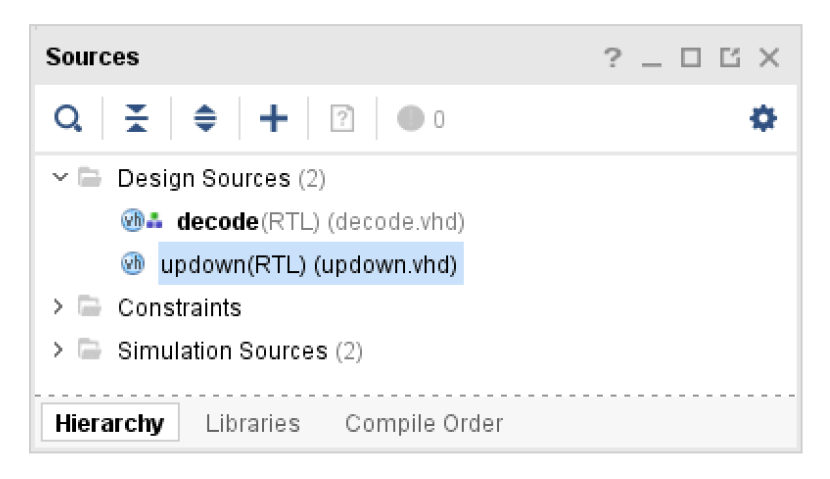

手順1:ファイルを開きます。

Sourceウィンドウ表示されている updown.vhdファイルをダブルクリックします。

図23 -Sourceウィンドウ

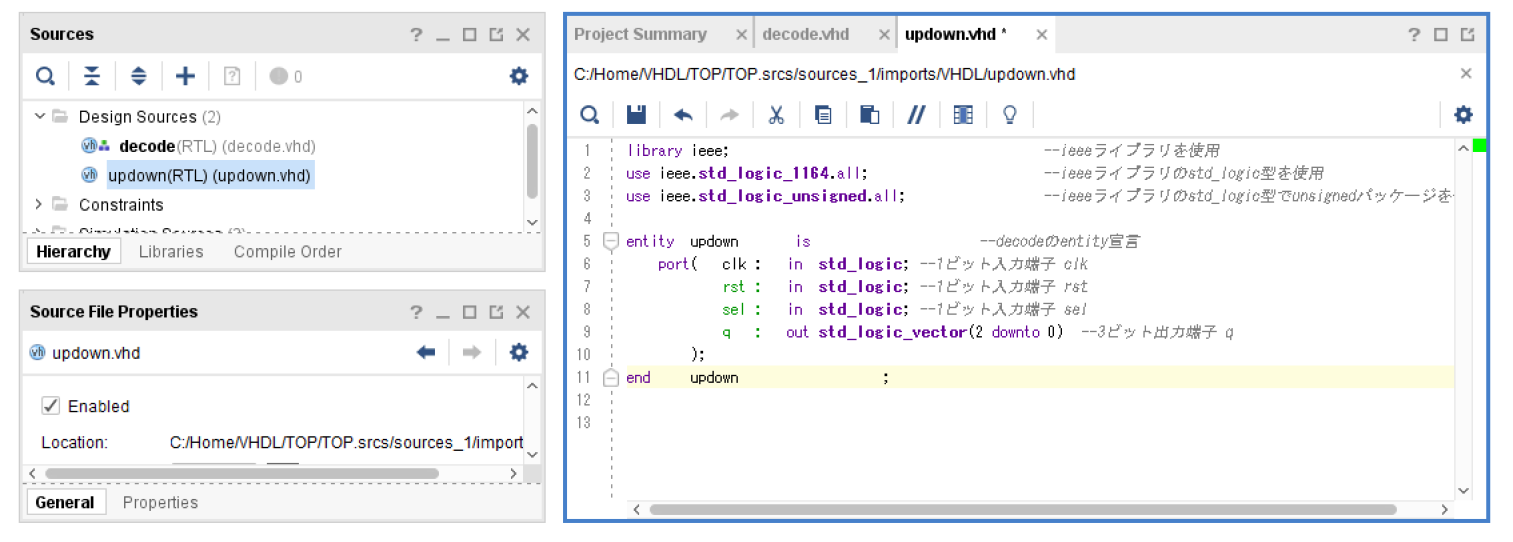

手順2:updown.vhdファイルが開かれます。

未完成の回路記述が表示されます。

図24 -テキストエディタ画面

手順3:ソースコードを完成させる。

ファイル内の空欄を埋めて、ファイルを完成させて、保存してください。

図25 -ファイル編集画面

3.VHDL文法チェック

手順1:ソースコードに文法エラーチェックを演習(2)での 「VHDL文法チェック」を参照し、修正します。

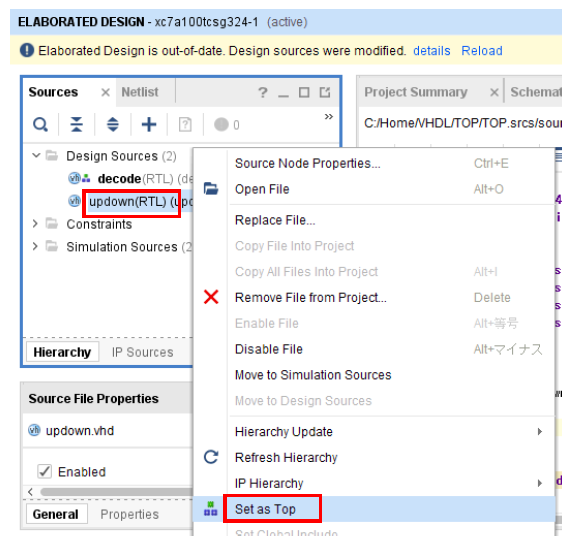

手順2:トップモジュールの切り替え

updown.vhdを選択し、右クリックメニューから Set as Topを選択し、トップモジュールを切り替えます。

図26 -トップモジュールを指定

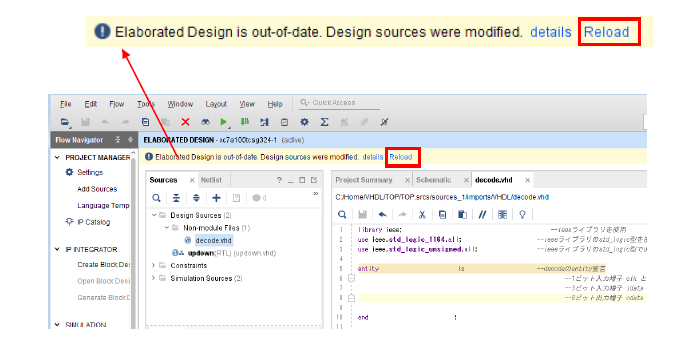

手順3:デザインのリロード

Reloadをクリックします。

エラーが表示されたら、ソースコードを修正し、保存します。

エラーがなくなるまで、繰り返します。

図27 -Elaborated Design の Reloadメッセージ

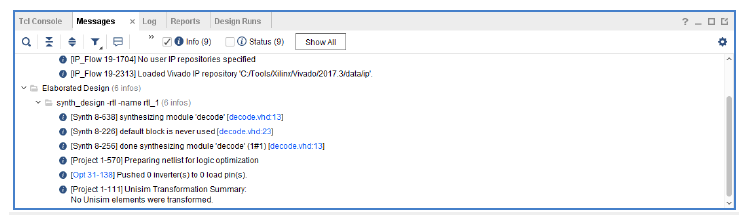

手順4:文法チェックOK

最後的に以下のように赤いエラーメッセージが表示されなくなれば、文法チェックOKとなります。

図28 -Messageウィンドウの表示

演習解答

図29 -演習(3)の解答

作業を振り返って

クロックは0から1、1から0変更している信号です。

順序回路の種類と記述の方法が理解できたかと思います。

次回演習(4)は「階層設計」です。

最後までお付き合いいただきありがとうございました!

次回もご覧ください。

このブログは「FPGA設計ブログ一覧」の

1. コーディング・IP設定・プリミティブ設定 のひとつです。

これからもTECHブログを通じて、皆様の設計にお役立てできればと思います。 VHDLの使い方、設計に関する問い合わせなどありましたら、ご連絡ください。