【新人ブログ ミンガラバー】VHDL初級編 part.1 ~VHDL記述の基本フォーマット~

ミンガラバー(Mingalaba)!

“ミンガラバー” はミャンマー語で “こんにちは” という意味です。

私は2020年度にPALTEKに入社したミャンマー出身のシーでございます。

私はミャンマーの大学で、電気やハードウェアの基本を学びました。

ハードウェア記述言語(HDL)の基本も学習しましたが、実際にXilinxのボードを動かしたことはありませんでした。そんな私が社内研修ではじめてHDLを使いXilinxボードでスロットマシンを開発できるようになりました。

このブログでは研修で学んだVHDL記述の基本フォーマット、VHDLやVerilog-HDLについて簡単に紹介させていただきます。いろいろなことを学習中なので至らないところは多いかと思いますが、同じく学習中の方に少しでも役に立てば幸いです。

研修ではVHDLの基本を5回にわけて一つずつ実践しました。

ブログも5回にわけ、演習(1)から(5)として紹介します。それでは、演習(1)から始めましょう。

このブログは「FPGA設計ブログ一覧」の

1. コーディング・IP設定・プリミティブ設定 のひとつです。

目次

RTLとは

演習に入る前に、まずRTLについて説明します。

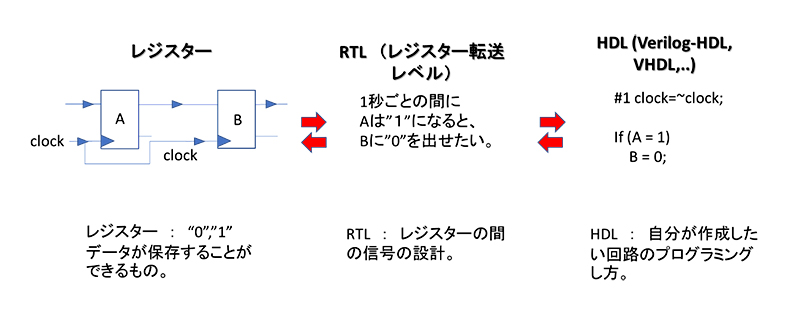

レジスタ転送レベル(Register Transfer Level)の省略です。RTLの定義は次の通りです

図 1-レジスタ、RTL、HDL関係のイメージ図

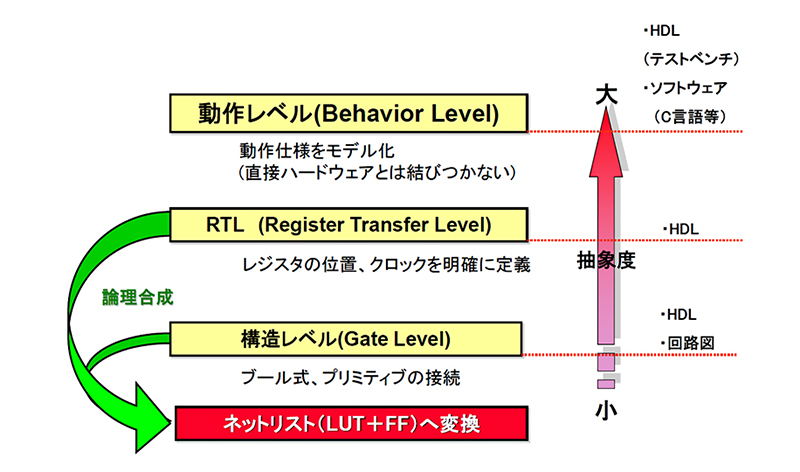

図 2- 論理合成と記述レベル

| 動作レベル | テストベンチのような記述です。 詳しくは考えずに動作だけを確認したい場合に記述するものです。 例えば、この信号は「何クロックにHIGHになってください」みたいな記述です。実際にインプリメントすると、エラーになることが多いです。 |

|---|---|

| RTL | レジスタの間の信号転送を集中して記述するものです。 設計者はレジスタを宣言してからif-elseif文など使って組み合わせ論理回路を設計します。 |

| ゲート・レベル | [and, or, nandなど]ゲートを利用して設計するものです。ネットはハードウェア要素間の接続を表しています。 |

演習(1)Library宣言部分とEntity宣言部分を理解する

前提条件

今回はDigilent社のBasys 3 Artix-7 FPGA Trainer Board(以下、Basys3ボード)に搭載されているXilinx社のArtix-7 FPGAデバイスのデータ(Device名、Package名等)を使って学習します。

Xilinx社の製品を開発する場合は、Vivado® Design Suite HLx Editionという開発ツールをインストールする必要があります。

今回はVivado2020.1を使用しながら説明していきます。

演習(1)ではVivado® Design Suite をインストールすれば十分です。

PCのOSは、Windows 10を使用しました。

Library宣言部分とEntity宣言部分

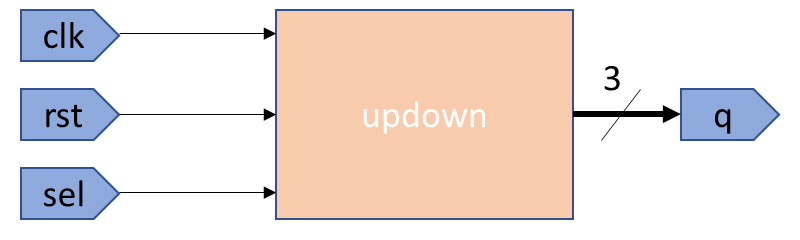

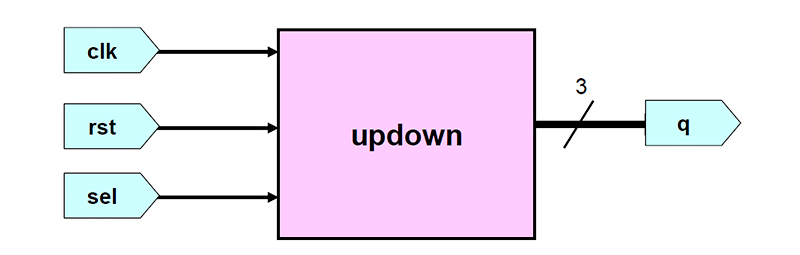

Library宣言部分とEntity宣言部分を理解するため、Vivado® Design Suiteを使って以下の回路を作成します。

| entity名 | updown |

|---|---|

| 入力ピン名 | clk、 rst、 sel |

| 出力ピン名 | q(3ビット) |

図 3-Entity概要

デザインファイルの全体

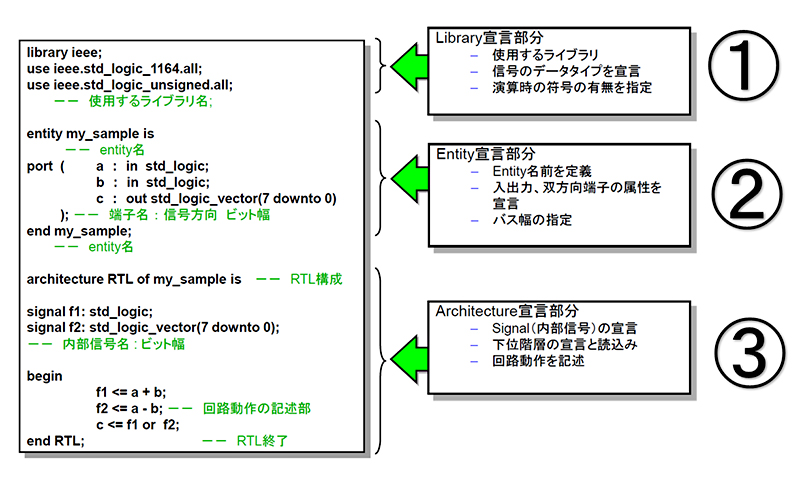

図 4-デザインファイルの全体

図 5-VHDL記述の説明

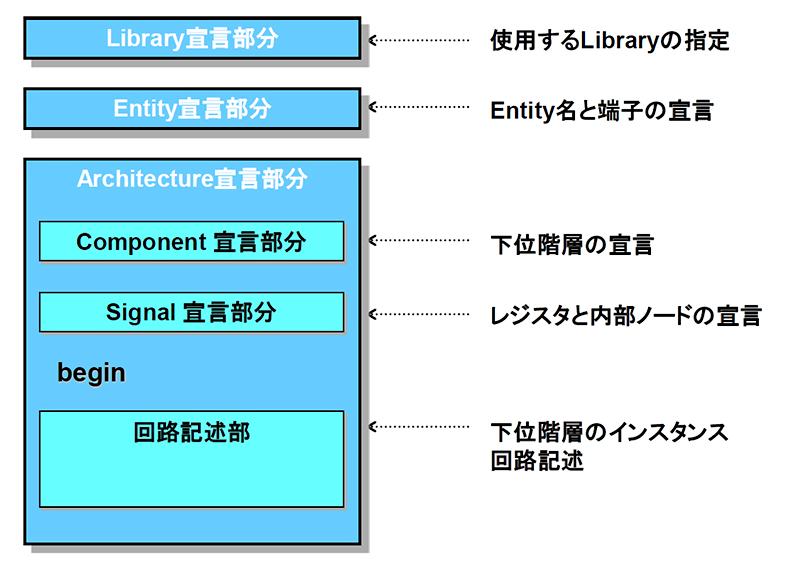

VHDLデザインは基本的に

① Library

② Entity

③ Architecture

として3つに分けられます。

演習(1)では、Library宣言部分①とEntity宣言部分②を記述します。

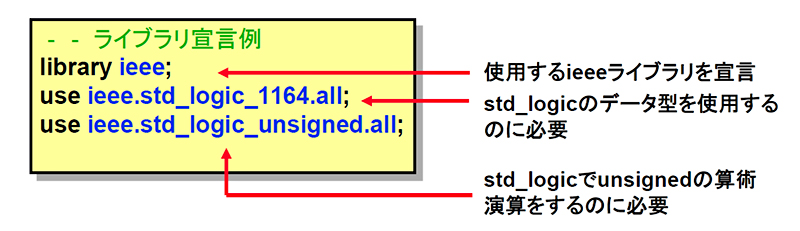

Library宣言

文法

- library ライブラリ名;

use ライブラリ名.パッケージ名.all;

Library宣言は、ファイルの先頭に記述して宣言したライブラリ中身を使用可能にします。

[.all]は、指定したパッケージの中身を全部使用可能にする構文です。

図 6-library宣言

std_logicのデータ型

- ‘0’ - 0

‘1’ -1

‘X’ -不定

‘Z’ -ハイ・インピーダンス

‘U’ -初期状態

‘L’ -弱い信号の0

‘H’ -弱い信号の1

‘W’ -弱い信号の不定

‘-‘ -don’t care

その中から [‘0’,’1’,’X’,’U’]は主に使われるデータタイプです。

注意:全て大文字で記述しなければ、Errorとなります!

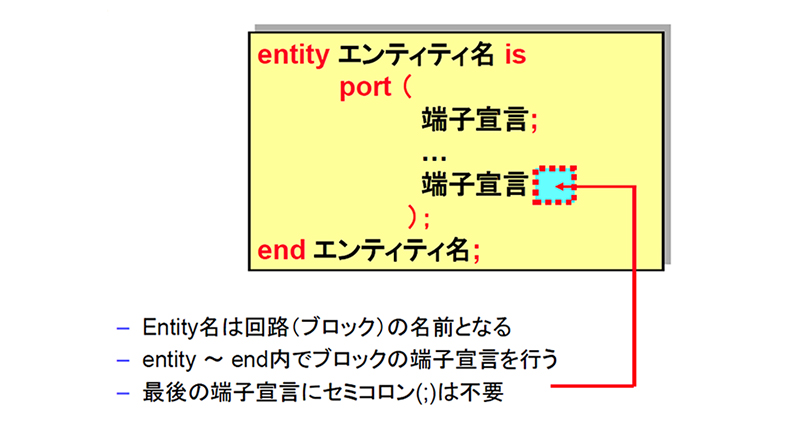

Entity 宣言

文法

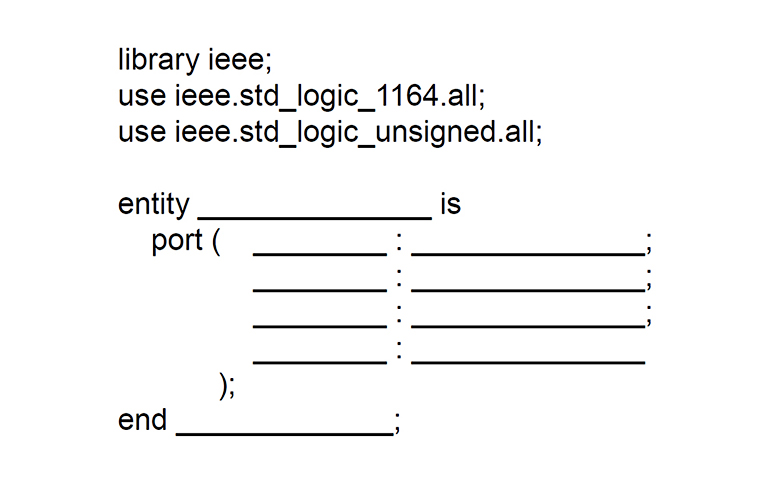

図 7- entity部分

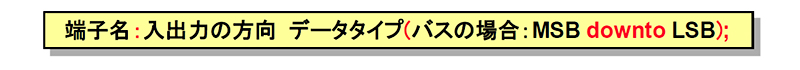

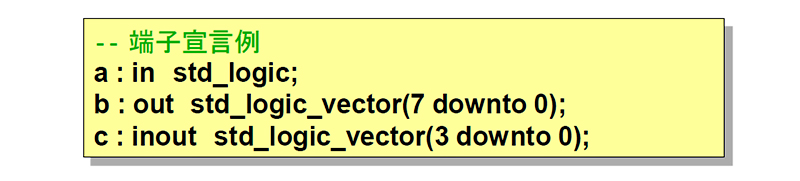

端子宣言

文法

図 8-端子宣言の文法

入力の方向 :in, out, inout(双方向)の3種類

データタイプ:1bit信号 std_logic

バス信号 std_logic_vector(MSB downto LSB)

図 9-端子宣言例

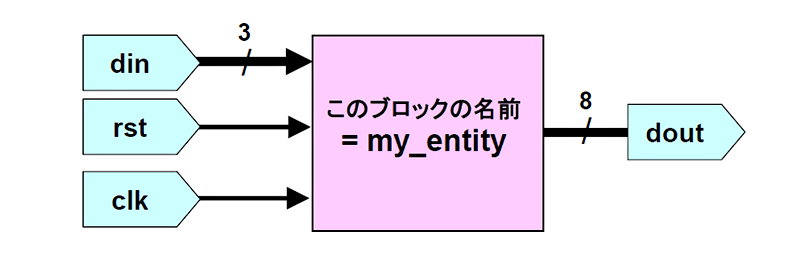

Entity記述例

- entity my_entity is --entity 宣言

port(

clk : in std_logic; --entityの端子宣言

rst : in std_logic;

din : in std_logic_vector (2 downto 0 );

dout : out std_logic_vector (7 downto 0 );

);

end my_entity;

図 10-例ブロック図

ここまで理解したら次の課題はできるはずです。

課題

以下のブロック図を見ながらlibrary とentityをVivado® Design Suiteで実際に作成してみましょう。

図 11-課題ブロック図

Vivado® Design Suite の作業手順

Vivado® Design Suiteでの作業手順は以下の通りです。

1. Vivado® Design Suite の起動

2. 新規プロジェクトの作成

3. 新規ファイルの作成と保存

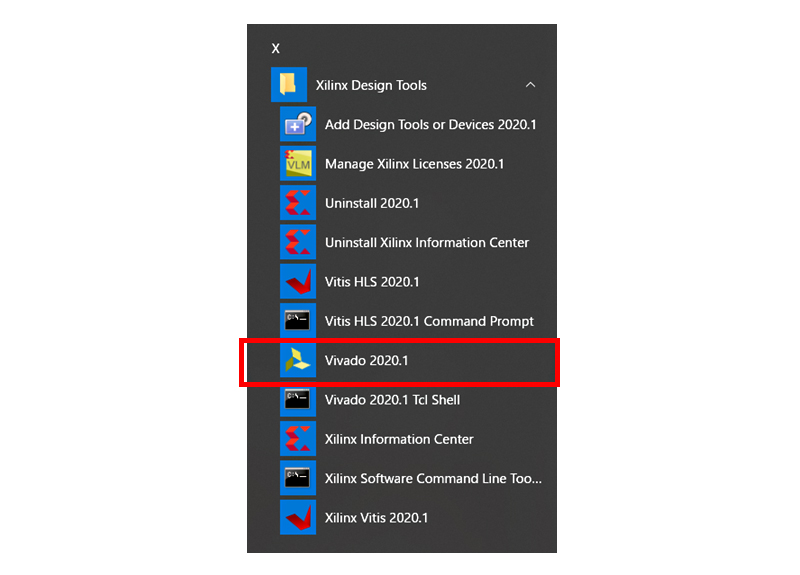

1.Vivado® Design Suiteの起動

PCの スタートメニュー > すべてのプログラム > Xilinx Design tools > Vivado 2020.1

図 12- Vivado® Design Suite起動

2.新規プロジェクト作成

手順1 : 新規ファイルプロジェクトを作成します。

Create Project をクリックします。

図 13-新規プロジェクト作成

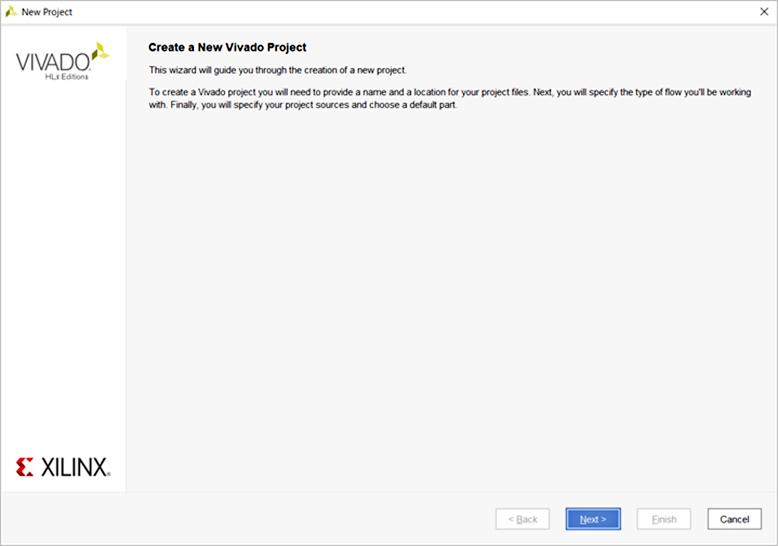

手順2 : 新規プロジェクト作成のダイアログが起動します。

Nextをクリックします。

図 14-新規プロジェクト作成ダイアログ

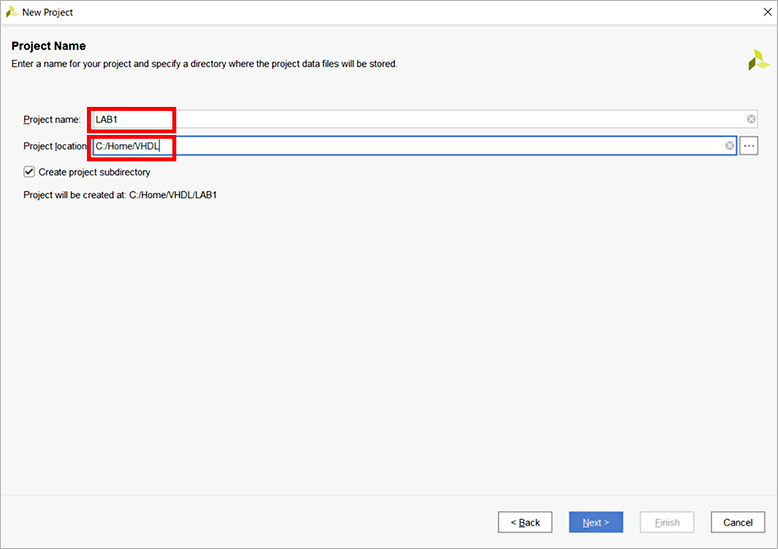

手順3 : プロジェクト名/保存先フォルダを指定します。

プロジェックと名:LAB1

保存先フォルダ:C:/Home/VHDL(自分で適当にしても構いません)

を指定して、Nextをクリックします。

図 15-プロジェクト名の指定

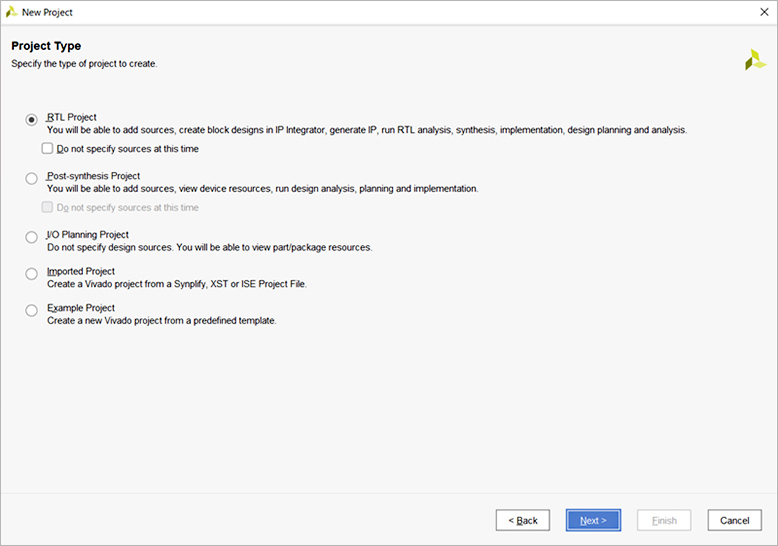

手順4 : プロジェクト種別を指定します。

RTL Projectを選択して、Nextをクリックします。

図 16-プロジェクト種別の指定

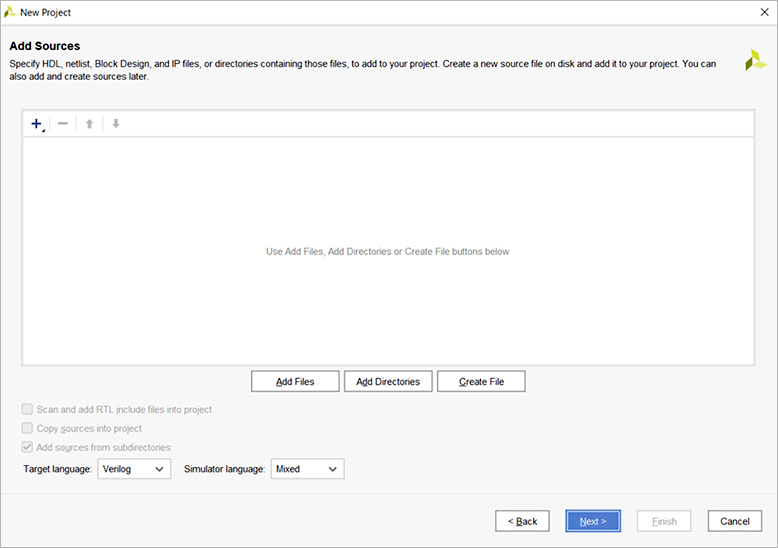

手順5 : 既存ソースコードを追加します。

何もせず、Nextをクリックします。

図 17-既存ソースコードの追加

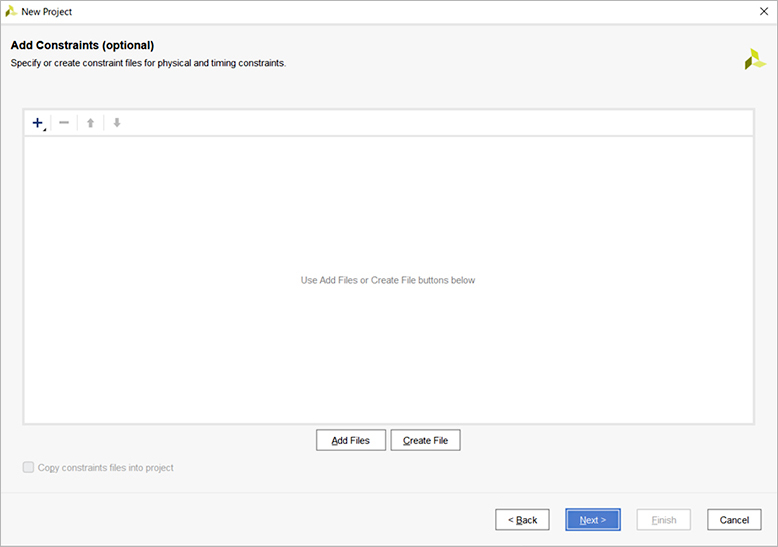

手順6 : 既存の制約ファイルを追加します。

何もせず、Nextをクリックします。

図 18-既存の制約ファイルの追加

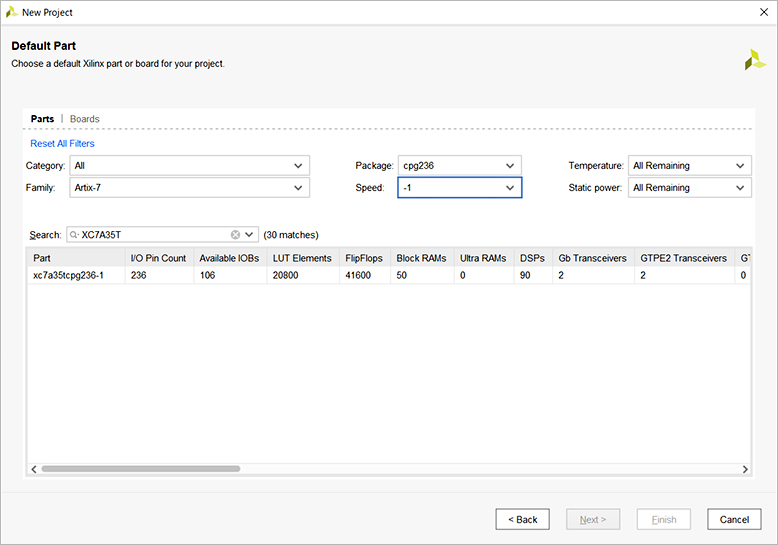

手順7 : ターゲットデバイスを選択します。

以下ターゲットデバイスを選択し、Nextをクリックします。

[ターゲットデバイスの設定]

Family : Artix-7

Device : XC7A35T

Package : CPG236

Speed grade : -1

※詳細の情報は Basys3ボードのリファレンスマニュアルから確認することができます。

図 19-ターゲットデバイスの選択

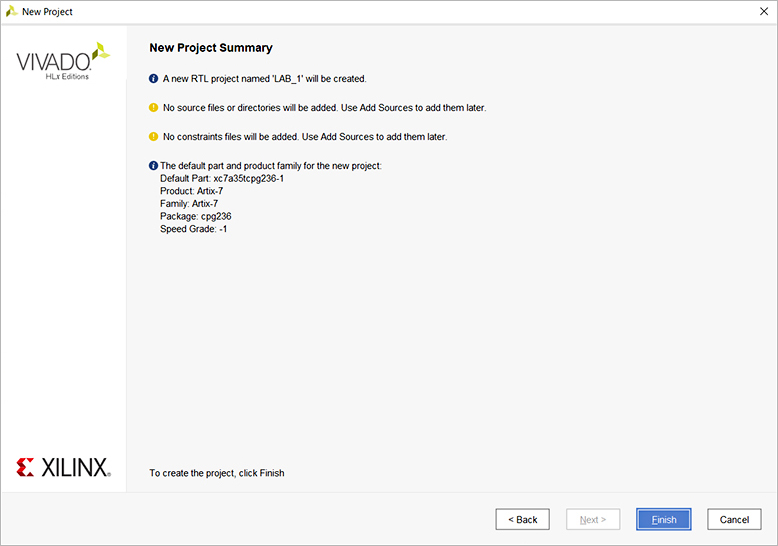

手順8 : 設定の確認ダイアログ。

設定の確認ダイアログが表示されるので、Nextをクリックします。

図 20-設定の確認ダイアログ

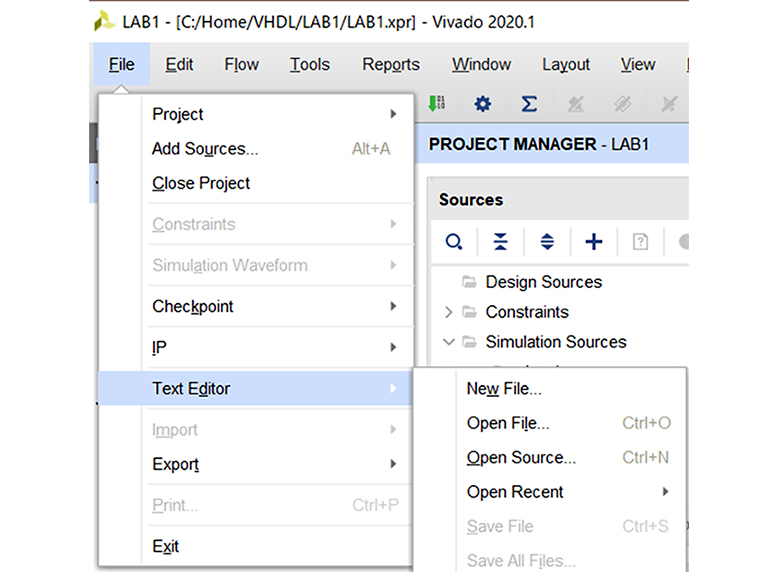

3.新規ファイルの作成と保存

手順1 : 新規ファイルを作成します。

図 21-新規ファイルの作成

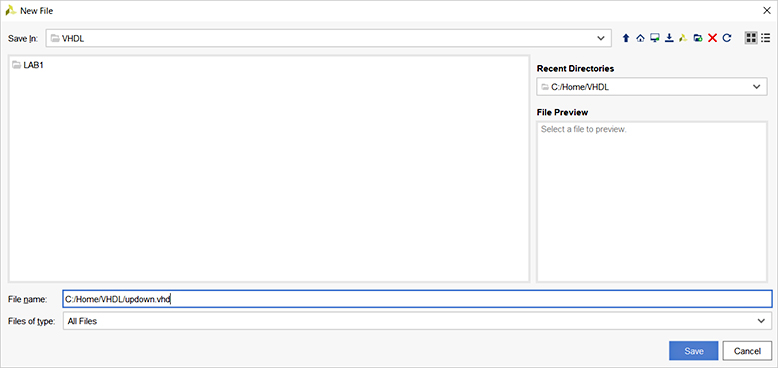

手順2 : 新規ファイルを作成します。

以下保存先フォルダ、ファイル名を指定して、

保存先フォルダ : C:/Home/VHDL(自分で適当にしても構いません)

ファイル名 : updown.vhd

Saveをクリックします。

図 22-新規ファイル作成ダイアログ

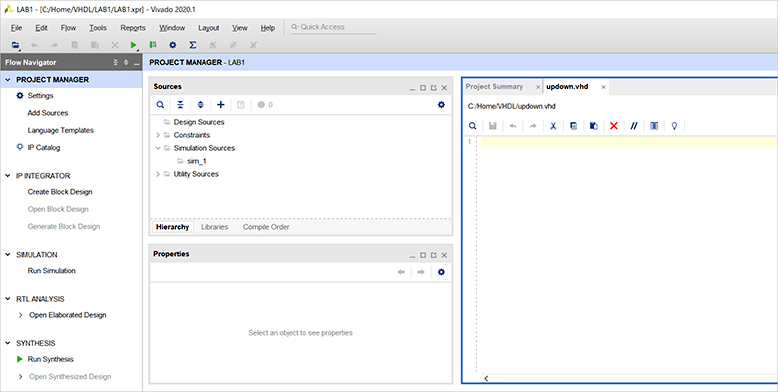

手順3 : ファイル内容を記述します。

テキストエディタでファイルが開くので、演習(1)の回答を記述してください。

図 23-ファイルの編集

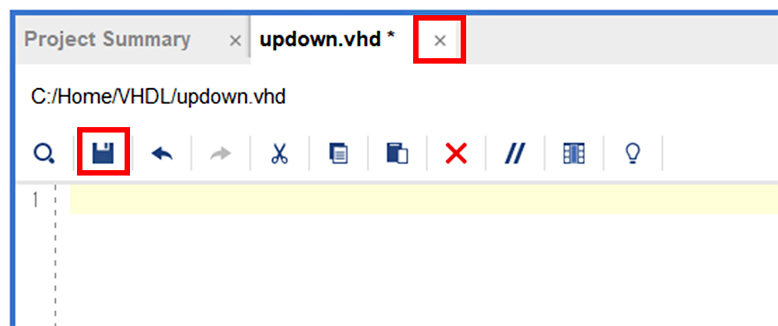

手順4 : ファイルを保存します。

ファイル保存アイコン  を押して、ファイルを保存します。

を押して、ファイルを保存します。

手順5 : ファイルを閉じます。

図 24-ファイルを保存、閉じる

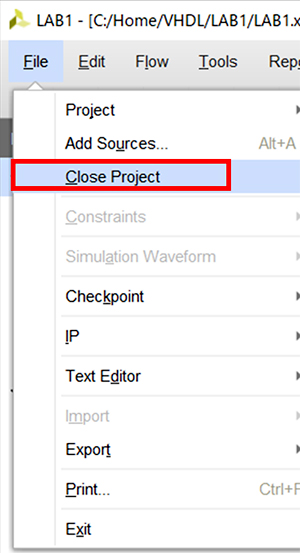

手順6 : プロジェクトを閉じます。

File > Close Projectを選択します。

図 25-プロジェクトを閉じる

課題のヒント

以下は課題のヒントです。

解答は次回の演習(2)に掲載しますので、是非確認してください。

図 26-課題ヒント

作業を振り返って

RTLは、レジスタとレジスタの間にどのように接続するかを想定して設計することです。

想定したことを設計する際は、HDLというVerilog-HDL、VHDL言語で設計します。

以上でVHDLの libraryとentityの書き方、またはVivado® Design Suite の新規プロジェクトの作成のし方が理解できたかと思います。

一つずつ実行して学びながら簡単な回路を作成できるまでお伝えしようと思います。次回演習(2)は「組み合わせ回路」です。

最後までお付き合いいただきありがとうございました!

次回もご覧ください。

このブログは「FPGA設計ブログ一覧」の

1. コーディング・IP設定・プリミティブ設定 のひとつです。

これからもTECHブログを通じて、皆様の設計にお役立てできればと思います。 VHDLの使い方、設計に関する問い合わせなどありましたら、ご連絡ください。