【回路設計ヒント】FPGAの端子と回路図の接続信号との確認方法

みなさんこんにちは

回路でFPGAの配線接続の確認はどのように行っていますか。オーソドックスな方法ですと、印刷をした回路図と端子表を用意し色ペンで配線をたどって表にもチェックをつけていく感じですよね。

この方法は、端子数や配線数が増えてくると時間や労力がかかり、ましてや回路が変更になった場合には…もう一度確認しなければなりません。

そこで、CADから得られる情報と端子表を使って確認する方法を紹介したいと思います。

このブログは「FPGA設計ブログ一覧」の

基板設計・評価関連のひとつです。

目次

1.デザイン

この説明では次のFPGAと回路のデザインを使用します。

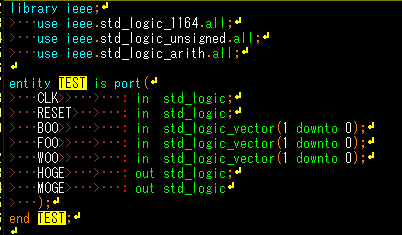

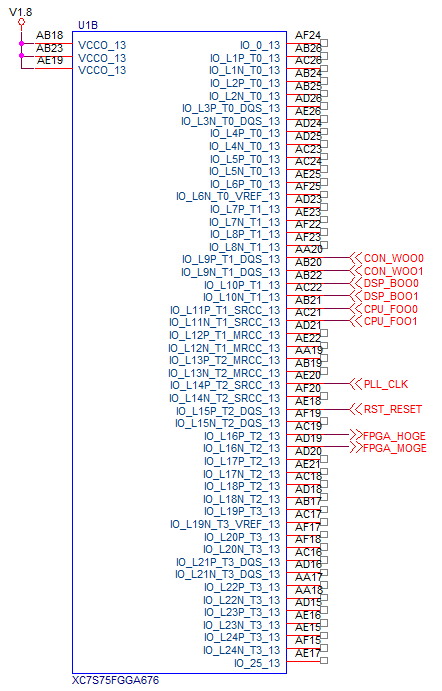

FPGAは次のようになっています。

◆トップソース

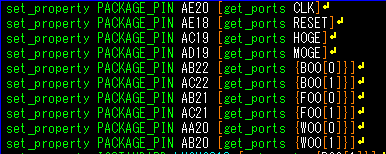

◆Constraintsファイル(.xdc)

回路図は次のようになっており、この部分(BANK13)だけの説明で使用します。

FPGAのリファレンスはU1で、配線名の先頭には出力デバイスの名称をつけています。

※CON_ はコネクタです

2.前提条件

紹介する方法の前提条件は、設計時にFPGAでの端子名またはFPGAの端子表での名称と、回路上での配線名が同様であることです。

そうでない場合は、容易に加工ができて一致させることができるようにしておく必要があります。

3.FPGA側での用意

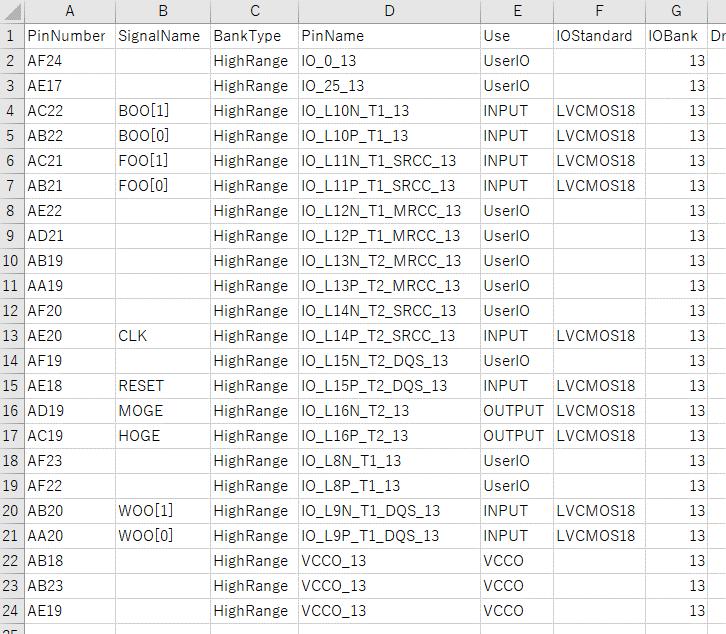

仕様書などからFPGAの端子表を作成するか、デザインができていればツールが出力するIOレポートから端子表を作成します。

下の図は、Vivado® Design Suiteが出力したIOレポート

(<<projct-name>>_io_placed.rpt ) を加工したものです。

4.回路図CAD側での用意

ネットリストの形式が自由に選べるCADについては加工しやすい形式を選択し、配線名と端子番号を抽出します。

※Cadence社 OrCAD® CaptureでTelesis形式のネットリストを出力した場合

CAD上でシンボルの端子や端子番号とネット情報が取りだせる場合には、その内容をコピーして配線名と端子番号か端子名を抽出します。

※Siemens社 PADS® の場合、シンボルを選択して「接続ネットをリストアップ」を実行すると下の図のように情報が取り出せます。

5.確認作業

「3.FPGA側での用意」で作成した端子表と「4.回路図CAD側での用意」で抽出した情報をExcelなどで比較します。

ただし、内容によっては単純に比較ができないため文字加工を行います。今回は回路のネット名にあわせるように文字を加工していきます。

文字加工1はSignalName(B列)から信号名だけを抽出しています。

文字加工2はSignalName(B列)からbitの番号だけを抽出しています。

文字加工3は1と2を組み合わせたものです。

文字加工4はバスだったものは3を、そうでないものはSignalName(B列)を選択しています。

ネットリストの情報を比較した場合の文字加工5は SignalName(K列)のいらないプリフィックスを削除しています。

◆FPGAのIOレポートとネットリストの情報を比較した場合

FPGAとCADどちらも端子番号(A列、J列)でソートしています。

◆FPGAのIOレポートとCADから出力した情報を比較した場合

FPGAとCADどちらも端子名(C列、J列)でソートしています。

どちらも文字加工4と文字加工5を比べることで、接続間違いがないかの確認が行えます。

いかがでしたでしょうか?

Excelなどでの関数やスクリプトを使いこなす必要がありますが、一度方法を確立すれば修正があった場合、すぐに対応できます。

もちろん、この方法はFPGAだけでなくCPUやコネクタといった多ピンの接続確認にも使うことができます。

これからもTECHブログを通じて、皆様の設計にお役立てできればと思います。

次回のブログもどうぞよろしくお願いいたします。

尚、CADツールについてはお使いのCADメーカーにお問い合わせください。

最後までお付き合いいただきありがとうございました。

このブログは「FPGA設計ブログ一覧」の

基板設計・評価関連のひとつです。