【回路設計ヒント】どうする?FPGAの端子アサイン ~コンフィグレーション編~

皆さん、こんにちは。

FPGAの端子アサインはどのように決定していますか?

- FPGA設計者が主体で決めている

- 回路(基板)設計者が主体で決めている

- FPGAも回路も一人で両方担当している

などさまざまなケースがあると思います。

一人で両方を行っている場合には臨機応変に修正対応が可能ですが、分業している場合には

- FPGA設計者が決めると「パターンの引き回しが考慮されない」

- 回路設計者が決めると「FPGAの機能や仕組みが考慮されない」

といった問題が生じることがあります。

中でも最も困るのは、基板が完成したにもかかわらず、端子アサインが原因でVivado™やISE®での合成が通らず、実機が動作しなかったり、基板の作り直しが必要になったりするケースです。

そこで今回は、FPGAを使い始めた方やFPGA内部構造にあまり詳しくない方に向けて、FPGAの端子アサインにおけるコンフィグレーション関連の重要なポイントを紹介したいと思います。

それでは、はじめましょう。

目次

ここで掲載している図表は例として挙げています。

すべてのデバイスシリーズに当てはまるわけではありません。

必ずご使用になるデバイスシリーズのデータシートで内容をご確認ください。

コンフィグレーションモード

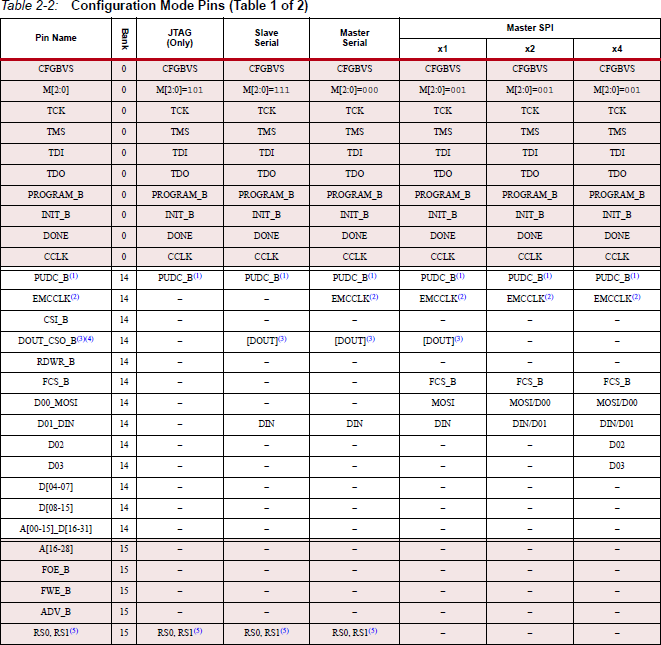

FPGAのコンフィグレーション関連の端子は、デバイスシリーズやコンフィグレーションモードによって、複数のI/O BANKにまたがって配置されています。

この特性を考慮せずに、単純にデザインで使用する端子数だけでデバイスを選定してしまうと、以下のような問題が発生する可能性があります。

- 必要な端子数が不足する

- 使用したいI/O電圧とコンフィグレーション関連信号の電圧要件が合わない

これらの問題を避けるため、各デバイスシリーズのコンフィグレーションユーザーガイドには、コンフィグレーションモードごとに必要な端子とI/O BANKの情報が詳細に記載されていますので、必ず事前に確認してください。

参考として、AMD社の7シリーズの場合は次のような構成となっています(一部抜粋)。

出典:

UG470 7 Series FPGAs Configuration User Guide <P.18> (参照 2024/11/25)

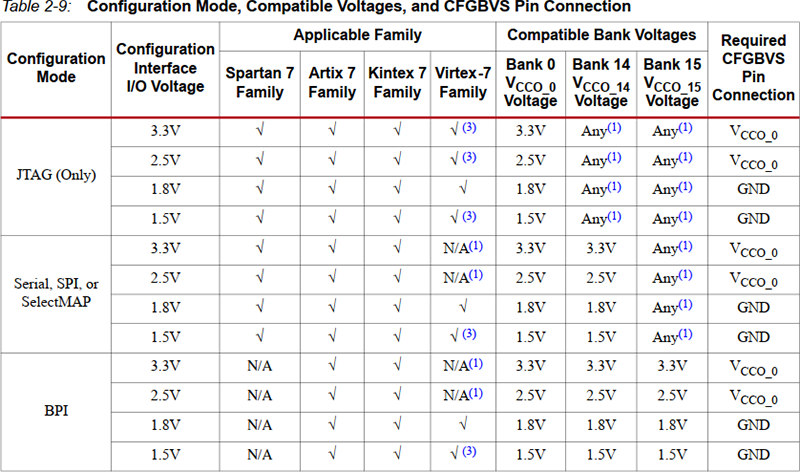

また、コンフィグレーションユーザーガイドには、各モードで使用するI/O BANKに必要な電源電圧についても詳細に記載されています。これらの電圧要件は、回路設計時の重要な検討事項となります。

出典:

UG470 7 Series FPGAs Configuration User Guide <P.32> (参照 2024/11/25)

多機能端子の接続

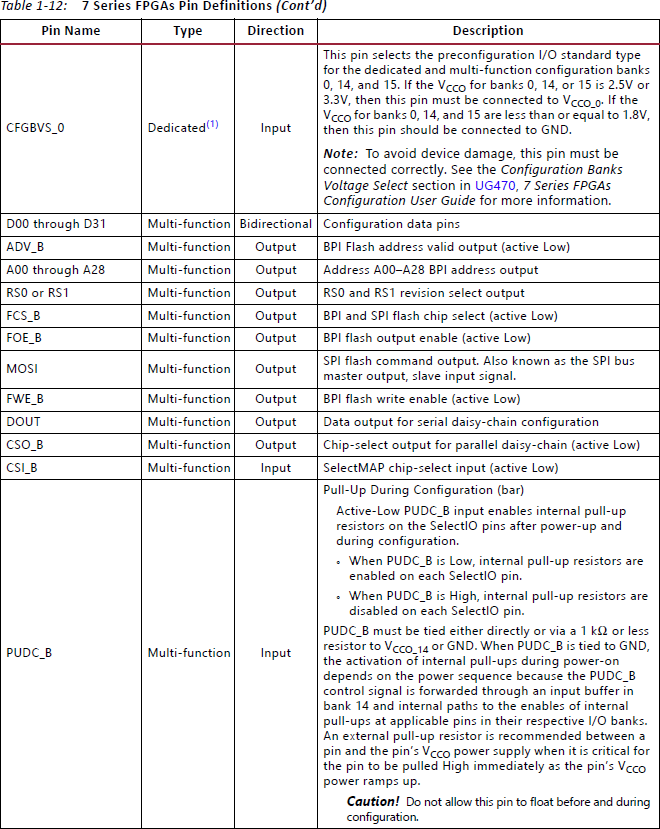

コンフィグレーション関連の端子で特に注意が必要なのが、「Dual-purpose」や「Multi-function」と呼ばれる多機能端子です。これらの端子は、コンフィグレーション時と通常動作時で異なる機能を持ちます。

以下に、AMD社の7シリーズFPGAにおける代表的な端子タイプを示します(一部抜粋)。

出典:

UG475 7 Series FPGAs Packaging and Pinout Product Specification User Guide <P.22> (参照 2024/11/25)

これらの多機能端子は、FPGAの動作状態によって異なる機能を持ちます。

| コンフィグレーションモード (電源起動直後やコンフィグレーション中) |

コンフィグレーション用の機能端子として動作 |

|---|---|

| ユーザーモード (コンフィグレーション完了後) |

ユーザーI/Oとしてデザインに従って動作 |

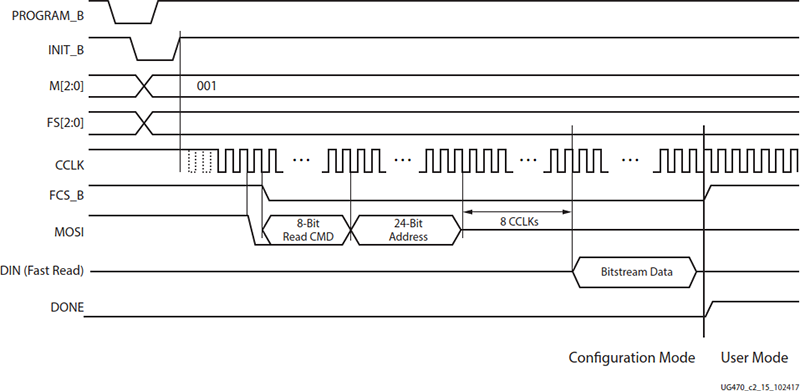

図1は、SPIx1モードでのコンフィグレーション時の動作例を示しています。

DONE信号がLowからHighに遷移する時点でモードが切り替わり、I/Oの機能もユーザーデザインで定義した内容に変更されます。

図1. 7シリーズ FPGA SPIx1モード コンフィグレーションシーケンス

出典:

UG470 7 Series FPGAs Configuration User Guide <P.49> (参照 2024/11/25)

「Dual-purpose」や「Multi-function」タイプの端子をデザインで使用する際は、このようなモード切り替えに伴う機能変更を十分に考慮する必要があります。対向デバイスとの接続においても、両モードでの動作に問題がないか、慎重な検討が求められます。

Pull-Up設定の注意点

コンフィグレーション中のユーザーI/Oは、基本的にHi-Z状態となっています。ただし、端子のオプション設定により、Pull-Upの有効・無効を選択することが可能です。

制約事項

- Pull-Up設定は全I/O BANKで一括制御となります

- 特定のI/O BANKのみPull-Upを有効にするような個別設定はできません

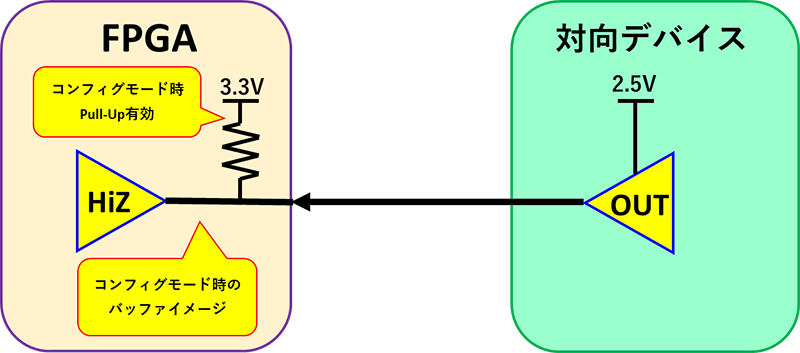

注意点①

コンフィグレーション中にPull-Upを有効にする場合、特に以下の状況で注意が必要です。

・ I/O BANKの電圧と接続デバイスの電圧が異なる場合

(注:

一部のデバイスシリーズでは、I/O BANKの電圧と異なる電圧レベルの信号入力が許容されています)

※

コンフィグ(コンフィグレーションの略)

図2. FPGAと対向デバイス間のインタフェース構成図

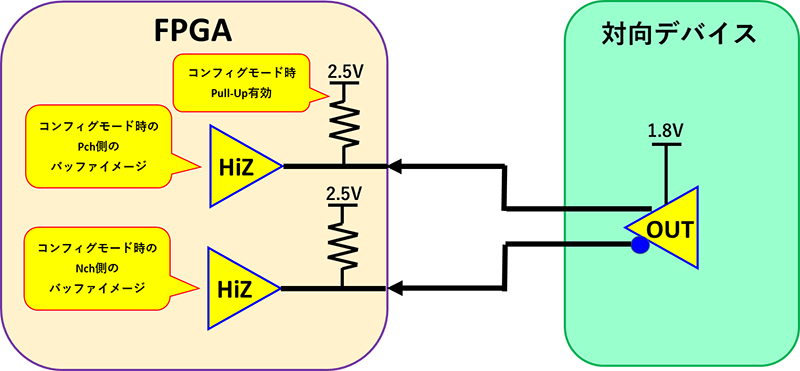

注意点②

コンフィグレーション中にPull-Upを有効にする場合、特に以下の状況で注意が必要です。

1. I/O BANKの電圧と接続デバイスの電圧が異なる場合

(注:

一部のデバイスシリーズでは、I/O BANKの電圧と異なる電圧レベルの信号入力が許容されています)

2. 差動信号をDC結合で接続している場合

- コンフィグレーション中:各端子にPull-Upが掛かることで差動バランスが崩れる可能性

- ユーザーモード(コンフィグレーション後):差動バッファとして正常動作

※

コンフィグ(コンフィグレーションの略)

図3. FPGAコンフィグレーションモード時のインタフェース構成

潜在的なリスク

コンフィグレーション中のPull-Up電圧が接続先デバイスに影響を与える可能性があります。

- 電源の回り込みによる誤動作

- 対向デバイスの予期しない動作

- 電源シーケンスへの影響

システム全体の電源投入シーケンスや接続デバイスの仕様を考慮し、Pull-Up設定を慎重に判断してください。

まとめ

- コンフィグレーションで使用するモード、制御信号、ROM、コンフィグレーションマスタ(CPUなど)を決めてからユーザーI/Oを割り振りましょう

- コンフィグレーション中とコンフィグレーション後で機能や状態が変わる端子には気を付けましょう

- コンフィグレーション中Pull-Upを有効にする場合には、接続先との電圧関係に注意しましょう

いかがでしたでしょうか?

このように、端子アサインに関連していろいろと条件がありますので、FPGAでの実現性確認と基板設計での最適化とを繰り返して端子を決めていくことが良いと思います。

最後までご覧いただきましてありがとうございました!

これからもブログを通じて、皆様の設計にお役立てできればと思います。

次回のブログもどうぞよろしくお願いいたします。

弊社ではFPGA設計や回路図設計、レイアウト設計、ソフトウェア設計、筐体設計などを受託開発しています。

サービス内容をWEBサイトに掲載していますので、ぜひご覧ください。

FPGAの活用に際して設計検討などありましたら、お気軽にお問い合わせください。