【Vivado®で使用するXDCファイルの基本的な記述例】第1回 端子配置設定、クロック設定編

このブログでは、Vivado® ML Editionで使用する、「XDCファイル」の基本的な記述について解説します。

XDCとは、Xilinx Design Constraint(頭文字)の略です。

XDCファイルは、Xilinx社のFPGA及び適応型SoCに対して制約を与えることができるファイルで、以下の項目で制約設定が可能です。

- ・端子配置設定

- ・クロック設定

- ・コンフィグレーション設定

- ・タイミング設定 など

今回は、端子配置設定の中の、「端子配置設定」、「クロック設定」について説明します。

このブログは「FPGA設計ブログ一覧」の

4. インプリメント(配置配線)のひとつです。

目次

端子配置設定(端子配置、IO規格)

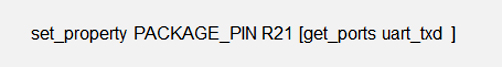

FPGA信号名“uart_txd”をFPGA端子“R21”に配置する場合の記述例

→get_portsコマンドで与えた文字列“uart_txd”を PACKAGE_PINプロパティの文字列“R21”にセットします。

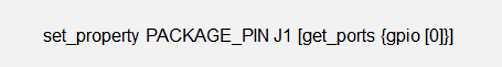

BUS信号の場合、{}で囲む必要があります。

→get_portsコマンドで与えた文字列“gpio[0]”を PACKAGE_PINプロパティの文字列“J1”にセットします。

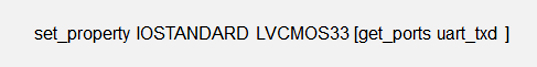

FPGA信号名“uart_txd”を“LVCMOS33”のIO規格制約を与える場合の記述例

→get_portsコマンドで与えた文字列“uart_txd”をIOSTANDARDプロパティの文字列“LVCMOS33”をセットします。

※LVCMOS33→3.3Vバンクに対応します

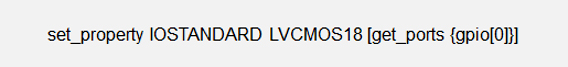

BUS信号の場合、{}で囲む必要があります。

→get_portsコマンドで与えた文字列“gpio[0]”を IOSTANDARDプロパティの文字列“LVCMOS18”をセットします。

→IOSTANDARDは、ワイルドカードが使用できます。

※LVCMOS18→1.8Vバンクに対応します

他のIO規格として、以下の制約ができます。

シングルエンド規格LVCMOS12、LVCMOS15、LVCMOS18、LVCMOS25、LVCMOS33、LVTTL

差動規格

TMDS_33、LVDS、LVDS_25

SSTLやHSTL

SSTL15、SSTL18_I、SSTL18_II

HSTL_I、HSTL_II、HSTL_II_18

DIFF_SSTL15、DIFF_SSTL18_I、DIFF_SSTL18_II

DIFF_HSTL_I、DIFF_HSTL_I_18

DIFF_SSTL15_DCI

DIFF_HSTL_I_DCI

などがあります。

※SSTLは主にDDR用の制約、HSTLは汎用です。

端子配置、IO規格の制約は、1行で記載可能です。

全体を{}で囲みます。

オプション設定

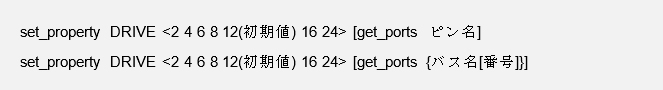

ドライブ強度[mA]

出力バッファの駆動電流を“mA”で指定します。

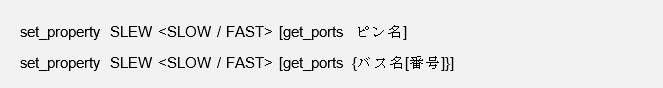

スルーレート

出力バッファのスルーレートを指定します。

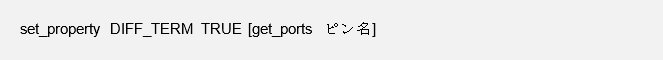

終端抵抗

差動入力、双方向バッファで使用する終端を指定します。

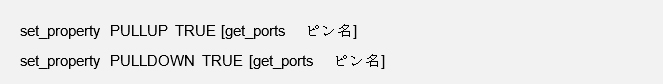

プルアップ・プルダウン

ウィーク プルアップ抵抗、ウィークプルダウン抵抗を有無の指定ができます。

※TRUE→FALSEでディセーブルになる。

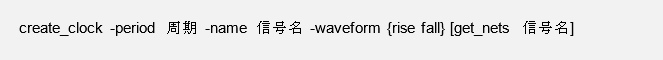

クロック設定

外部から入力するクロックの周波数を設定する。

周期:“ns” or “MHz”で指定する。

→単位を指定しない場合、“ns”が適用される。

rise、fall:省略した場合、0ns/duty50%が適用される。

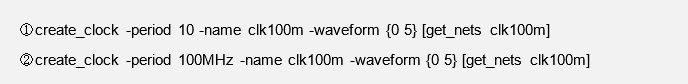

例1:100MHzのクロックの場合(信号名:clk100m)

①が周期をnsで記載した場合

②が周期をHzで記載した場合

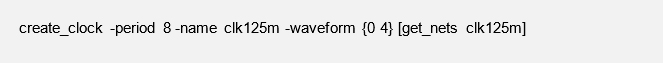

例2:125MHzのクロックの場合(信号名:clk125m)

以上となります。

次回は、コンフィグレーション設定、タイミング設定について解説します。

このブログは「FPGA設計ブログ一覧」の

4. インプリメント(配置配線)のひとつです。

今回説明した内容でのご不明な点や、FPGA設計などでお困りのことなどがありましたら、下記よりお問い合わせください。