【Versal™ACAP】I2C Example Design Clock切り替え編 Part2【Vivado® ML 2021.2】

皆さん、こんにちは。

今回は、 前回ブログ(【Versal™ACAP】I2C Example Design Clock切り替え編 Part1【Vivado® ML 2021.2】) の続きとなります。

今回は実機確認編となり、I2C制御で実際に周波数が切り替わるまでを紹介したいと思います。

それでは、始めましょう。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

目次

今回は、以下の環境で実行します。

- ・HostPC CentOS 7.6

- ・Vivado® ML Edition 2021.2

- ・Petalinux® 2021.2

レジスタ確認:I2Cスイッチ

前回の記事で、デザインの準備は完了しました。

今回は、I2CでOSC切り替えを行うにあたって、以下の手順でOSCの周波数切り替えを行います。

1. I2Cスイッチで切り替えたいOSCが接続されているチャネルを有効にする

2. Si570の出力周波数に影響のあるレジスタの値を変える

まずI2Cスイッチで切り替えるチャネルを確認します。

こちらは前回デザイン作成時に決めた周波数を変えるチャネルになります。

※画像クリックで大きな画像が表示されます。

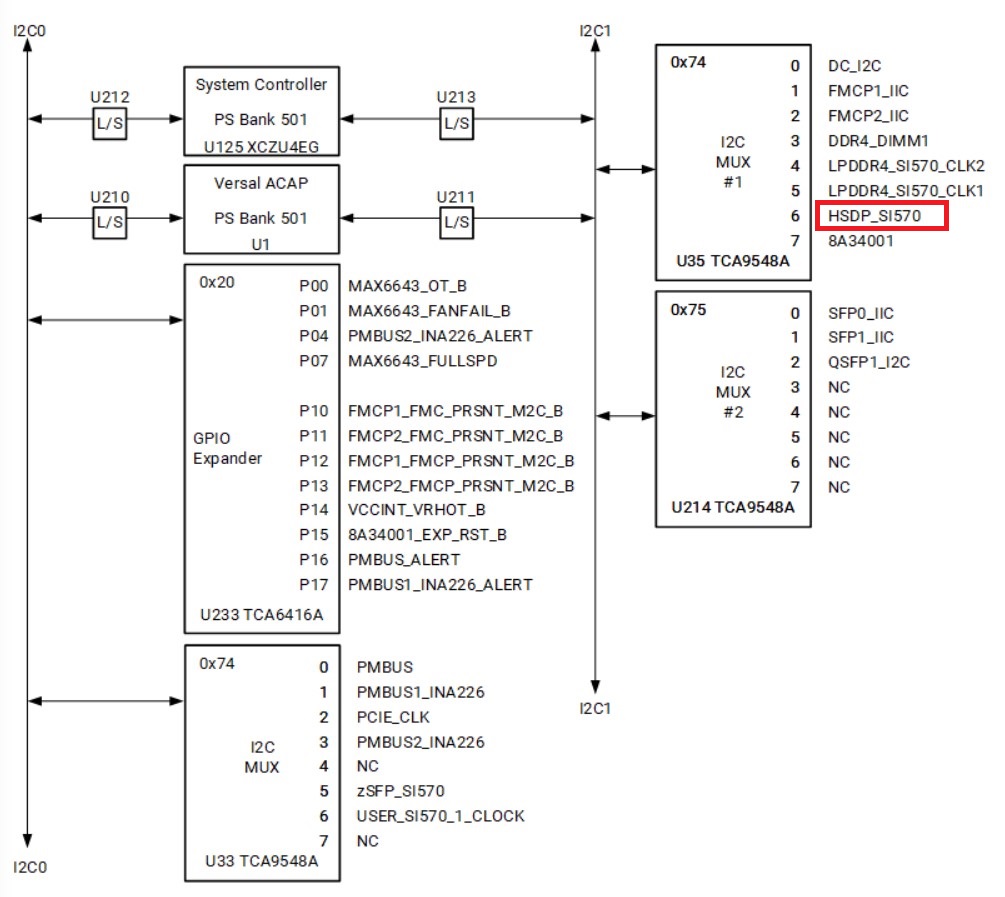

出典:Xilinx VCK190評価ボード ユーザーガイド(UG1366) [1] p32

I2C MUX #1のチャネル6が対象となります。

ここで、I2Cスイッチの部品名とデバイスアドレスが記載されているので確認します。

I2Cスイッチ:TCA9548A

デバイスアドレス:0x74

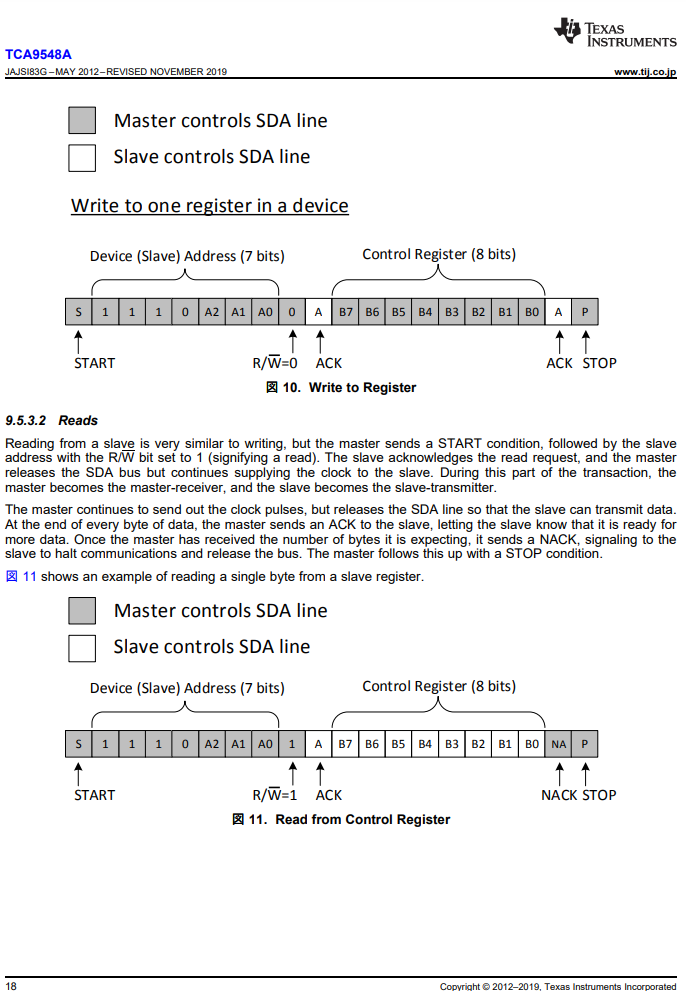

次にTCA9548Aのデータシート [2]を確認します。

アクセスはこちらに書かれていました。

※画像クリックで大きな画像が表示されます。

出典:TEXAS INSTRUMENTS TCA9548A データシート [2] p18

デバイスアドレス + コントロールレジスタと指定してアクセスするようです。

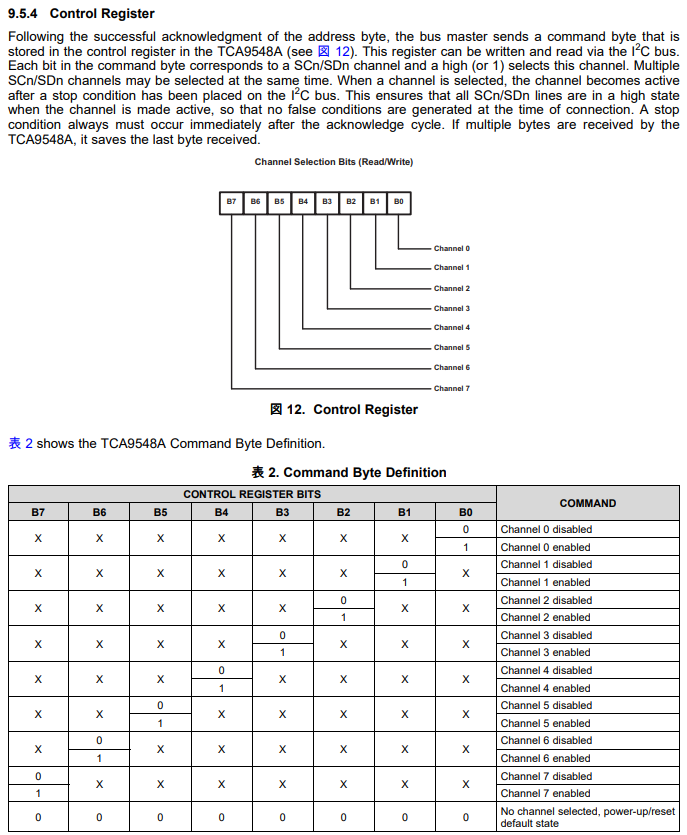

コントロールレジスタについては以下に記載があります。

※画像クリックで大きな画像が表示されます。

出典:TEXAS INSTRUMENTS TCA9548A データシート [2] p19

8チャネルそれぞれが1ビットずつ8bitでenable/disableを決めているようです。

これで今回アクセスするI2Cスイッチについてはわかりました。

レジスタ確認:Si570

次に変更する周波数(HSDP_SI570)を作っている部品を確認します。

まずデバイスアドレスを確認するため、VCK190の回路図 [3]を確認します。

p8のU5付近に「I2C Addr = 0x5D」と記載がありました。

これでデバイスアドレスが確認できました。

https://japan.xilinx.com/products/boards-and-kits/vck190.html

- ※

- リンク内のXTP610から回路図データがダウンロードできます。

ダウンロードには、アカウント登録が必要となります。

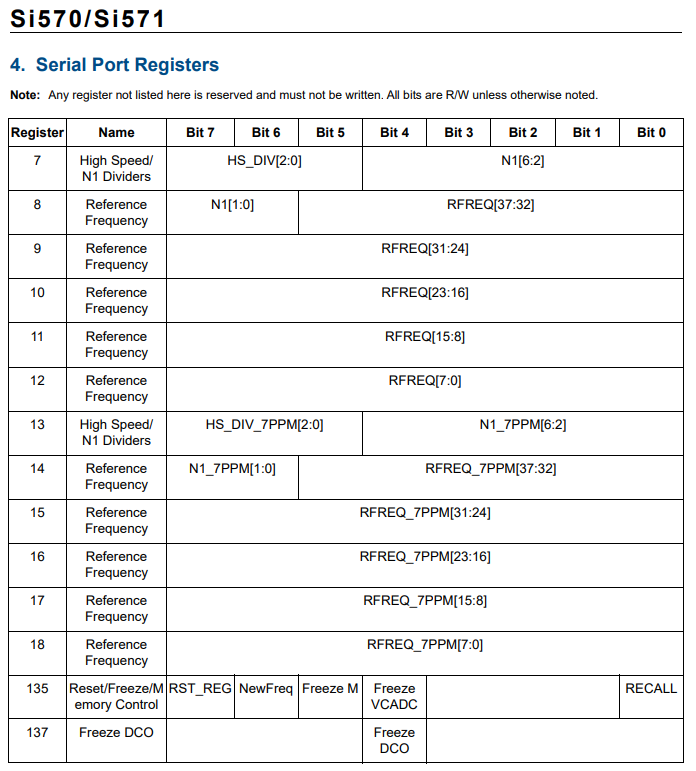

次にレジスタを確認するため、Si570のデータシート [4]を確認します。

※画像クリックで大きな画像が表示されます。

出典:SKYWORKS SOLUTIONS, INC. Si570 データシート [4] p22

Register欄にアドレスが書かれています。

今回は、Register7のHS_DIVの値を切り替えたいと思います。

HS_DIVについても確認します。

※画像クリックで大きな画像が表示されます。

出典:SKYWORKS SOLUTIONS, INC. Si570 データシート [4] p14

これで確認は完了です。

実践

レジスタの確認が完了したので、実機確認に移ります。

VCK190に前回記事のデザインをSD Bootで起動させます。

次にUSBケーブル経由でシリアルアクセスし、Linuxが起動するのを確認します。

注意点①

今回は、VIOを使用するため、SD Boot後にltxファイルを追加で書き込む必要があります。

VivadoでDenerate Device Imageをした際、以下の階層にltx拡張子のファイルが生成されているため、Vivado Hardware Manegerからltxファイルを書き込みましょう。

ltxファイルの保存先

<project_name>/<project_name>.runs/impl1/<top>.ltx

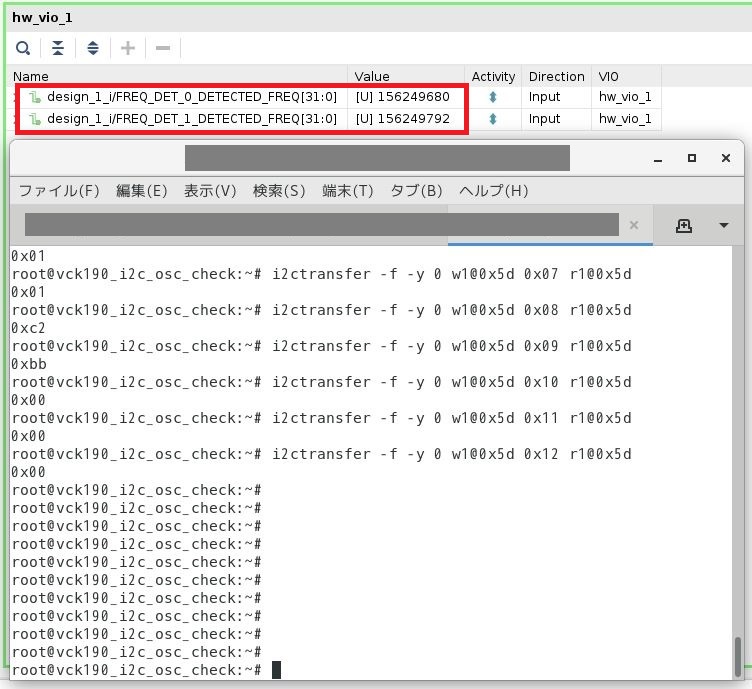

ltxファイル書き込み後の様子になります。

※画像クリックで大きな画像が表示されます。

出典:Vivado® ML Edition、シリアルコンソール画面

前回記事で、接続したzSFP_SI570_CLK_C_P/Nが上、HSDP_SI570_CLK_C_P/Nが下で それぞれ156.25MHzとなってます。

次にLinuxからI2C制御を行います。

TCA9548A (デバイスアドレス0x74)に1byteのリード要求を送ります。

# i2ctransfer -f -y 0 r1@0x74

0x01

-f:アクセス強制

-y:インタラクティブ無効

0:i2c-0を指す。i2cdetect -lで確認可能。

r1:リード 1byte

@0x74:デバイスアドレス

0x01が返ってきています。

TCA9548Aのコントロールレジスタを見る限りチャネル0だけが有効になっています。

今回は、チャネル6を有効にしたいので、0b01000000→0x40をライトします。

i2ctransfer -f -y 0 w1@0x74 0x40

i2ctransfer -f -y 0 r1@0x74

0x40

w1:ライト 1byte

先と同じリード要求で今度は、0x40が返ってきました。

書き込みが反映されています。

続けてSi570のレジスタ7の値をリードします。

i2ctransfer -f -y 0 w1@0x5d 0x07 r1@0x5d

0x01

0x01が返ってきました。

HSDIVは上位3bitなので、HSDIV=0b000のようです。

データシートを見る限り000=4となっているので、HSDIVは4のようです。

ではいよいよHSDIVの値を変更します。

今回はHSDIVを4→5に変更します。

HSDIVの値を5にするため、Si570のレジスタ7に0b00100001=0x21を送ります。

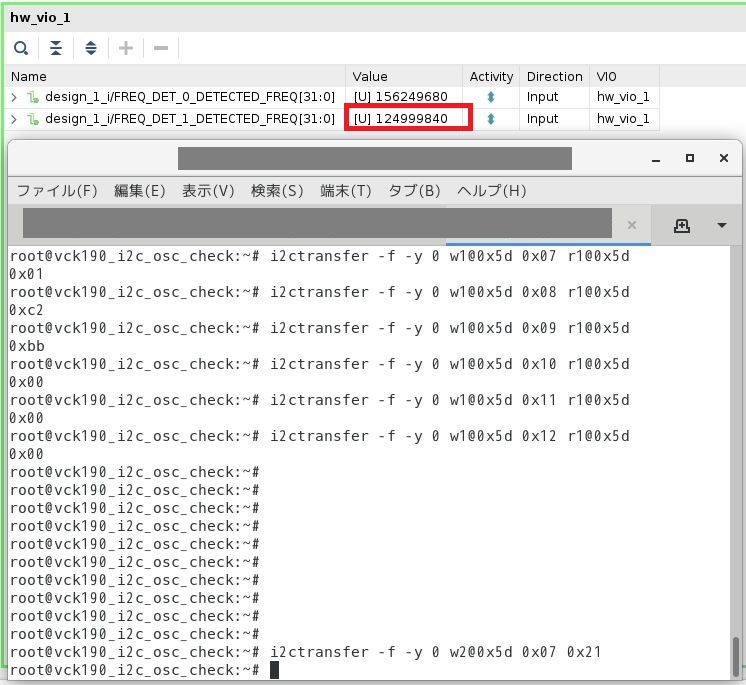

i2ctransfer -f -y 0 w2@0x5d 0x07 0x21折角なので、レジスタ読み出しではなく、VIO上で確認します。

※画像クリックで大きな画像が表示されます。

出典:Vivado® ML Edition、シリアルコンソール画面

VIO上のHSDP_CLKの値が変わりました。

HSDIVが4→5となり、周波数が4/5になるので、

156.25*4/5=125

となり計算も合います。

これでVCK190のOSC周波数をI2C制御で変更することができました。

おわりに

今回は、VCK190でI2C Example DesignでClock切り替えを行うための実機手順について解説しました。

デザインの準備については、前回記事をご覧いただければと思います。

別インターフェースのExampleデザインについても、ブログを通じてお伝えできればと思いますので、次回のブログもどうぞよろしくお願いいたします。

調査依頼や、設計検討などありましたら、お気軽にお問い合わせください。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

最後までお付き合いいただきありがとうございました。

- 参考文献

-

[1]Xilinx VCK190評価ボード ユーザーガイド(UG1366)

[2]TEXAS INSTRUMENTS TCA9548Aデータシート

[3]Xilinx XTP610 VCK190 Schematics

- ※

- リンク内のXTP610から回路図データがダウンロードできます。

ダウンロードには、アカウント登録が必要となります。