【Versal™ACAP】Targeted Reference Design Build 2021.1版

みなさんこんにちは。

以前のTECHブログでVersal™ AI コア シリーズ VCK190 評価キットのTargeted Reference Design(以下「TRD」)を紹介させていただきました。

【Versal ACAP】 Versal™ AI コア シリーズ VCK190 評価キットを動かしてみた【紹介動画付き】

TRDのダウンロードはこちらから (※ダウンロードにはザイリンクス アカウントが必要です。)

https://japan.xilinx.com/member/forms/download/design-license-xef.html?filename=rdf0610-vck190_base_trd_platform1_2020.2_v0.5.zip

しかし、TRDのダウンロードリンクがGitHubからのダウンロードへと変わっており、以前のリンクではダウンロードできなくなっています。

改めて確認したところ新機能などもありましたので、概要の説明とBuildしてみた上での注意点を解説いたします。

それでは、始めましょう。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

目次

今回は、以下の環境で実行します。

- ・CentOS 7.6

- ・Vivado®2021.1

- ・Vitis®2021.1

- ・Petalinux®2021.1

- ・CentOS 7.6

- ・Vivado®2021.1

- ・Vitis®2021.1

- ・Petalinux®2021.1

TRDについて

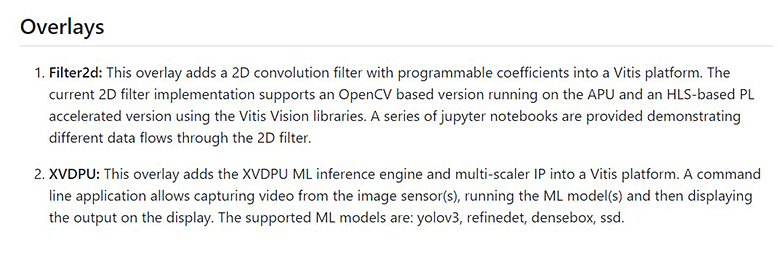

以前の記事 では4KのHDMIモニター出力や、2次元畳み込みフィルターの動作についてふれましたが、現在のTRDにはXVDPUという機能が含まれているようです。

出典:GitHub Xilinx/vck190-base-trd

https://github.com/Xilinx/vck190-base-trd (参照 2021/12/24)

MIPIカメラの映像データに対してMLモデルを適用してHDMIに出力することができるといった内容のようです。

追加内容について確認したかったのですが、今回は周辺インターフェースの都合上、動作を確認できずお見せすることができないため、詳細については割愛させていただきます。

ダウンロード時の注意点

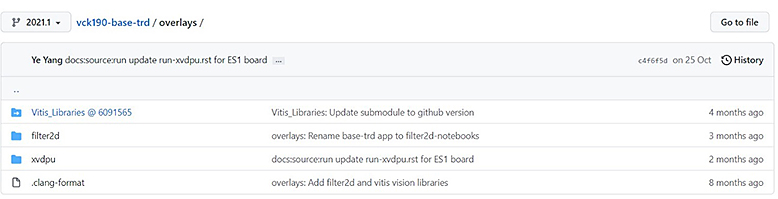

それでは、TRDをBuildするためにGitHubからダウンロードを行います[1]。

https://github.com/Xilinx/vck190-base-trd

※GitHubからダウンロードをする場合

vck190-base-trd/overlays/Vitis_Librariesが参照リンクになっており 参照リンク先もあわせてダウンロードをしていない場合は Buildの途中でエラーで停止してしまうため注意しましょう。

出典:GitHub Xilinx/vck190-base-trd

https://github.com/Xilinx/vck190-base-trd/tree/2021.2/overlays (参照 2021/12/24)

今回はLinuxでBuildするため、Versal Base TRD Documentation[2]に従って、端末から以下のコマンドでダウンロードします。

https://xilinx.github.io/vck190-base-trd/2021.1/html/index.html

$git clone --branch 2021.1 --recursive https://github.com/Xilinx/vck190-base-trd.gitPhase4.5 Petalinux Buildの注意点

その後は手順通りにPhase4.2, 4.3, 4.5にてmakeコマンドを実行していくのですが、Phase4.5 Petalinux Buildにて以下のようなエラーに遭遇したため、注意点として残しておきます。

fatal error: 'common/xf_common.hpp' file no found.

こちらについてですが、

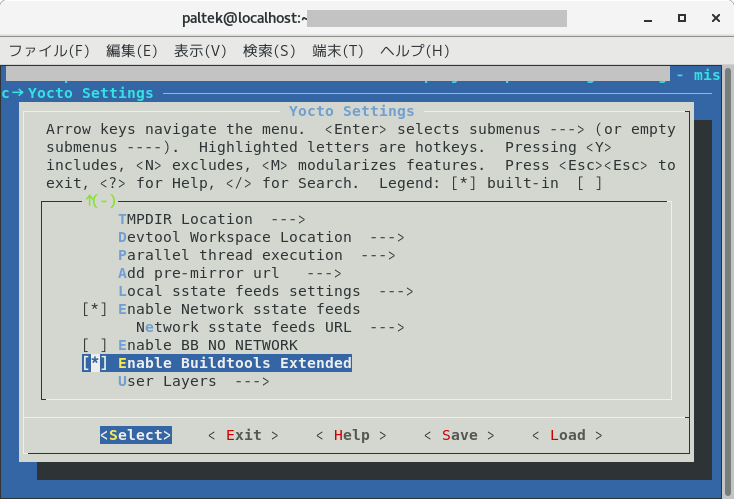

「Please enable buildtools Extended in petalinux-config --> yocto settings」を試してみました。

$cd working_dir/petalinux/xilinx-vck190-base-trd/images/linux/

&petalinux-config以下のGUIです。

[ * ] Enable Buildtools Extended を有効にします

出典:Petalinux設定画面(参照 2021/12/24)

これにより、gccなどのツールチェーンがインストールされるようになっているようです。

この対応後、改めてmakeコマンド実行するとエラーなく最後まで進むことができました。

動作については、以前のブログで紹介した内容と比べて大きな変化はありませんでした。

ご興味のある方は、

【VERSAL ACAP】 Versal™ AI コア シリーズ VCK190 評価キットを動かしてみた【紹介動画付き】 をご参照ください。

おわりに

今回は、VCK190 Base TRDのダウンロード先の変更とBuild時の注意点について解説しました。

XVDPUについても紹介したかったのですが、今回は周辺インターフェースの都合で割愛させていただきました。

準備でき次第、ブログを通じてお伝えする予定ですので、次回のブログもどうぞよろしくお願いいたします。

調査依頼や、設計検討などありましたら、弊社デザインサービス事業までお気軽にお問い合わせください。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

最後までお付き合いいただきありがとうございました。

- 参考文献

-

[1] Xilinx vck190-base-trd

https://github.com/Xilinx/vck190-base-trd[2] VCK190 Base TRD Documentation

https://xilinx.github.io/vck190-base-trd/2021.1/html/index.html

関連ブログ

- 【Versal ACAP】 Versal™ AI コア シリーズ VCK190 評価キットを動かしてみた【紹介動画付き】

Versal™についての簡単な紹介を交えつつ、最新の基板にすぐ触れたい方や実際に動いている様子を知りたい方へ「実機動作の様子」と「動作させるための手順」について解説します。

- 【Vivado® ML Edition 2021.1】を使ってVCK190 評価キットのプロジェクトを作成してみた

ツールインストールした後、Versal™ AI コア シリーズ VCK190 評価キットのシンプルなプロジェクトを作成し、書き込みしましたので、その内容についてお知らせします。

- 【Vivado® ML Edition 2022.1】をインストールしてVCK190 評価キットのプロジェクトを作成してみた

今回は、Vivado® ML Edition 2022.1をインストールした後、VCK190評価キットのシンプルなプロジェクトを作成し書き込みしてみます。

その他の関連ブログ

Example Design関連シリーズ

【Versal™ACAP】機能紹介シリーズ