【ModelSim®使用方法】ModelSim®単独で使用する場合のVivado® IPライブラリの特定と設定方法

皆さん、こんにちは。

ModelSim®でシミュレーションを行う際、デザインの中にVivado®のIPがあるとデザインの他にライブラリも設定しないといけないですよね。

Vivado®でシミュレーションを行う場合や、Vivado®からサードパーティーのシミュレーションツールを起動する場合には自動でライブラリも設定されたりしますが、ModelSim®だけで環境構築するには必要なライブラリを手動で設定しないといけません。

そこで今回は、

- 普段はASICの設計でほとんどFPGAは使わない方

- 設計を初めたばかりの方

に向けてどのライブラリを特定・設定すればよいかのヒントをお届けしたいと思います。

今回紹介する設定方法は、シミュレーションライブラリがコンパイルされていることが前提となります。

ライブラリのコンパイルをまだされていらっしゃらない方は、こちらをご参考いただきライブラリをご用意ください。

【ModelSim®使用方法】ModelSim®単独で使用する場合のVivado® ML Edition IPライブラリの設定方法

なお、IPの種類は非常に多く、多岐にわたるため、論理シミュレーションで必要なものにフォーカスして説明します。

それでは、はじめましょう。

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。

目次

生成したIPの確認

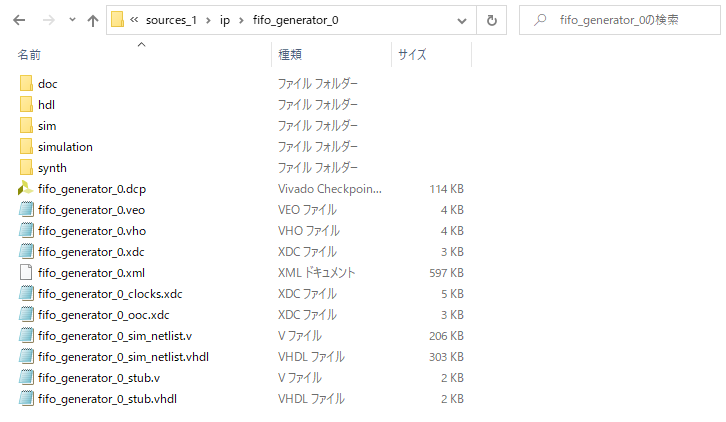

Vivado®のターゲット言語を「Verilog」に設定し、「fifo_generator_0」というマクロ名でFIFOを作成しました。

環境などによりますが、以下のような場所に各種ファイルが生成されます。

- /project_1.srcs/sources_1/ip/fifo_generator_0 または

- /project_1.gen/sources_1/ip/fifo_generator_0

の中に、ラッパー用のHDLファイル(.veo/.vho)やタイミング設定ファイル(.xdc)などなどができています。

出典:Windows®エクスプローラー画面 (参照 2023/06/27)

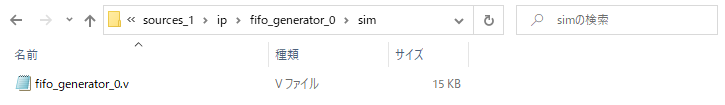

/sim の下にはシミュレーション用のHDLファイルができています。

出典:Windows®エクスプローラー画面 (参照 2023/06/27)

/synth の下には論理合成用のHDLファイルができています。

出典:Windows®エクスプローラー画面 (参照 2023/06/27)

シミュレーション実行

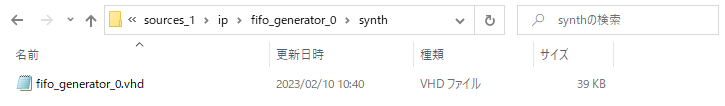

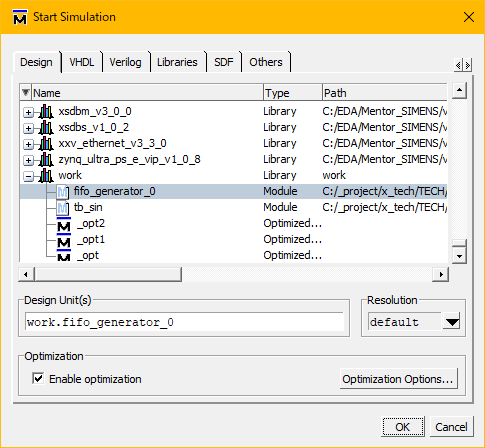

何も考えず、「fifo_generator_0」をシミュレーションのトップファイルとして実行してみます。

出典:ModelSim® SE-64 2021.03 Start Simulation画面 (参照 2023/06/27)

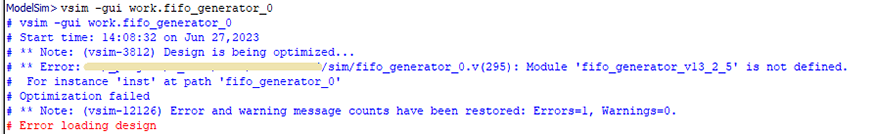

実行後のログを見ると

出典:ModelSim® SE-64 2021.03 Transcript画面 (参照 2023/06/27)

モジュールが足りないということで、エラーになりました。

シミュレーション用HDLファイルの確認

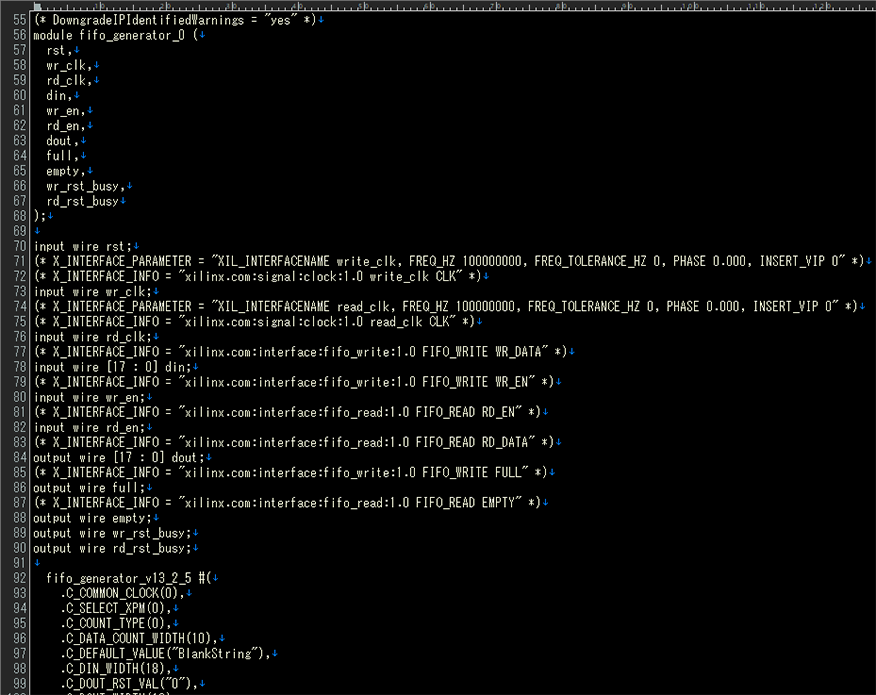

今回はVerilogに設定しているため、.vファイルが生成されています。

出典:Vivado® 2020.2 IP生成ファイル fifo_generator_0.v (参照 2023/06/27)

/sim/fifo_generator_0.v の92行目に「fifo_generator_v13_2_5」というモジュールが呼び出されています。

これがシミュレーションの時に必要なライブラリになります。

実は先ほどエラーで表示されていたモジュール名がライブラリでした。

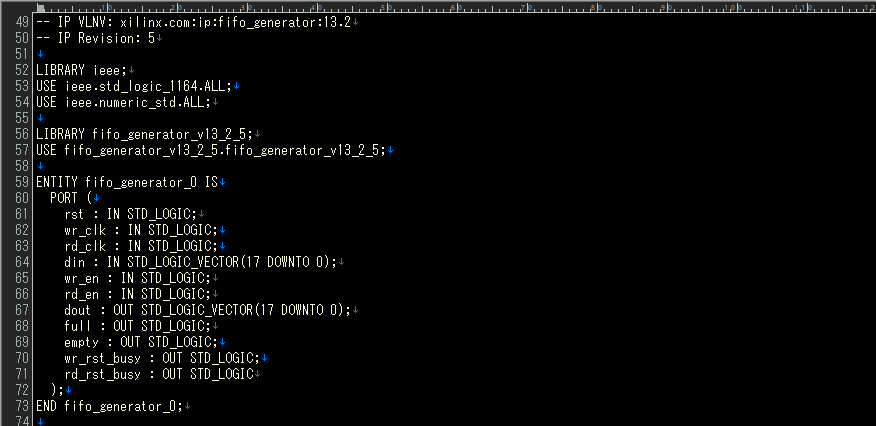

論理合成用ファイルの確認

ターゲット言語をVerilogに設定していますが、IPによっては別の言語で生成されることがあります。

今回はVHDLでファイル生成されていますが、これは変更することができません。

出典:Vivado® 2020.2 IP生成ファイル fifo_generator_0.vhd (参照 2023/06/27)

/synth/fifo_generator_0.vhdの56行目に

「LIBRARY fifo_generator_v13_2_5」と、ライブラリが宣言されています。

シミュレーションの時もこれと同じライブラリが使われるので、必要なライブラリがわかります。

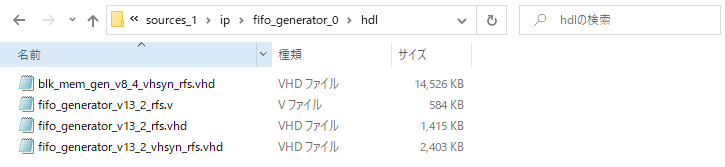

他ファイルの確認

他のファイルも確認してみましょう。

/hdl というディレクトリがありますが、ここには暗号化されたRTLファイルが作られています。

出典:Windows®エクスプローラー画面 (参照 2023/06/27)

実はファイル名のバージョンの数字までがライブラリ名になります。

- fifo_generator_v13_2_rfs.v

- blk_mem_gen_v8_4_vhsyn_rfs.vhd

のファイル名から

- 「fifo_generator_v13_2」

- 「blk_mem_gen_v8_4」

の2つのどちらか、もしくは両方が作成したIPで必要になるライブラリになります。

今回作成したFIFOのIP「fifo_generator_0」で必要ライブラリでは、「fifo_generator_v13_2」ということが分かりました。

それでは実際にシミュレーションで設定してみましょう。

シミュレーションファイルの実行

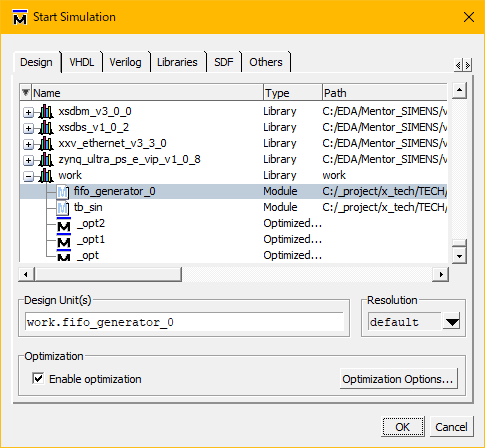

作成したテストベンチ、IP、ライブラリを設定し、シミュレーションを実行してみましょう。

Simulate → Start Simulate → 設定ウインドウが開きます。

Designタブの Design Unit にテストベンチのトップマクロを指定します。

出典:ModelSim® SE-64 2021.03 Start Simulation画面 (参照 2023/06/27)

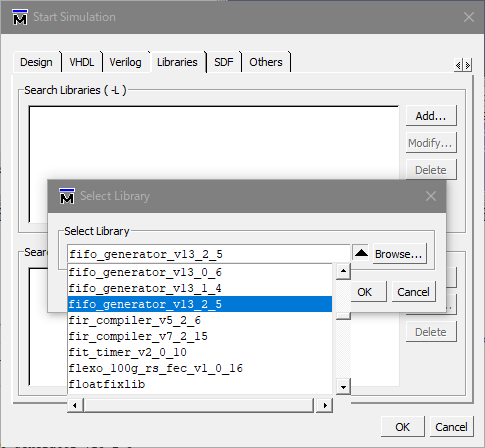

Librariesタブの上側 Search Libraries(-L) でAdd を押します。

▼マークを押して必要なライブラリ(今回の例では fifo_generator_v13_2_5)を探しOKを押します。

出典:ModelSim® SE-64 2021.03 Start Simulation画面 (参照 2023/06/27)

他に必要なライブラリがあれば、これを繰り返してライブラリを追加していき、設定が終わったらOKを押して実行します。

ライブラリの不足や他に問題がなければシミュレーションが実行されます。

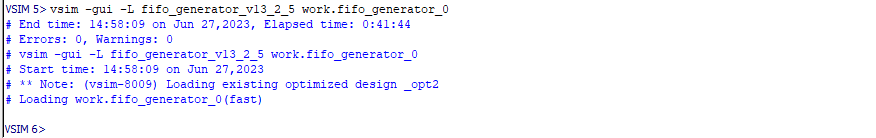

出典:ModelSim® SE-64 2021.03 Transcript画面 (参照 2023/06/27)

なお、シミュレーションを始める度にGUIでライブラリの設定をするのは面倒かと思います。

ModelSim®はGUIから実行した内容は、Transcriptにコマンドとして表示されますので、実行した内容をコピーしておけば、次回はTranscriptに貼り付けて実行するだけで同じように動作させることができます。

vsim -gui work.fifo_generator_0 -L fifo_generator_v13_2_5

-L から後ろが設定したライブラリになります。

必要なライブラリが見つからない場合

BUFGやMMCM(PLL)などのプリミティブは、HDLファイルにライブラリの情報が含まれていないものがあります。その場合には unisim(Verilogの場合には unisims_ver)に含まれているかもしれません。

もし、エグザンプルデザインがある場合には、そのコンパイルマクロ(バッチファイルやTcl)を覗いてみるとよいでしょう。

AMD社のAnswer Recordについて

AMD社のAnswer Recordに、各種シミュレーションライブラリに関する説明があるので一部を紹介しておきます。

AR# 64052: Vivado シミュレーション ライブラリの使用 - UNISIM ライブラリ

AR# 64055: Vivado シミュレーション ライブラリの使用 - SIMPRIM ライブラリ

AR# 64059: Vivado シミュレーション ライブラリの使用 - UNIMACRO ライブラリ

いかがでしたか?

いろいろな場所にヒントがあることがお分かりいただけたかと思います。

最後までご覧いただきましてありがとうございました!

これからもTECHブログを通じて、皆様の設計にお役立てできればと思います。

次回のブログもどうぞよろしくお願いいたします。

弊社ではModelSim®のセミナーを行っています。ご興味のある方は下記URLをご覧ください。

ModelSim®セミナー

ご興味のある方は下記ページもご覧ください。

ModelSim®関連セミナー/ブログ一覧はこちらをご覧ください

ModelSim/Questaは、多くのエディション/グレードが存在しお客様の用途に合わせ柔軟な選択が可能です。

ModelSim/Questa エディション比較表はこちらをご覧ください

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。