FPGA開発におけるデバッグ効率化!ECO(Engineering Change Order)の活用術

Vivado™ でFPGAの開発において、デザインの一部分のみを変更してデバッグを行いたい場合、「デザイン変更をして、実機確認を行うまで時間がかかる」と感じたことはありませんか?

この悩みを解決できるのが「ECO:Engineering Change Order」です。

この記事ではECOの特徴や使用するメリットを初心者の方でもイメージできるように説明します。

ECOの概要

ECOとは、配置・配線済みのネットリストを変更することで、元デザインへの影響を最小限に抑えて変更を反映するために使用します。

ネットリストの変更箇所のみを再配置・配線することで、短時間で変更を実装し、確認できます。

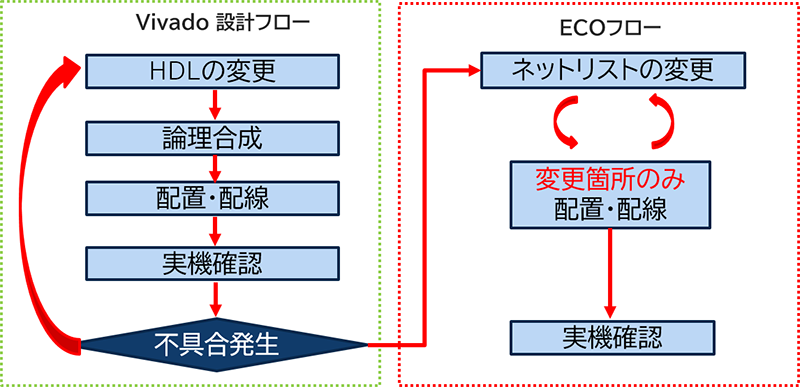

下図は、デバック時のVivado™ の設計フローとECOを使用したフローの比較イメージです。

「Vivado™ 設計フロー」では実機確認で不具合が発生した場合、HDLの変更まで遡って合成・配置・配線を行い、再度、実機確認を行う必要があります。

不具合原因が明確な場合は問題ありませんが、明確でない場合、何度もカットアンドトライをすることになり、デバッグに要する時間が膨大になる可能性があります。

一方、ECOフローでは、変更箇所のみを配置・配線でき、ネットリストを直接変更するため論理合成が不要です。

また、変更箇所のみが実機確認の結果に影響するため、不具合原因の特定が容易になります。

これにより、実機確認までの時間が大幅に短縮されデバッグに要する時間を削減できるため、開発効率の向上が可能です。

次にECOの使用例を1つ紹介します。

ECOの使用例

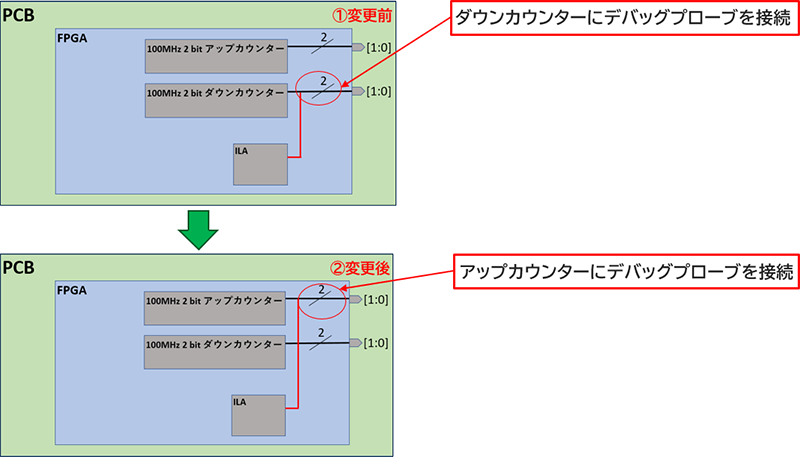

ILAのデバッグプローブの組み換え

この使用例では配線のみの変更になるため、変更した配線に対して再配線を行うだけです。

表1からわかるように、ECOを使用することで「論理合成」、「配置」のステップを省略でき、実機確認までに必要な時間を短縮することが可能です。

| 使用例における各ステップの処理時間 | 論理合成※1 | 配置 | 配線※2 | 合計 |

|---|---|---|---|---|

| Vivado™ 設計フロー | A | B | C | A + B + C |

| ECO | 0 | 0 | D | D |

※1 Vivado™ 設計フローでもILAをネットリスト挿入する場合、論理合成(A)は不要です。

※2 ECOでは、変更箇所のみ再配線されるため、CとDの処理対象は異なります(C≠D)。

資料ダウンロード

さらにECOの活用方法にご興味をお持ちの方へ、今回紹介した使用例に加え、以下の使用例について詳しく説明した資料をご用意しております。ぜひご活用ください。

- デバッグ用プローブの置換方法

- デザインのネット接続変更手順

- タイミング改善評価の進め方

- IOB(入出力ブロック)の設定・変更方法

まとめ

ECOの特徴やメリットはご理解いただけましたでしょうか?

ECOは変更箇所のみを配置・配線することができるため、以下の2点より効率的なデバッグを実現します。

- 「デバッグ → デザインの変更 → 実機確認」という一連のサイクルを大幅に短縮可能

- 変更箇所のみが実機確認の結果に影響するため、不具合原因の特定が容易

これにより、デバッグ作業に必要な時間・人員のコストを大幅に削減することができ、製品の出荷スケジュールに合わせて、迅速かつ確実なデバッグを実行可能です。

ECOの活用により、皆様のデバッグ業務がより快適になれば幸いです。

最後までご覧いただきありがとうございました。