メモリ基本講座「LPDDR5/5Xとは何ぞや?~機能編①~」

本ブログでは、前回の概要編に続き、LPDDR5/5Xの主要な機能について、「機能編」として詳しく解説していきます。

1.LPDDR5の性能・電力効率改善

LPDDR5は低消費電力を追求するため、従来のLPDDR4/4Xと比較して大幅な性能向上と電力効率の改善を実現しています。エネルギー効率を向上させるため多くの革新的な新機能が追加されており、これらの機能は、システム全体のパフォーマンス最適化を目的として設計されています。

2.FSP操作

LPDDR5のFSP(Frequency Set Point)は、自動車の「ギア」に相当する動作点を定義します。高負荷時には高いギアで性能を確保し、低負荷時には低いギアへ切り替えることで、システム要求に応じた効率的な動作点制御を実現し、全体の消費電力削減に貢献します。

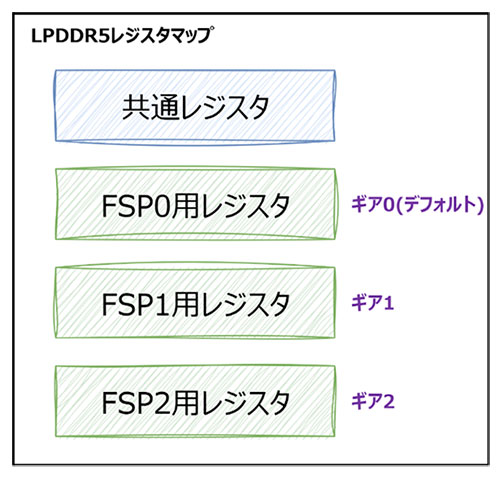

LPDDR5デバイスは、最大3つのFSP(FSP0/1/2)をサポートしていますので、タイミングパラメータ、Vref・ODT設定、トレーニング関連レジスタ(MR1、MR2、MR10など)もそれぞれ3セットで用意されています。

電源投入後の初期化シーケンスにて、コントローラは各FSPに対してトレーニングを行います。LPDDR5は事前に設定済みのFSP間を再トレーニングなしで高速で切り替えることができます。

レジスタMR16[1:0]はFSP設定レジスタ対象領域を設定できます。

| MR16 OP[1:0] | FSP-WR Symbol | FSP0用レジスタ | FSP1用レジスタ | FSP2用レジスタ |

|---|---|---|---|---|

| 00b | FSP-WR[0] | Write/Read | アクセス不可 | アクセス不可 |

| 10b | FSP-WR[1] | アクセス不可 | Write/Read | アクセス不可 |

| 11b | FSP-WR[2] | アクセス不可 | アクセス不可 | Write/Read |

3.DVFSC、EDVFSC、DVFSQ

DVFS(Dynamic Voltage and Frequency Scaling)はFSPを基盤として、動作状況に応じて電圧および周波数を動的に制御することで、消費電力を効率的に削減する技術です。モバイル機器では利用シーンが多様化しており、常に一定の電圧・周波数で動作させることは現実的ではありません。そのため、DVFSは省電力設計において重要な役割を担っています。

LPDDR5のDRAMデバイスにおいても、コアおよびI/O電源を対象としたDVFS機能がサポートされています。

以下では、LPDDR5における3種類のDVFS機能について簡単に紹介します。

DVFSC(Dynamic Voltage and Frequency Scaling Core)

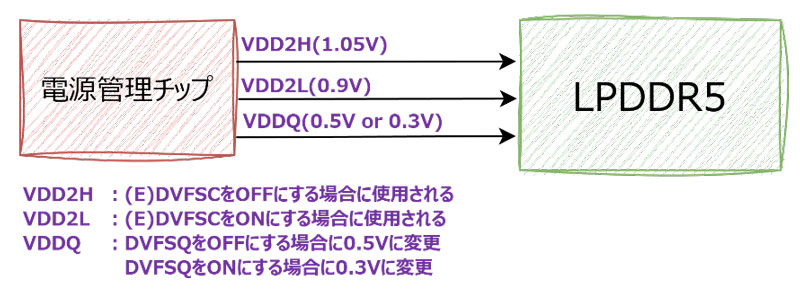

DVFSCは、コア電源(VDD2)と動作周波数を動的に切り替える機能です。動作負荷に応じて最適なFSPを選択することで、性能と消費電力のバランスを効率よく制御します。初期化時に対応モードを設定し、動作中に切り替えて使用します。

DVFSCを有効にすると、VDD2電圧はVDD2H(1.05V)からVDD2L(0.9V)になります。シングルVDD2レールではVDD2Lは1.05Vなので省電力効果がありません。対応データレート40Mbps~1600Mbpsです。

EDVFSC(Enhanced DVFSC)

EDVFSCはDVFSCの拡張機能であり、LPDDR5Xのみでサポートされます。DVFSCと同様にVDD2を対象としますが、DVFSCよりも高いデータレート領域まで低電圧動作を適用でき、高速動作時においてもコア消費電力の削減が可能です。基本的な使用方法はDVFSCと同様です。対応データレート40Mbps~3200 Mbpsです。

DVFSQ(VDDQ Dynamic Voltage and Frequency Scaling VDDQ)

DVFSQは、I/O電源(VDDQ)を対象とした動的電圧・周波数制御機能です。データレートに応じてVDDQ電圧を切り替えることで、I/O動作時の消費電力を低減します。DVFSQ使用時には、JEDEC規格に基づき、外部電源によってVDDQ電圧を0.5Vから0.3Vへ変更します。

4.Deep Sleep

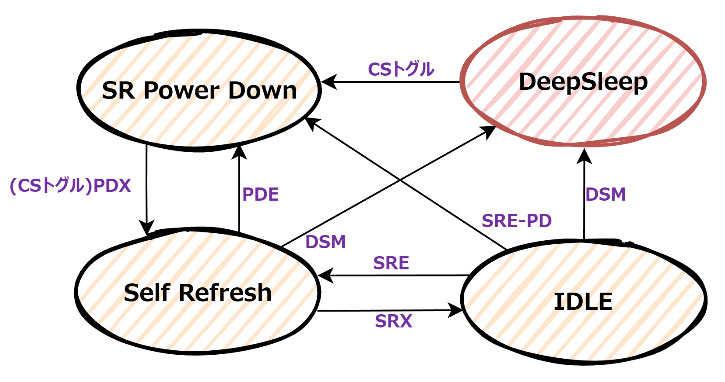

Deep Sleep(以下略称DS)は、LPDDR5において新たに追加された低消費電力状態であり、Self Refresh(以下略称SR)により約5.5%の消費電力削減を実現し、LPDDR5における最小消費電力状態です。

下図は消費電力モード遷移図となります。

IDLEとSRからは、DSコマンドでDSに入ります。Self Refresh Power Down(以下略称SRPD)からは直接的にDSに入れず、いったんSRに戻ってからDSに入ります。

DSは自動リフレッシュの拡張版で、より低い消費電流を実現するために内部回路を制御します。DSに切り替えた後、電力削減効果を得るためには、少なくとも tPDN_DSM=4ms 以上の時間、当該モードを維持する必要があります。短時間で終了しても動作は可能ですが、消費電力低減効果はほとんどありません。SRPDは短時間の低消費電力待機に向いており、DSMは退出に時間がかかる代わりに、長時間待機でより低い消費電力を実現します。

5.Write X

Write Xは「メモリに特定のパターン(ALL0、ALL1)を書き込む命令」で、ホスト側からデータ送信を減らして省電力化を実現するための仕組みです。メモリクリア処理で全て0による初期化を行う場合やデータバッファを特定パターンで埋める処理、さらにはグラフィックス処理における単色塗りつぶし操作など、同一パターンの大量書き込みが発生する場面で活用できます。これらの処理においてWrite X機能を使用することで、従来の書き込み方式と比較して消費電力を大幅に削減することが可能になります。

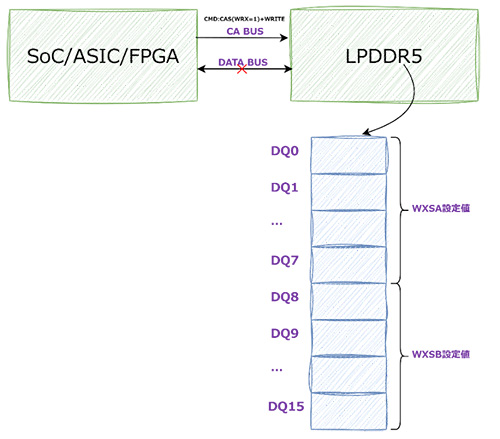

コントローラはMRWコマンドを使用してWrite X機能を有効にできます。WRITE Xコマンドは、CASコマンドに続いてColumnアドレス付きのWRITEコマンドで構成されます。

下表はWrite XのCAS Command表です。

| Command | CS | CA0 | CA1 | CA2 | CA3 | CA4 | CA5 | CA6 | CK |

|---|---|---|---|---|---|---|---|---|---|

| CAS | H | L | L | H | H | V | V | V | R1 |

| X | DC0=0 | DC1=0 | DC2=0 | DC3=0 | WRX | WXSA | WXSB | F1 |

WRXを1に設定することで、WRITE X動作が有効になります。WXSAはDQ[7:0](下位バイト)のパターンを制御し、WXSBはDQ[15:8](上位バイト)のパターンを制御します。

下図はWrite X機能動作イメージとなります。Write X機能が動作する際に、データバスを使わずに、WXSAとWXSBの設定値に基づいてメモリデバイス内部でデータパターンが生成されます。これにより、従来の書き込み動作で必要だったデータバスの駆動電力が不要となり、システム全体の消費電力を大幅に削減することができます。

6.Data Copy

Data Copy機能は、8バイトを最小判定単位としてデータパターン繰り返し性を識別し、I/Oおよびコア消費電力(IDD4W, IDD4R)を大幅に削減する機能です。この機能は通常の読み書き時に自動で動作し、データパターンを検出します。読み取り機能有効化時には読み取りレイテンシが増加する可能性があるものの、繰り返しパターンを持つ大量データ処理時に顕費電力削減効果を提供します。

Data Copyは以下の2種類があります。

- Write Data Copy

- Read Data Copy

Write Data Copy

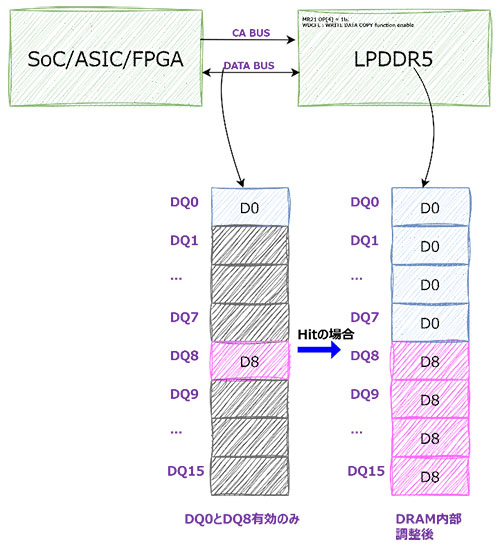

下図は、LPDDR5のWrite Data Copy機能の動作イメージを示しています。

8バイト単位で同一データパターンが繰り返される場合、通常はDQ0~DQ15の全16本のデータラインを駆動して書き込みを行いますが、Write Data Copy機能を使用すると、下位バイト用のDQ0と上位バイト用のDQ8の2本のみで参照データを送信し、送信されたデータはLPDDR5デバイス内部で他のDQラインへ自動的にコピーされ、最終的にDQ0~DQ7はD0、DQ8~DQ15はD8という同一パターンが生成されます。

Write Data Copy機能を使用すると、下位バイト用のDQ0と上位バイト用のDQ8の2本のみで参照データを送信します。送信されたデータはLPDDR5デバイス内部で他のDQラインへ自動的にコピーされ、最終的にDQ0~DQ7はD0、DQ8~DQ15はD8という同一パターンが生成されます。

このように、駆動するデータライン数を16本から2本に削減できるため、データバスの消費電力を大幅に低減することが可能です。特に、メモリクリアや単色塗りつぶしといった処理では、高い省電力効果を発揮します。

Read Data Copy

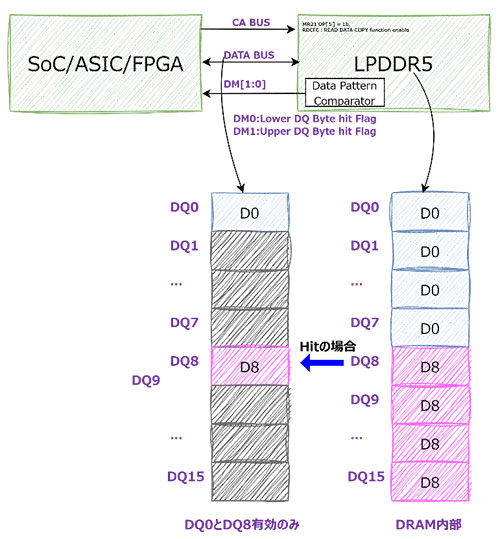

下図は、LPDDR5のRead Data Copy機能の動作イメージを示しています。本機能では、LPDDR5デバイス内部のData Pattern Comparatorを用いて、8バイト単位でデータパターンの繰り返しを検出します。

繰り返しパターンが検出された場合、デバイスは下位バイト用のDQ0と上位バイト用のDQ8のみで参照データを出力します。同時に、DM0およびDM1ピンを通じて、ヒット/ミスのフラグ情報をホスト側へ通知します。ヒット時には、その他のDQライン(DQ[7:1]、DQ[15:9])をLOWレベルに固定することで、通常の読み出し動作と比べてデータバスの駆動電力を大幅に削減します。

ホスト側では、受信した参照データとフラグ情報を基に元の8バイトデータを復元できるため、読み出し処理全体の電力効率を向上させることが可能です。

7.PARC機能

PARC(Partial Array Refresh Control)は、実際に使用されていないDRAM領域が多い場合に、未使用セグメントのリフレッシュを抑制することでリフレッシュ動作時の消費電力(IDD5)を削減するための機能です。

該当機能は8 Bank Base Refresh構成を採用しており、各Bankは8セグメントに平均的に分割されています。

PARC有効時には、各セグメントごとにRefreshの有効・無効を設定でき、All-Bank/Per-Bank REFRESHコマンドにおいても、マスクされたセグメントはRefresh対象から除外されます。ただし、PARC機能を使用する際にメモリコントローラ側でアドレス管理が適切に行われていないと、重要なデータが失われる可能性がありますのでご注意ください。

まとめ

本ブログでは、LPDDR5において新たに導入・強化された消費電流削減に関する各種機能について紹介しました。

FSPをベースとしたDVFSC/DVFSQによる動作点制御、Deep Sleep Modeによる待機時電流の低減、さらにWrite XやData Copy機能によるデータバス駆動の最小化など、LPDDR5ではシステムの動作状況に応じて電力を効率的に削減するための仕組みが多層的に用意されています。

これらの機能は、単にピーク性能を追求するのではなく、実際のユースケースにおける平均消費電力をいかに下げるかという観点で設計されている点が、LPDDR5/5Xの大きな特徴と言えるでしょう。

導入や評価に関するご相談、製品の詳細仕様についてのご質問は、下記よりお問い合わせいただけます。