メモリ基本講座【番外編】LPDDR4の特徴と基板設計上の注意点

本ブログでは、LPDDR4について話をしていきます。

LPDDR4とはDDRメモリの派生規格として開発された規格で、最新ではLPRDDR5まで規格が発表されています。

本ブログでは、LPDDR4における消費電流についての考え方や設計上の注意点についてお話しします。

それでは始めましょう。

-

皆さまこんにちは!メモリ博士ちゃんです!

本ブログでは、LPDDR4の特徴と基板設計上の注意点について紹介します。

目次

- 1. LPDDR4とその特徴

- 2. LPDDR4消費電流についての考え方について

- 3. LPDDR4基板設計上の注意点

- 4. コラム

- 5. おわりに

1. LPDDR4とその特徴

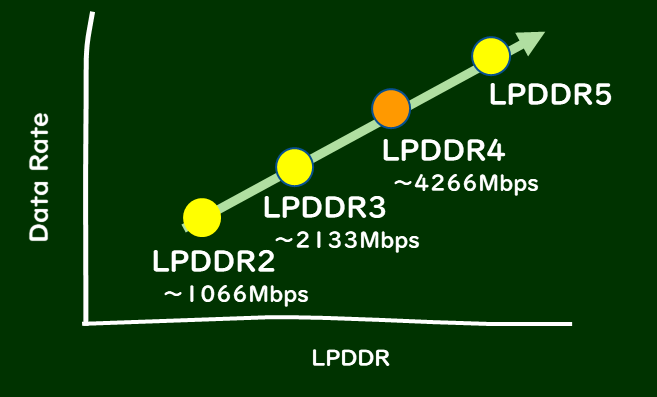

LPDDRはLow Power DDRメモリのことで、DDRメモリの派生規格として開発されました。2009年にLPDDR2の規格が発表されてから、最新のLPDDR5まで製品開発が行われており、製品の世代が交代する度に、低電圧化、高速化が図られてきました。

LPDDR系の製品ですが、低消費電力の特徴を活かし、当初はバッテリ駆動の製品を中心に採用されてきましたが、最近ではバッテリ駆動以外の各種産業機器やエッジコンピューティングで採用されている事例も多く見られます。

それではここからはLPDDR4の特徴について説明します。

LPDDR4の特徴について

① Low Power

電源電圧のVDDはDDR4、LPDDR3より低下されており、LPDDR4はVDD1=1.8V, VDD2=1.1V, VDDQ=1.1Vに対し、DDR4はVDD=VDDQ=1.2V, VPP=2.5Vになります。

LPDDR3はVDD1=1.8V, VDD2=1.2V, VDDQ=1.2Vになるため、LPDDR4はより低消費電力製品ということが分かります。さらにLPDDR4よりDQ DriverのPowerを低下させたLPDDR4xの製品もリリースされており、VDD1=1.8V, VDD2=1.1V, VDDQ=0.6Vになります。

② Performance

データレートは最大でLPDDR3の2倍の4266Mbpsで、ピークのバンド幅はDDR4より33%向上しています。

2. LPDDR4の消費電流についての考え方について

ここからはLPDDR4を使って製品開発を行う上で、参考となる内容について紹介します。

LPDDR4の消費電流を見積もる上でのポイントは、データシートに記載されている内容を正しく理解することと、実際の使用条件に合わせて消費電流を見積もることの2つになります。

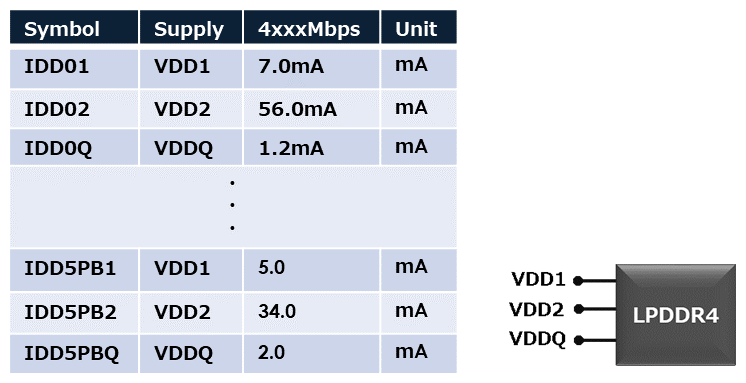

最初にメモリのデータシートに記載されている消費電流の部分について説明します。データシートには実に数十もの項目についてスペックが規定されていますが、Read時、Write時、Stand-by時といったようにメモリの動作毎に分けてスペックが記載されています。

さらに、LPDDR4の電源系統にはVDD1、VDD2、VDDQの3系統の電源がありますが、それぞれの電源系統毎に分かれてスペックが規定されています。動作状態、電源系統毎に分けて記載されていることが数十にも及ぶ項目となっている要因となっています。

続いて、電源電圧に関する内容ですが、データシートには推奨動作電圧範囲としてスペックが規定されていますが、消費電流の部分に記載されているデータは、推奨動作電圧範囲のMax値で記載されていることに注意が必要です。

表1. 推奨動作電圧範囲

| Symbol | Min. | Typ. | Max. | Unit |

|---|---|---|---|---|

| VDD1 | 1.70 | 1.8 | 1.95 | V |

| VDD2 | 1.06 | 1.10 | 1.17 | V |

| VDDQ | 0.57 | 0.60 | 0.65 | V |

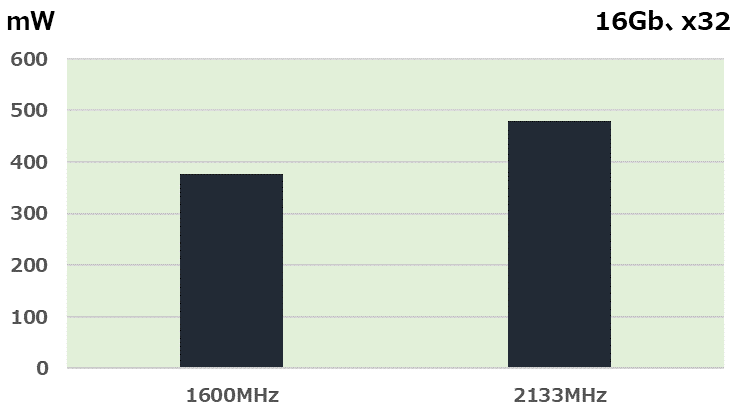

また、動作周波数についても、データシートには代表的な動作周波数での電流値が記載されていますが、動作周波数によって電流値も異なってきますので、実際に使用する動作周波数での電流を見積もる必要があります。

参考までに、動作周波数の違いによる消費電流の違いですが、クロックの周波数が1600MHzから2133MHzになった場合、LPDDR4の消費電流は約28%増加することになります。

図1. LPDDR4動作周波数による比較

3. LPDDR4基板設計上の注意点

続いての基板設計を行う上での参考となる情報について紹介します。

LPDDR4のように高速で動作するデバイスを使用した基板設計を行う際には、ノイズや歪等の影響を考慮する必要がありますが、それ以外にも、最適な電源ICとコンデンサを選択すること、また設計段階で基板シミュレーションによる確認をすることも重要なポイントとなってきます。

では、ここから各項目について説明します。

① 基板の配線インピーダンス

電源リップルの低減を目的に、電源IC(DC/DC)からメモリまでの配線インピーダンスを低くする必要があります。

② LPDDR4の電源電圧について

データシートには推奨電源電圧範囲としてスペックが規定されていますが、それ以外にメモリのBGAボール端でのACノイズを、0~20MHzの期間で45mVp-p以下に抑える必要があることにも注意が必要となります。

③ 電源端子に付加するコンデンサの配置

ノイズ除去を目的としたデカップリングコンデンサですが、ホストデバイスやメモリの各電源端子の近傍に配置する必要があります。

せっかくコンデンサを付加してもデバイスから離れた場所に接続しては、十分なノイズ除去の効果は得られません。

この電源端子に付加するコンデンサですが、ESR(Equivalent Series Resistant)やESL(Equivalent Series Inductance)が小さい積層セラミックコンデンサが推奨されているケースもありますので、詳細については各メモリメーカーのデータシート等を参照してください。

ここまで、基板設計する上での注意点について説明してきましたが、実際に基板設計した段階でどの程度のリップルの影響を低減できたか、基板配線の影響が度合いを確認するには、基板シミュレーションで確認することが重要となります。

基板設計段階でのシミュレーションの実施は、基板開発工数の削減にも繋がりますので有効に活用してください。

4. コラム

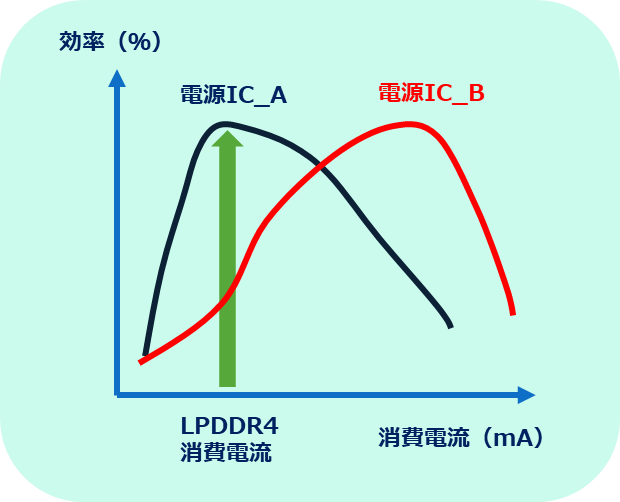

LPDDR4の消費電流についての考え方や基板設計を行ううえでの参考情報について説明してきましたが、メモリに電源を供給する電源IC(DC/DC)の選定はどの程度重要なのでしょうか?

メモリに電源供給する電源ICの選定には、必要する電源の出力電圧、精度以外にメモリの消費電流に合わせて最適な製品を選定する必要があります。

例えば、上図のように電源IC_Aと電源IC_Bの2種類の異なる効率特性を持った電源ICがあったとします。

電源IC_Aの場合はLPDDR4の消費電流に対し、効率の高い所で使用することになりますが、電源IC_Bの場合は、LPDDR4の消費電流に対し、効率の低いところで使用することになります。このようなケースで電源IC_Bを採用すると、システムが誤動作して、電源ICの再選定、基板改版等が必要となる場合がありますので、注意が必要です。

LPDDR4の採用検討する際には、消費電流、最適な電源ICの選定についても考慮する必要があることを覚えておいてください。

おわりに

いかがでしたでしょうか。

本ブログでは、LPDDR4の消費電流についての考え方や基板設計を行ううえでの参考情報について説明させていただきました。

LPDDR4の採用検討する際には、消費電流、最適な電源ICの選定についても考慮する必要があることを覚えておいてください。

ご不明な点やご質問などはお気軽にPALTEKまでお問い合わせください!

本ブログに関するご質問・お問い合わせはこちらへ

https://www.paltek.co.jp/semiconductor/maker/micron/inquiry/index.html

最後までご覧いただきありがとうございました!