メモリ基本講座「DDR5とは何ぞや?(2) ~DDR5の新機能~」

2025年7月18日 更新

メモリ基本講座「DDR5とは何ぞや?(1) ~DDR5で何が変わる?~」では、DDR5の特長、DDR4とDDR5の違いについて紹介しました。今回は、DDR5で追加された機能とDDR5で追加された端子、削除された端子について紹介します。

目次

DDR5で追加された機能

Same-Bank リフレッシュ

まず、パフォーマンスの向上を目的に追加された機能がSame-Bankリフレッシュです。

DRAMはメモリセルのコンデンサに電荷を蓄えることでデータを保持していますが、時間経過と共にリーク電流の影響で保持していた電荷が減少し、書込んだデータが保持できなくなってしまいます。これを防ぐことを目的にDRAMでは一定の間隔でコンデンサに電荷を書込んでデータを保持しています。この一定の間隔でデータを書込む制御がリフレッシュです。

これまでのDDRの製品におけるリフレッシュ制御は、All bankリフレッシュのみでしたが、DDR5ではAll bankリフレッシュに加え、Same-Bankリフレッシュが追加されました。DRAMにおいてリフレッシュは必要不可欠な制御ですが、リフレッシュ期間中は該当箇所へのデータのRead/Writeを行うことができません。

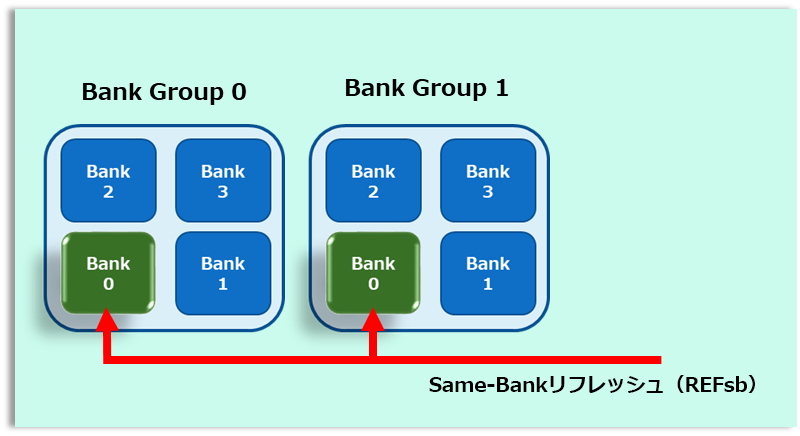

このSame-Bankリフレッシュ機能ですが、図1に示すように、バンクグループ内で同じbank Noに対してのみリフレッシュを実行することが可能となるので、これまでのAll bankリフレッシュと比較して、リフレッシュサイクルの時間を低減することが可能となります。

図1 Same-Bankリフレッシュ

DDR5 16Gbの例ですが、ALL bankリフレッシュの場合、297nsのtRFC(リフレッシュサイクル時間)が必要でしたが、Same-Bankリフレッシュの場合のtRFCは130nsとなり、165ns低減されます。

One die ECC

続いて、データの信頼性向上を目的として追加されたのが、On-Die-ECC、RFM、Loop Back Modeになります。

これまでのDDRの製品ではECC(Error Correction Code)の機能はホスト側に実装されていましたが、DDR5ではデバイス内部でエラー訂正を可能とする、On Die ECCを搭載し、システムレベルでのエラー修正の負荷を低減することが可能となりました。DDR5のECCですが、シングルエラー修正(SEC)として実装され、128データビットと8パリティビットをペアにした136ビットのコードワードを構成し、Writeコマンド中にDRAMに保存されます。

また、On Die ECCと合わせ追加された機能がECS(Error Check and Scrub)になります。

このECS機能ですが、内部データを読み取り、エラーを検出した際に、エラーを訂正し、正しい値で書き戻すことが可能となります。

ECSの設定に関しては、Mode Register[MR14]OP7(ECS Mode)でManual ECS modeかAutomatic ECS mode(default)かを選択可能です。

MPC

MPC(Multi-Purpose Command)は、インターフェイスの初期化、トレーニング、および定期的なキャリブレーションに関連する機能を実行するためのコマンドです。これまでのDDRの製品では個別のコマンドまたは、モードレジスタの設定により実行されていましたが、DDR5のMPC機能は、コマンド/アドレスバスのMPC命令コード(8つのオペレーションビットを含む)により開始され、最大で256個の機能を実行することが可能となります。

Loopback mode

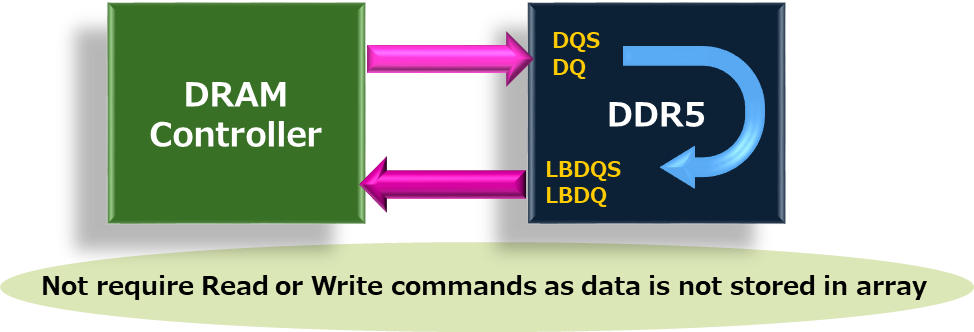

Loopback modeは、メモリコントローラがメモリアレイに対し Read/write を行うことなく、DRAMへ送信されたデータのシグナルテストが可能となる機能です。

図2 Loopback mode

この機能の追加に伴い、DDR5では、LBDQ(Loopback Data Output)とLBDQS(Loopback Data Strobe Output)の端子が追加されています。

Loopback Modeで出力する信号は、MR(Mode Register)53:OP[4:0]で選択することが可能で、Loopback modeのenable/disabled設定もMR53で設定します。

RFM

メモリの特定の行アドレスに対して連続アクセスを行った場合に隣の行アドレスに書込みされたデータが干渉して反転し、リードが不可能となるRow hammerという現象が知られています。DDR5ではRow hammerの発生で生じていたデータの不整合を保護するための機能としてRFM(Refresh Management)機能が追加されました。

RFMモードは、MR58 OP[0]により設定が可能となります

DDR5でDDR4から追加された端子、削除された端子

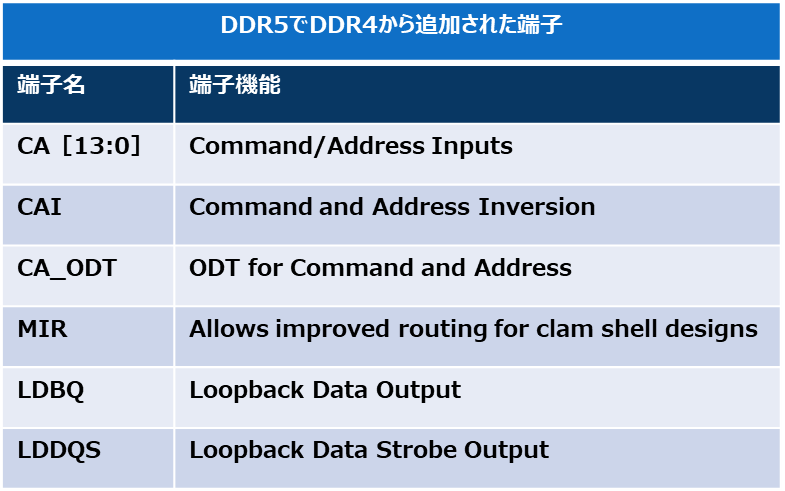

DDR5での機能の追加に伴い、追加された端子、削除された端子があります。メモリ基本講座「DDR5とは何ぞや?(1) ~DDR5で何が変わる?~」でも端子の件は少し触れましたが、詳細について紹介します。

まず、DDR5で追加された端子ですが、DDR4ではCommand /Address 入力を各端子に割り振っていましたが、DDR5ではCommnad/Address入力をCA[13:0]に集約しています。その他は、Loopback mode機能の追加に伴うLDBQ,LDDQS端子等になります。また、VDD(Power supply)、VDDQ(DQ power supply)、VSS(Ground)の各端子数も、DDR4から増加されています。

※VDD、VDDQ、VSS端子の増加数については、バス幅がx4、x8の製品とx16の製品で異なります。

表1.DDR5で追加された端子

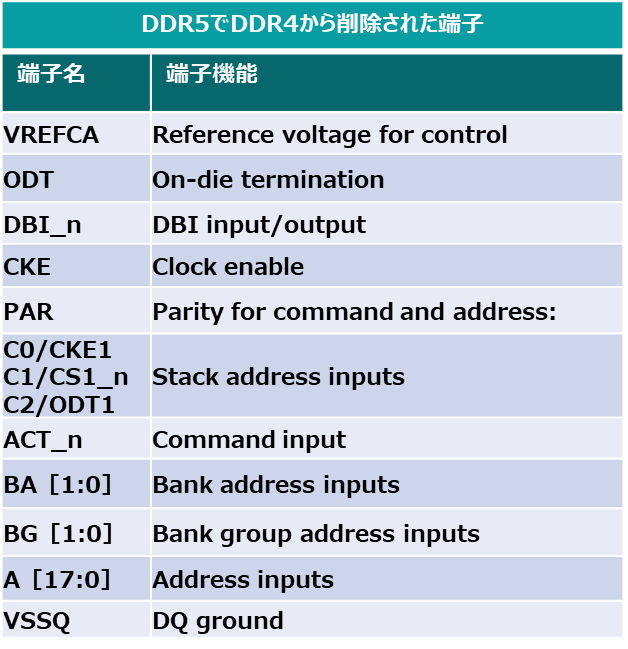

続いて、DDR5で削除された端子ですが、Command/Adress Input系の端子に加え、CKE(Clock enable), ODT(On-die termination)、VRFCA(Reference voltage for control),VDDQ(DQ ground)等端子が削除されました。

表2.DDR5で削除された端子

おまけ

メモリの性能を表現する際に、データレート(Data rate)やメモリバンド幅(memory bandwidth)といった言葉を目にする機会も多いと思いますが、今回はそれぞれの違い等について紹介します。

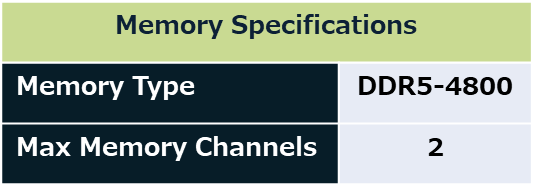

まず、データレートですが、単位時間あたりにどれだけのデータ転送が可能かを示したもので、メモリの端子毎に定められた性能となります。DDR5-4800MT/s(※1)の場合、1秒間に48億回のデータ転送が可能ということになります。

このデータレートですが、メモリに入力されるクロックの周波数と1クロック当たりのデータ転送回数の積によって決まります。

1クロック当たりのデータ転送回数は、DDR系の製品であれば、クロックの立上りと、立下りに同期してデータ転送が行われるので“2”(固定値)です。

例)クロック周波数が2400MHzの場合、2400MHzX2=4800MT/s

続いて、メモリバンド幅ですが、こちらもメモリのデータ転送速度を表現したものですが、メモリとデータ転送を行うホスト(CPUやFPGA等)との間で単位時間あたりにどれだけのデータ転送を行うことができるかを示した性能となります。

メモリバンド幅は、データレートを決定する項目に別の項目を加えた下記の4つの要素により求めることが出来ます。

- (1)メモリに入力されるクロック周波数

- (2)1クロックあたりのデータ転送回数=2(固定値)

- (3)バス幅=8Byte(64bit、固定値)

- (4)メモリとのチャンネル数

(1)と(2)はデータレートと同じ項目

各CPUメーカーから公開されているスペックを基にメモリバンド幅を計算すると次のようになります。

例)

メモリバンド幅=2400MHzX2X8ByteX4=153.6GB/s

メモリバンド幅については、CPUメーカーのスペックにも記載されていますので、参照してみてください。

※1 MT/s:mega transfer per second

最後に、MicronのDDR5に関する情報は下記から確認することが可能です。

https://www.micron.com/products/dram/ddr5-sdram

また、Micronは、DDR5に関するさまざまな技術情報を提供する 「DDR5 Technology Enablement Program(TEP)」を準備していますので、興味のある方はアクセスしてみてください。

DDR5のデータシートを含め、開発に役立つさまざまな情報を入手することが可能となります。

注1)TEPは上記Webサイトからアクセス可能です

注2)TEPにアクセスする際にはMicron webサイトへのアカウント登録が必要となります