メモリ基本講座「DDR5とは何ぞや?(1) ~DDR5で何が変わる?~」

DDR5 SDRAMとは?

次世代のハイエンドPCやサーバーを主なターゲットとしたDDR5 SDRAM(Double Data Rate5 Synchronous Dynamic Random-Access Memory)の標準規格(JESD79-5)が2020年7月にJEDECより公開されました。

今回は、そのDDR5についてDDR4との違いを中心に紹介します。

DDRの規格(JESD79F)がJEDECから公開されたのが、2008年2月。その後、DDR2、DDR3、DDR4と新しい世代の製品がリリースされる毎にData Rateの向上が図られる一方で、電源電圧は低下してきました。

DDR5はこれまでの流れを受け継ぐ形で、動作電圧はさらに低下し、パフォーマンスが向上した製品です。

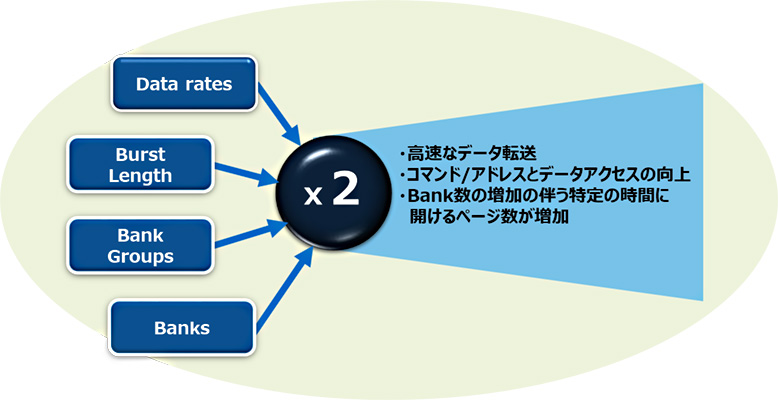

DDR5は、DDR4と比べてData Rate・Bust Length・Bank Group・Bankをすべて2倍とすることで、高速なデータ転送、コマンド/アドレスといったデータアクセスの向上が可能となります。

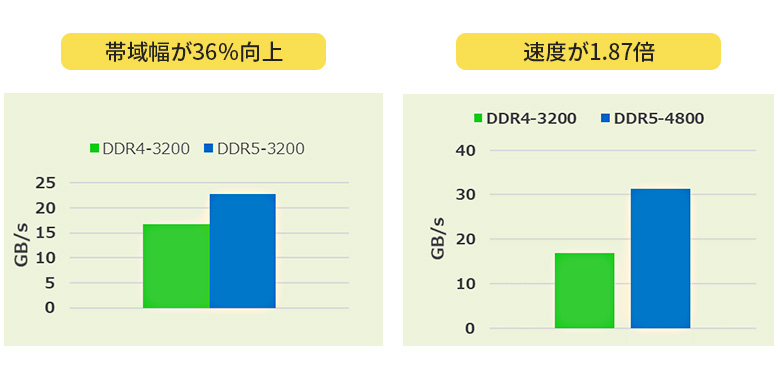

Micron Technology社が実施したシミュレーション結果によると、DDR4とDDR5で同一のスピードグレードで比較した場合、 帯域幅が36%向上。また、DDR4-3200とDDR5-4800の異なるドグレードで比較した場合にDDR5の方が1.87倍高速になるとの結果も報告されています。

DDR5とDDR4の性能比較

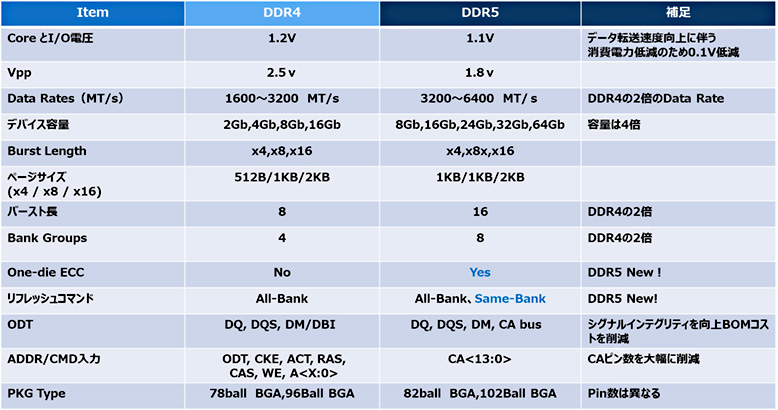

ここではJEDECから発表されているDDR5とDDR4の性能を比較し、代表的な差分について紹介します。

CoreとI/O電圧

まず、CoreとI/O電圧ですが、DDR4の1.2Vから0.1V下がり、DDR5では、1.1Vとなります。DDR3からDDR4への変更時には1.5Vから1.2Vと0.3Vも低下したのに対し、DDR4からDDR5では0.1Vの低下に留まっています。

低電圧化を行う際には、トランジスタ素子の特性や回路構成を見直すことが想定されますが、電源電圧の下げ幅が小さくなっているので、低電圧化に関しては限界に近づきつつあるのではと思われます。

Data Rate

続いてData Rateですが、DDR4では1600~3200MTSのサポートに対し、DDR5では3200から6400MTSと2倍のData Rateをサポートすることになります。

Data Rateを向上する上で欠かせないのがプロセスの微細化です。DDR4の2倍のData Rateを実現するために、メモリメーカー各社とも微細化プロセスを適用した製品開発を進めています。例えば、Micronは先ず、1Znmプロセスを用いてDDR5の製品開発を進めています。

Burst Length、Bank Group

動作電圧の低下、プロセスの微細化以外にDDR5の仕様を実現する上でDDR4から変更となるのがBurst Length、Bank Group、BankでそれぞれDDR4の2倍になります。

Bust Lengthは、DDR4の8から倍増の16にすることで、コマンド/アドレスとデータバスの効率性が向上します。

Bank GroupにおいてもDDR5では、DDR4の倍になっていますが、Bank Group毎のBank数はDDR4と同じです。これにより特定の時間におけるページ数が増加し、ページのヒット率が高くなるため、全体的なシステム効率が向上します。

端子関係では、Bank Groupの増加やコマンドの適用拡大等、DDR4から単純に機能を増加すると端子数の増加要因になります。一例としてDDR5ではBank Group数は8Groupになりますが、この変更によりBank Groupを指定するアドレスbitが2から3bitに増加してしまいます。そこでDDR5では端子数を削減するための対策が取られています。

代表的なところでは、ODT端子(On Die Termination)とCKE(Clock Enable)端子で、DDR5ではODT端子とCKE端子は削除されています。ODTの制御については、コマンド入力への制御に移行されます。CKE端子は元々パワーダウンモードとセルフリフレッシュモードへの移行を目的に端子に機能が割り当てられていましたが、DDR5では、パワーダウンモードへの移行に関しては、コマンド入力で制御されることになります。DisableについてはCS(Chip Select)端子にて制御されます。

パッケージ

DDR5のパッケージですが、バス幅x16製品では、102Ball BGAパッケージになります。

端子機能等に関する詳細情報につきましては、各メモリメーカー発行のデータシートを参照願います。

おまけ

DDR4とDDR5との差分の部分で、プロセスの微細化について説明しました。

Micronは1zプロセスを用いた製品開発を進めていますが、そもそも、この1zって何でしょうか?

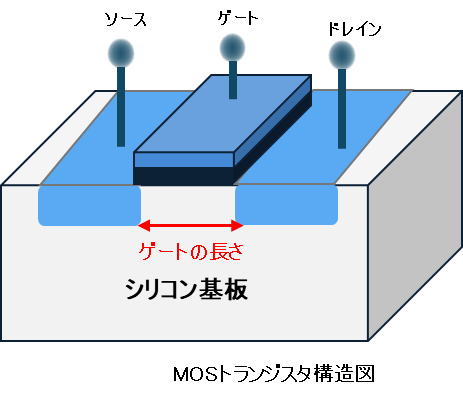

1zという表記は、プロセスノードのことで、プロセスの最小加工寸法を表します。このプロセスの最小加工寸法については、各メーカーで定義が異なる場合がありますが、一般的にはMOS(Metal-Oxide-Semiconductor)トランジスタのゲート長さの幅を指指していることが多いようです。

40nmプロセス適用の製品であれば、搭載しているMOSトランジスタのゲート長が40nmであることになります。 メモリ製品の場合、20nm以上の製品であれば、それぞれ採用しているプロセスノードで表記していましたが、10nm台の製品になってくると、各社とも1ynm、1znm、1αnmといった表記に代わってきました。

メモリの高速化を実現する上で、プロセスの微細化は必要不可欠ですが、各メモリとも最新の微細化プロセスを適用して製品開発を進めています。

この1Ynm、1znm、1αnmの表記に関しても各社の仕様によって異なりますが、一般的に、1Ynmが17nm~16nm、 1znmが16nm~14nm、1αnmが14nm以下とされています。

MicronのDDR5は1znmプロセスで製品開発を進めていると説明しましたが、他にDDR5の開発を表明しているメーカーで A社は1αnm、B社は1Ynmと各社採用プロセスが異なっています。

今後もメモリの高速化に伴い、採用プロセスの微細化が進むことが予想されますが、どこまで微細化が進むか注目しましょう。

次回は、On-die ECC、リフレッシュコマンドの(Same-Bank)等にDDR5で追加された新機能について紹介します。

PALTEKでは、DRAM、NOR Flash、NAND Flashについては Micron 、SRAMについては GSIテクノロジー の取り扱いをしています。