Simulink®モデルをHDL化してみた【第2回】「2-D LookupTableをHDL化してみた」

高速処理に対応するモデルをFPGAやAdaptive SoCに組込むHILSのシステムを構築する場合、プラントモデルをHDL化する必要があります。

このブログでは、Simulink®で作成したモデルをMathWorks社のHDL Coder™を使用してHDL化を行う際に、設計者の皆様が躓く箇所について2回に分けて解説します。

2回目の今回は、「2-D LookupTableをHDL化してみた」結果です。

前回の第1回「RC回路をSimulink®でモデル化してHDL化してみた」はこちらを参照ください。

なお、実行した環境は以下の通りです。

| OS | Microsoft Windows 10 Pro | ||

|---|---|---|---|

| MathWorks社製 | MATLAB® | バージョン 9.8 | (R2020a) |

| Simulink® | バージョン 10.1 | (R2020a) | |

| Fixed-Point Designer™ | バージョン 7.0 | (R2020a) | |

| HDL Coder™ | バージョン 3.16 | (R2020a) | |

| MATLAB Coder™ | バージョン 5.0 | (R2020a) | |

| Xilinx社製 Vivado® Design Suite | 2019.1.2(64bit) | ||

目次

2-D LookupTable

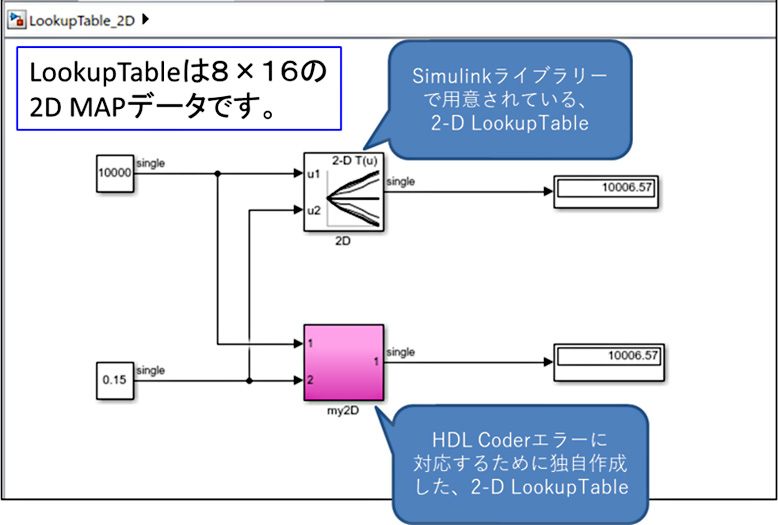

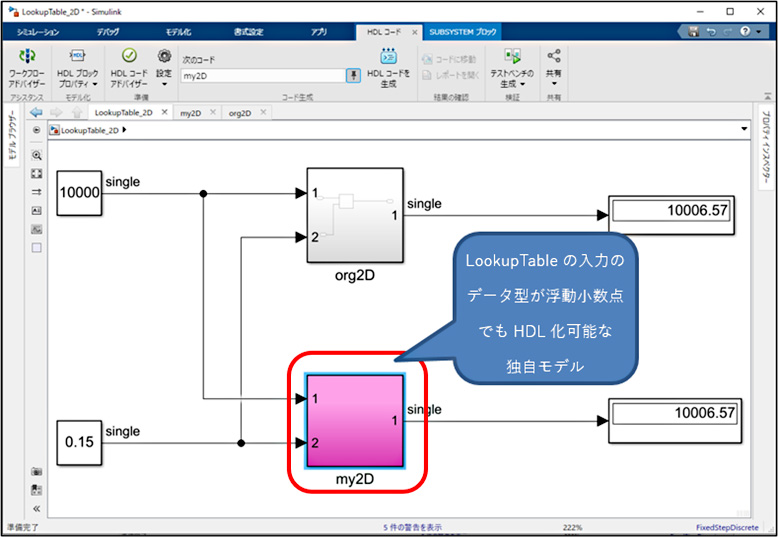

今回HDL化するLookupTableは図1のような2-D LookupTableです。

図1

2Dは、Simulink®であらかじめ用意されている2-D LookupTableを使用したブロックです。my2DはHDL Coder™エラーに対応するために独自に作成した2-D LookupTableです。

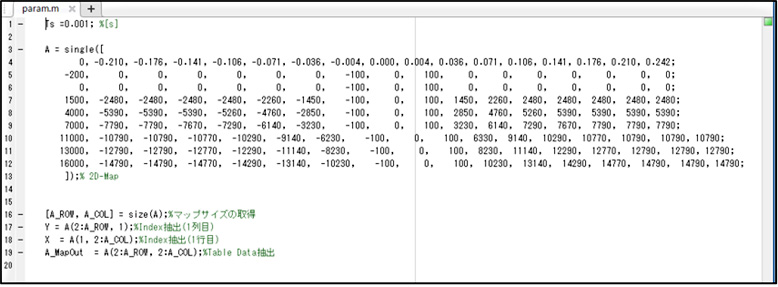

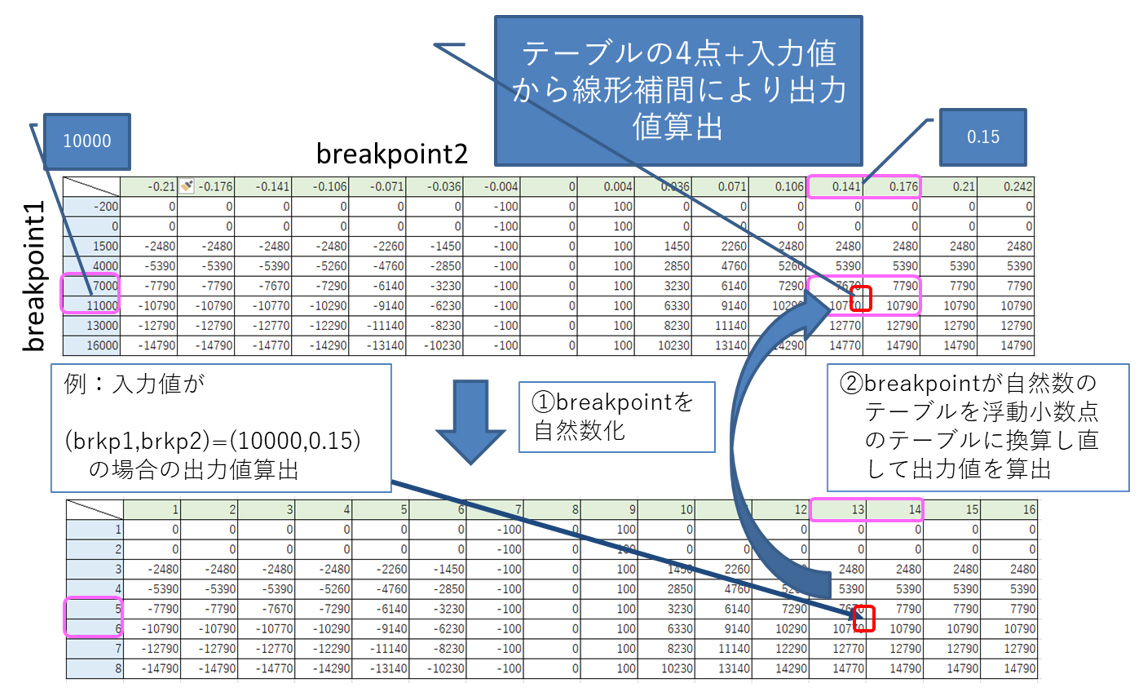

使用したテーブルデータは図2の縦8×横16の2D MAPデータです。

図2

2-D LookupTableは実測値の結果をテーブルデータとしてもたせ、2入力の値からテーブル値を使って補間した出力結果を演算に使用する、使用頻度の高いブロックです。

2-D LookupTableをHDL Coder™でHDLへ自動コード変換する

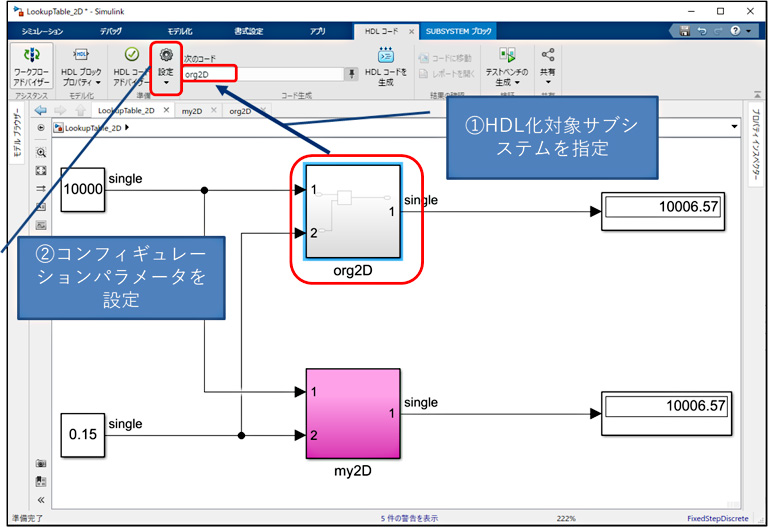

Simulink®であらかじめ用意されている2-D LookupTableの2DをHDL化していきます。

HDL Coder™ではSimulink®のトップ階層のブロックをHDL化できないので、サブシステム org2D階層を追加しています。

HDL Coder™を起動し、

①HDL化対象のサブシステムを指定します。(今回は「org2D」と指定)(図3)

②コンフィギュレーションパラメータを設定します。第1回ブログ時の設定を参照ください。

図3

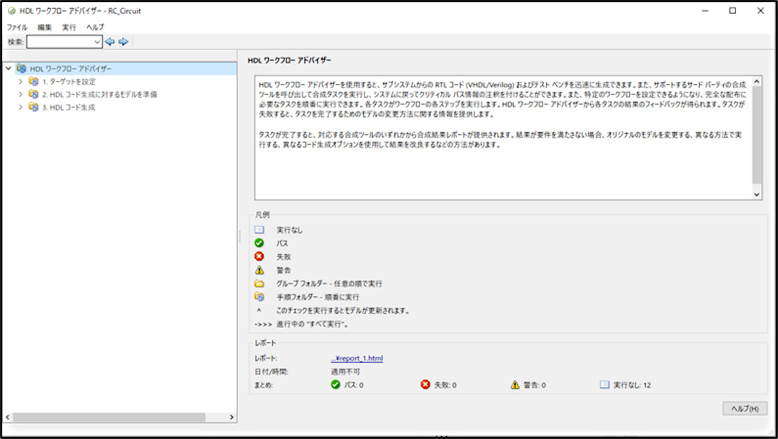

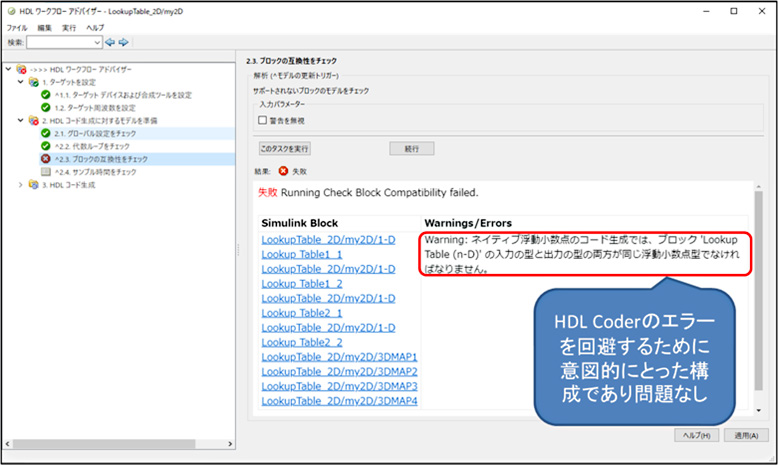

HDLワークフローアドバイザーを起動し、実行開始します。(図4)

図4

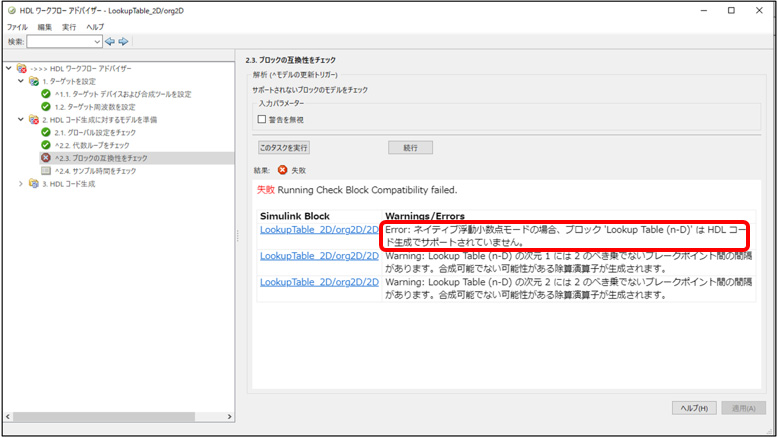

エラーになってしまう

ルールチェックでエラーになってしまいました。(図5)

図5

今回のエラーはLookupTableの入力に浮動小数点を使用していることが原因です。R2020b以降のバージョンではサポートするようになりましたが、R2020a以前のバージョンのHDL Coder™では入力に浮動小数点をサポートしていません。

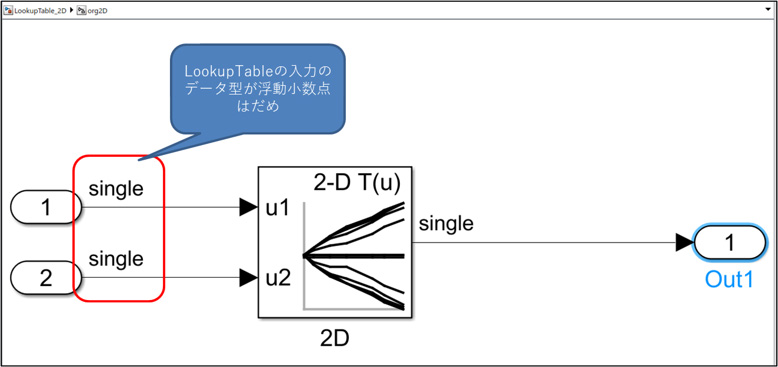

調べてみると、確かに図6のようにLookupTableの入力に浮動小数点が使用されていました。

図6

このエラーには、次の対策が有効です。

ブロックを置換える

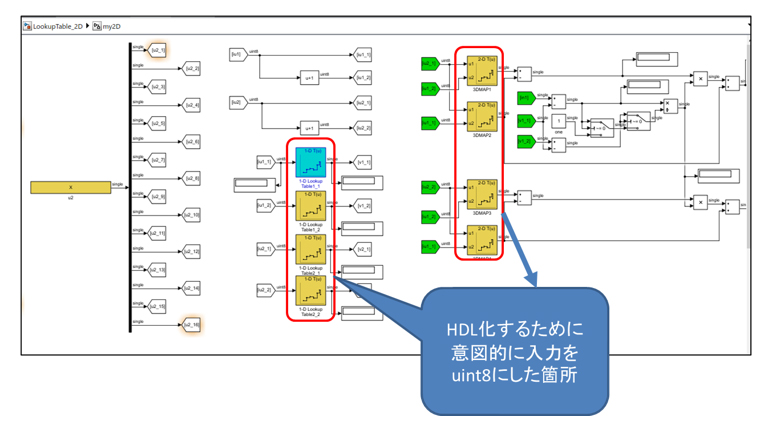

入力が浮動小数点でも対応できる、独自モデルmy2Dを作成し置換えました。(図7)

図7

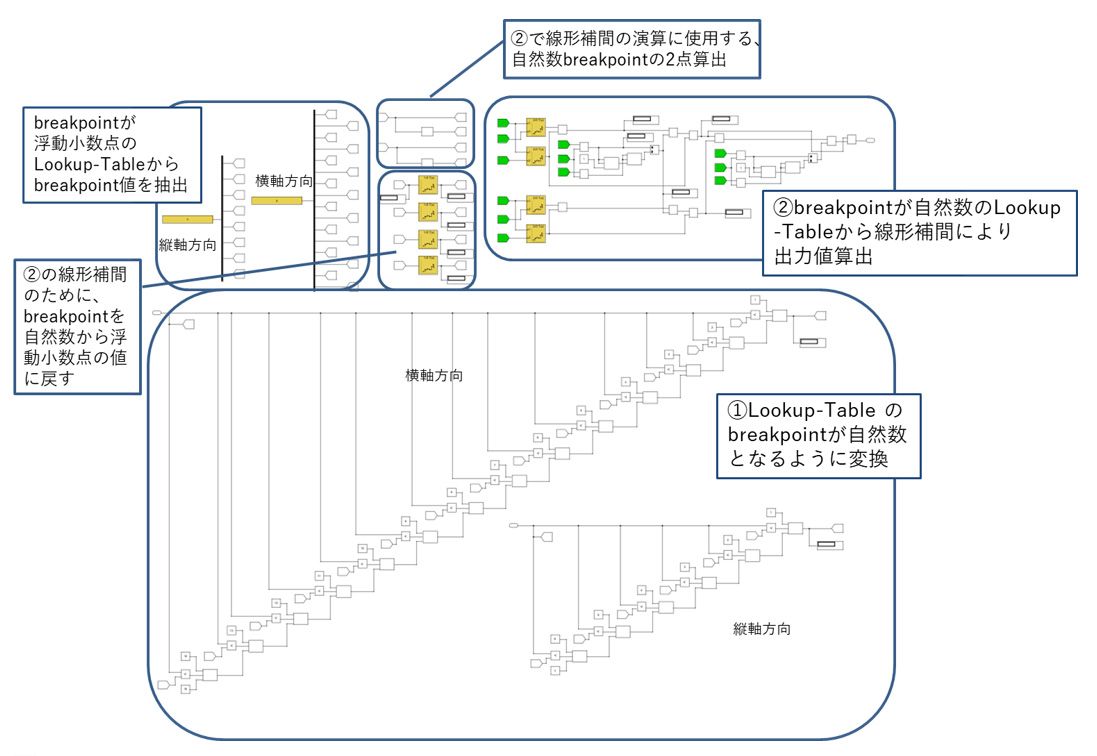

独自モデル構成

独自モデルmy2Dは大きく分けて以下の二つで構成されています。(図8)

①Lookup-Table のbreakpointが自然数となるように変換する。

②breakpointが自然数のLookup-Tableから線形補間により出力値を算出する。

図8

breakpointが自然数のテーブルを浮動小数点のテーブルに換算し直し、テーブルデータの4点と入力値から線形補間により出力値を算出します。(図9)

図9

独自モデルmy2DでHDL Coder™実行

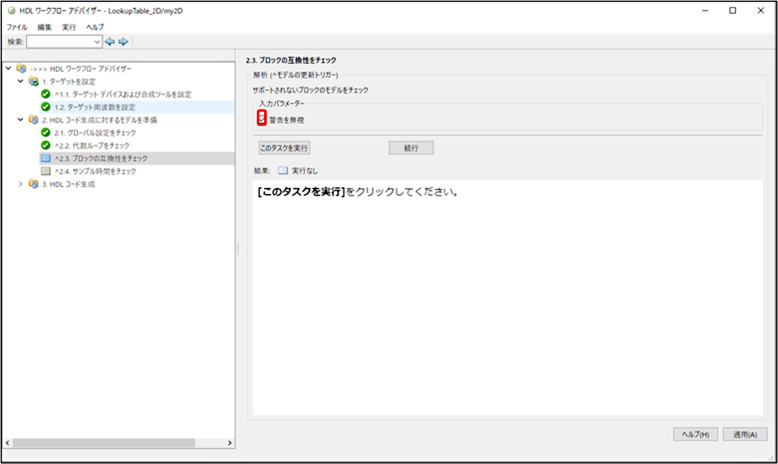

独自モデルmy2Dに置換え、再実行したところエラーは消え、下記のようなワーニングのみとなりました。原因はLookupTableの入力と出力でデータ型が同じ浮動小数点型でないためです。(図10)

図10

該当箇所を確認すると、以下のように、HDL Coder™のエラーを回避するために意図的にとった構成であり問題ありません。(図11)

図11

「警告を無視」にチェックを入れ、続行します。(図12)

図12

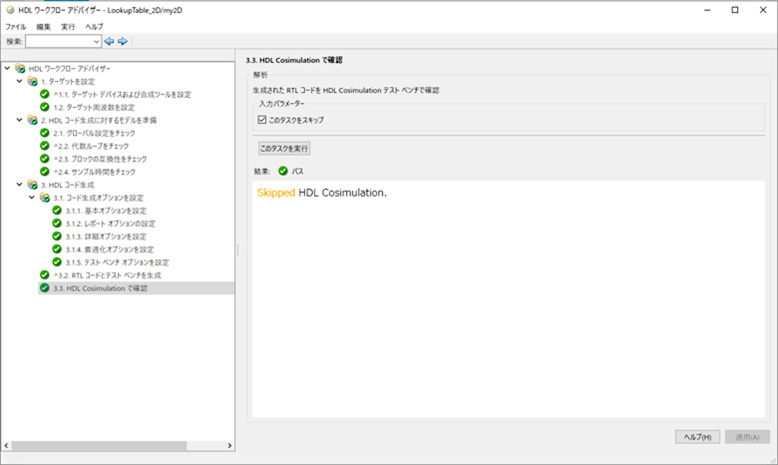

独自モデルmy2Dに置換えたことで、HDL化に成功!(図13)

図13

妥当性確認

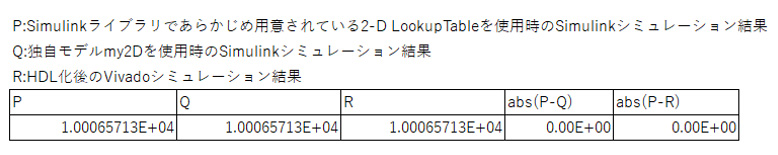

今回のシミュレーション結果は表1のようになりました。

この結果から(brkp1,brkp2)=(10000,0.15)を2D-LookupTableへ入力した場合の出力結果について、妥当性を確認します。

-

①Simulink®ライブラリであらかじめ用意されている2-D LookupTableを使用した場合とmy2Dに置換えた場合の誤差の確認

②HDL化による誤差の確認

表1

①「Simulink®ライブラリであらかじめ用意されている2-D LookupTable」を使用した場合と独自モデルmy2Dに置換えた場合の誤差の確認

(brkp1,brkp2)=(10000,0.15)を2D-LookupTableへ入力した場合の出力値について、Simulink®ライブラリであらかじめ用意されている2-D LookupTableを使用時のSimulink®シミュレーション結果(P)と、独自モデルmy2Dを使用時のSimulink®シミュレーション結果(Q)の差の絶対値、Abs(P-Q)は0。データ型Singleでの有効桁数は7桁であり「Simulink®ライブラリであらかじめ用意されている2-D LookupTable」から独自モデルmy2Dへの置換えで問題なしと判断します。

②HDL化による誤差の確認

PとHDL化後のVivado® Design Suiteシミュレーションの結果(R)の差の絶対値、Abs(P-R)の結果は0。HDL化による誤差に問題なしと判断します。

終わりに

今回は、Simulink®モデルからHDL Coder™を使用してHDL化する際によくある躓きから、2-D LookupTableのHDL化での躓きを解説しました。

「Simulink®ライブラリに登録されている2-D LookupTable」はR2020a以前のバージョンではHDL Coder™が浮動小数点入力をサポートしていないため、浮動小数点入力にも対応した独自モデル2-D LookupTableのmy2Dを作成して置換えることでHDL化に成功しました。HDL化に際しての妥当性確認として、独自モデルのmy2Dに置換えることによる誤差、HDL化による誤差を調べ、問題ないことを確認しました。

Simulink®モデルからHDL Coder™を使用してHDL化する際の躓きやすい箇所について、前回「RC回路をSimulink®でモデル化してHDL化してみた」と、今回「2-D LookupTableをHDL化してみた」をお伝えしました。

これからも、このような等価回路からのSimuink®モデル化やモデルのHDL化に関するポイントをご紹介しますのでご期待ください。

もしお手元にあるSimulink®モデルのHDL化やモデルベースデザイン設計を委託したいというご要望がございましたら、弊社モビリティビジネス事業までお気軽にお問い合わせください。

最後までお付き合いいただきありがとうございました。