Simulink®モデルをHDL化してみた【第1回】「RC回路をSimulink®でモデル化してHDL化してみた」

高速処理に対応するモデルをFPGAやAdaptive SoCに組込むHILSのシステムを構築する場合、プラントモデルをHDL化する必要があります。

このブログでは、Simulink®で作成したモデルをMathWorks社のHDL Coder™を使用してHDL化を行う際に、設計者の皆様が躓く箇所について2回に分けて解説します。

1回目は、「RC回路をSimulink®でモデル化してHDL化してみた」結果です。

なお、実行した環境は以下の通りです。

| OS | Microsoft Windows 10 Pro | ||

|---|---|---|---|

| MathWorks社製 | MATLAB® | バージョン 9.8 | (R2020a) |

| Simulink® | バージョン 10.1 | (R2020a) | |

| Fixed-Point Designer™ | バージョン 7.0 | (R2020a) | |

| HDL Coder™ | バージョン 3.16 | (R2020a) | |

| MATLAB Coder™ | バージョン 5.0 | (R2020a) | |

| Xilinx社製 Vivado® Design Suite |

2019.1.2(64bit) | ||

目次

HDL化するモデルを準備

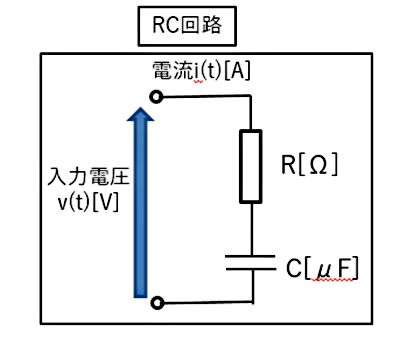

今回は図1のようなRC回路をモデル化します。

図1

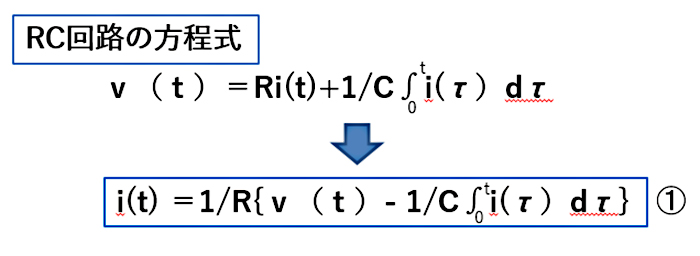

RC回路を電圧方程式であらわすと次のようになり、電流i(t)を左辺項とすると式①のようになります。

式①をSimulink®でモデル化すると図2のようになります。

図2

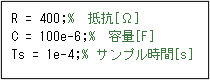

今回はパラメータとして以下を使用します。

HDL化対象を図3のようにサブシステム化します。(今回はサブシステム名を「RC」としました)

また、データ型は単精度浮動小数点型(Single)を使用しました。

図3

Simulink®モデルをHDL Coder™でHDLへ自動コード変換する

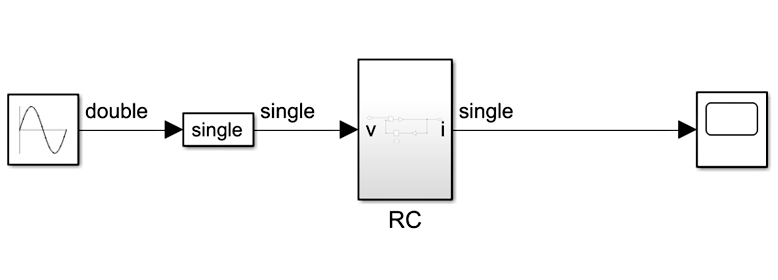

HDL Coder™を起動し、

①HDL化対象のサブシステムを指定します。(今回は「RC」と指定)(図4)

図4

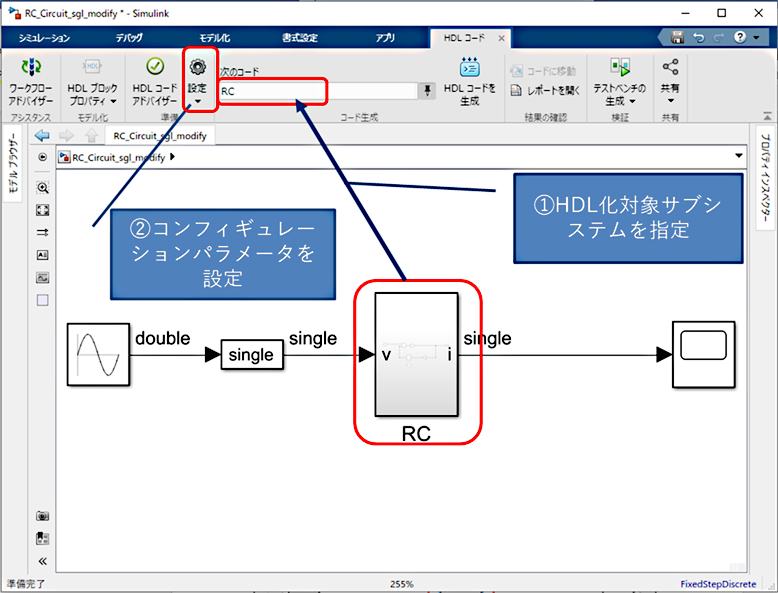

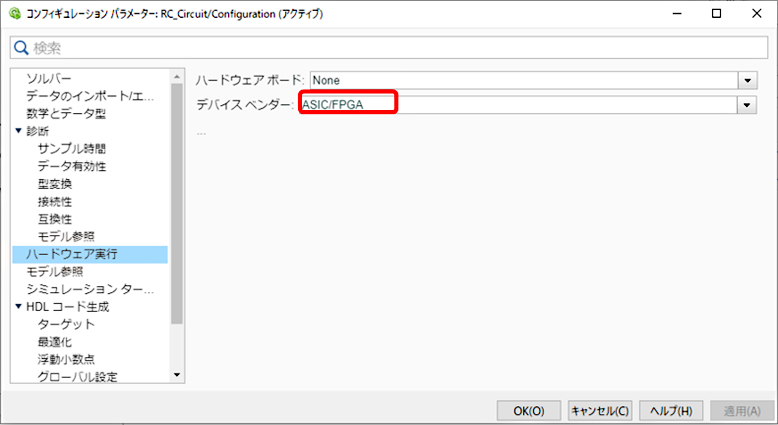

②コンフィギュレーションパラメータを設定します。(図5・6)

図5

図6

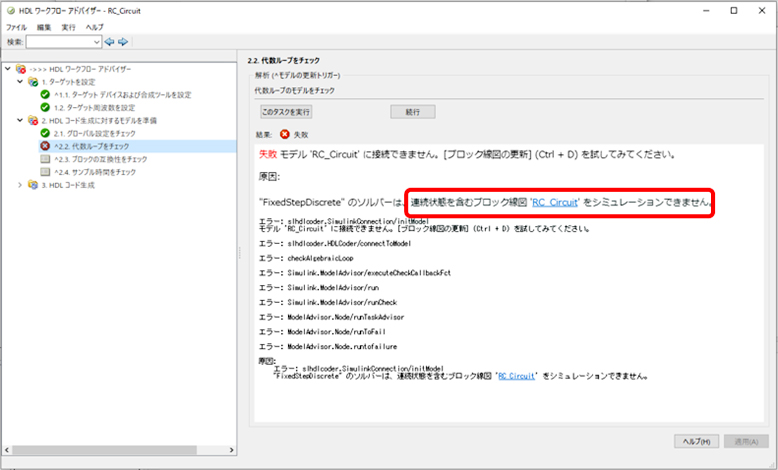

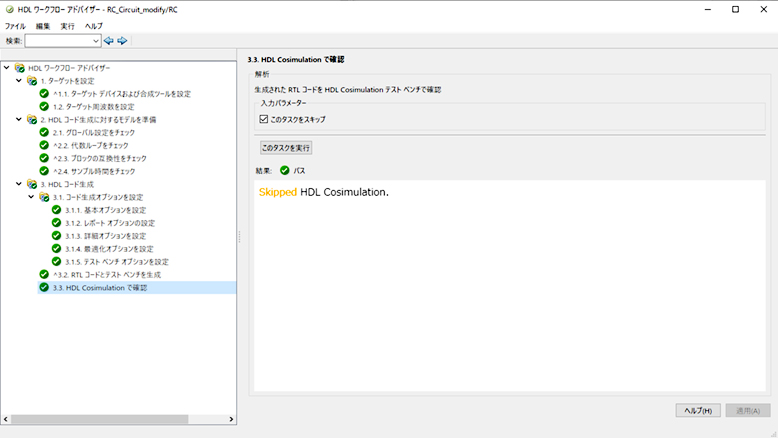

HDLワークフローアドバイザーを起動し、実行開始します。(図7)

図7

エラーになってしまう

ルールチェックでエラーになってしまいました。図8にあるように連続状態を含むブロックがあることが原因のようです。

図8

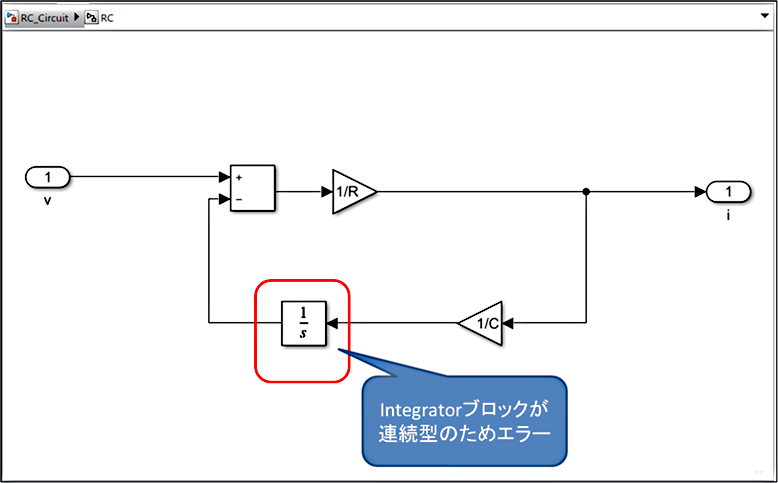

調べてみると、連続型のintegratorブロックが含まれていました。(図9)

図9

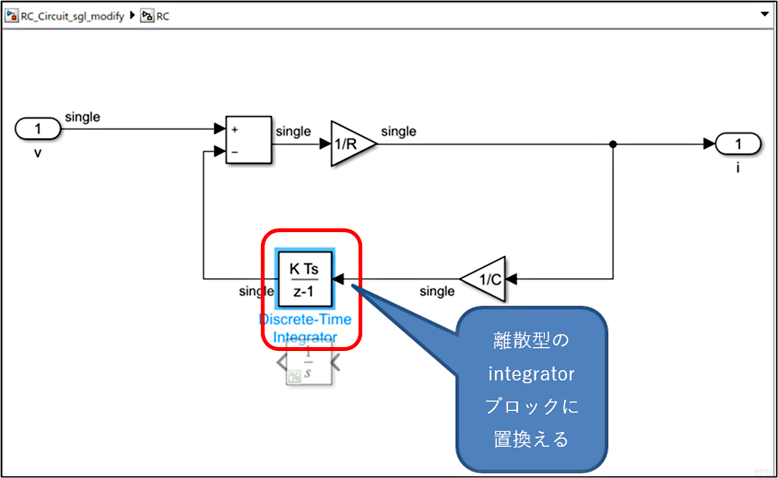

ブロックを置換える

エラーとなった連続型のIntegratorブロックを離散型のIntegratorブロックに置換えます。(図10)

図10

離散型ブロックに置換えたことで、HDL化に成功!(図11)

図11

妥当性確認

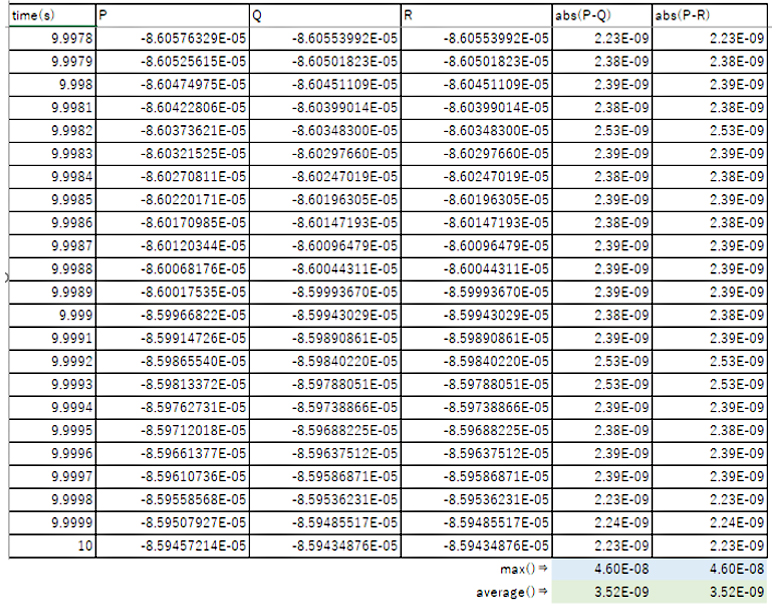

今回のシミュレーション結果は表1のようになりました。

この結果から出力信号電流iについて妥当性を確認します。

①連続型のIntegratorブロックを離散型のIntegratorブロックに置換えたことによる誤差の確認

②HDL化による誤差の確認

P:連続型Integrator使用時のSimulink®シミュレーション結果

Q:離散型Integrator使用時のSimulink®シミュレーション結果

R:HDL化後のVivado® Design Suiteシミュレーション結果

表1

①連続型のIntegratorブロックを離散型のIntegratorブロックに置換えたことによる誤差の確認

電流iの出力値について、連続型のIntegratorブロックを使用した、Simulink®シミュレーション結果(P)と、離散型のIntegratorブロックを使用した、Simulink®シミュレーション結果(Q)

の差の絶対値、Abs(P-Q)の結果から、(最大誤差)4.60E-08,(平均誤差)3.52E-09と判明。データ型Singleでの有効桁数が7桁であることから連続型から離散型への置換えで問題なしと判断します。

②HDL化による誤差の確認

PとHDL化後のVivado® Design Suiteシミュレーションの結果(R)の差の絶対値、Abs(P-R)の結果から、(最大誤差)4.60E-08,(平均誤差)3.52E-09と判明。データ型Singleでの有効桁数が7桁であることからHDL化による誤差に問題なしと判断します。

終わりに

今回は、Simulink®モデルからHDL Coder™を使用してHDL化する際によくある躓きから、RC回路を電圧方程式からSimulink®モデル化し、HDL化での躓きを解説しました。

HDL化対象のモデルに連続型のブロックが含まれると、HDL Coder™はモデルをHDL化してくれません。RC回路ではIntegratorを離散型ブロックに置換えることでHDL化に成功しました。またHDL化に際しての妥当性確認として、Integratorを連続型から離散型に置換えることによる誤差、HDL化による誤差を調べ、問題ないことを確認できました。

次回は、2-DのLookupTableのHDL化についてお伝えします。

もしお手元にあるSimulink®モデルのHDL化やモデルベースデザイン設計を委託したいというご要望がございましたら、弊社モビリティビジネス事業までお気軽にお問い合わせください。

最後までお付き合いいただきありがとうございました。