【MPSoC応用例】ファン回転速度の検出&回転速度の制御

今回はファン回転速度の検出および回転速度の制御回路を紹介したいと思います。

前提条件は回転速度検出および制御可能なファンを使っていること(4端子)です。

それでは始めましょう。

このブログは「FPGA設計ブログ一覧」の

基板設計・評価関連のひとつです。

目次

背景

使っている基板のファンがいつも最大速度で回すと音がうるさいので、回転速度の検出回路と回転速度の制御回路を作成しました。

方法

回転速度検出

周波数カウンター回路を利用し、ファンの回線速度出力信号の幅を測定することにより、回転速度を算出します。

回転速度制御

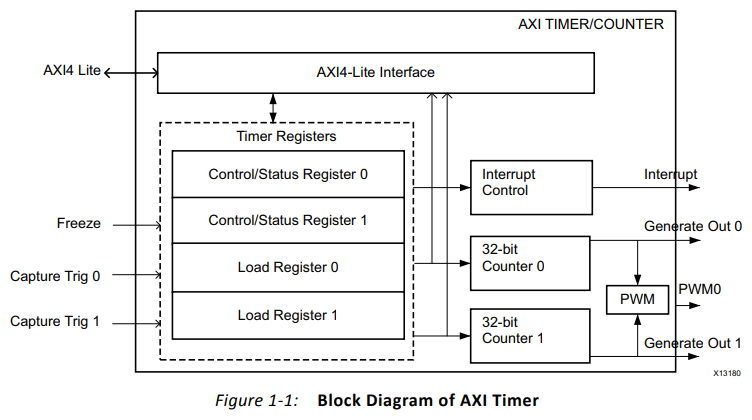

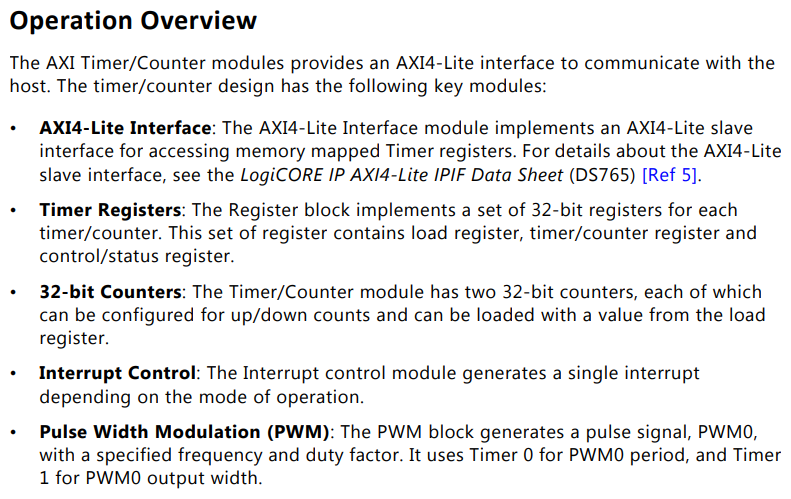

AXI Timerを利用し、ファン速度制御のPWN信号を生成します。

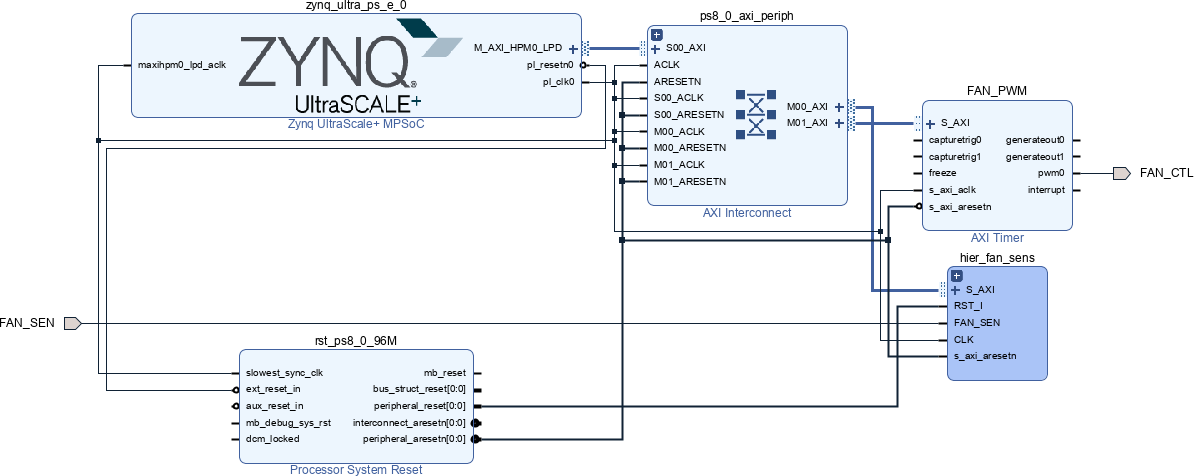

回路構成

MPSoCから制御できる回路を以下のように構築します。

出典:Vivado® ML Edition

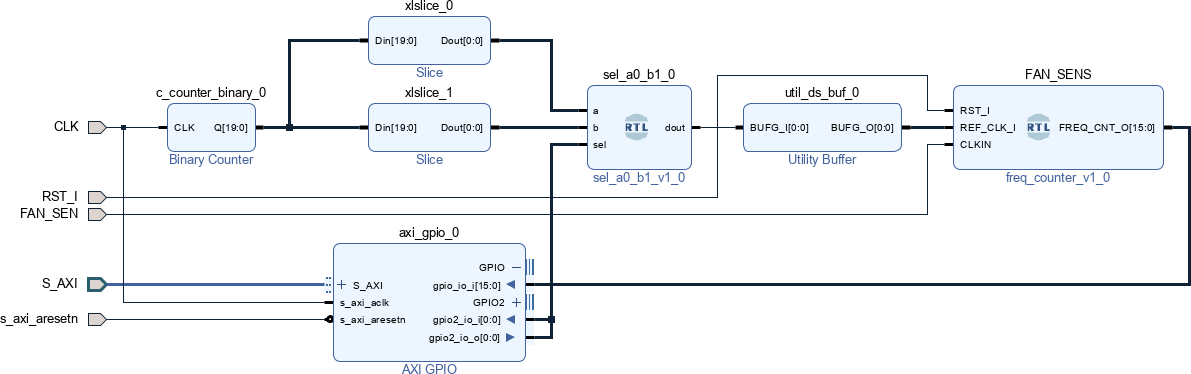

Hier_fan_sensの内部構成

出典:Vivado® ML Edition

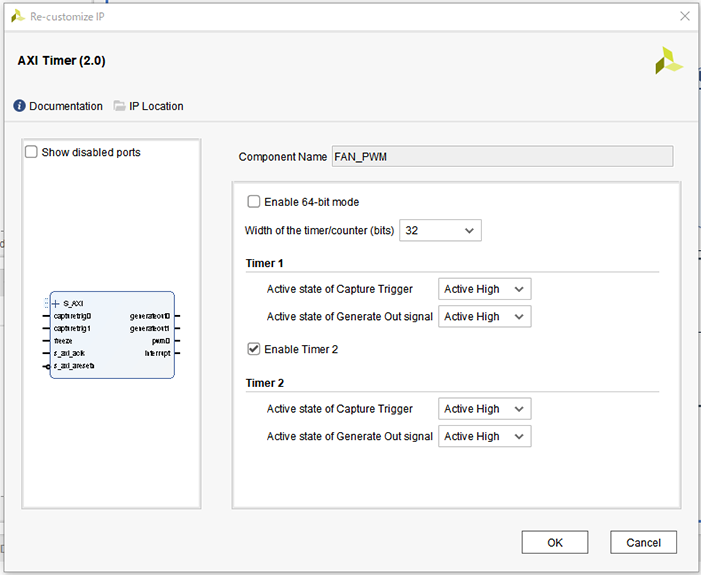

ファン速度制御のPWN信号を生成するAXI Timerの設定と内部構成

出典:Vivado® ML Edition

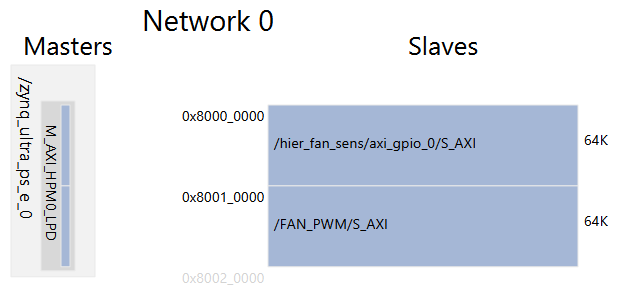

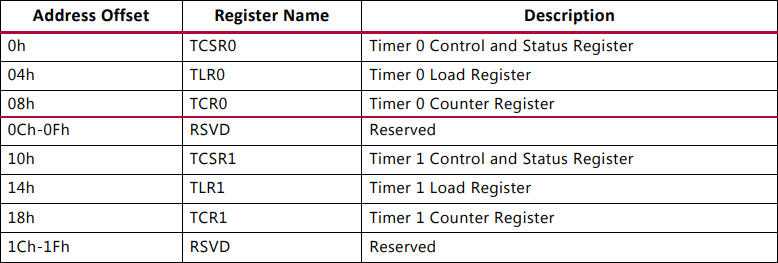

アドレスMAP

出典:Vivado® ML Edition

出典: AMD AXI Timer v2.0 Product Guide (PG079)

出典: AMD AXI Timer v2.0 Product Guide (PG079)

出典: AMD AXI Timer v2.0 Product Guide (PG079)

詳細は以下をご覧ください。

AMD AXI Timer v2.0 Product Guide (PG079)

上記の回路構成では、モジュールsel_a0_b1_0とFAN_SENS以外はVivado®に標準搭載されているIPになります。

EXAMPLEデザイン

EXAMPLEデザインについては以下よりダウンロードいただけます。

おわりに

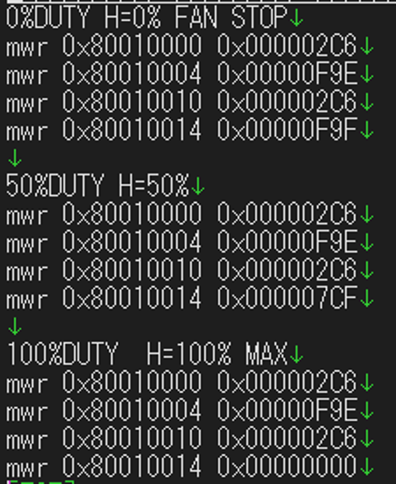

今回はAXI TimerのPWM機能を利用するため、以下のレジスタのcounter0でPWMの周期を設定し、counter1でPWMの幅を設定しました。

ソフトの制御でもちろん動作可能ですが、以下のようにレジスタを設定するだけでも、PWMの制御は可能ですので、手軽でテストしたいときにご参照ください。

出典:シリアルコンソール画面

いかがでしたでしょうか。

このようにVivado®2020.2のZynq® UltraScale+ MPSoC BASEのファン回転速度検出&制御用デザインが作成できました。次回からは制御ソフトのサンプリングプログラムを紹介したいと思います。

このブログは「FPGA設計ブログ一覧」の

基板設計・評価関連のひとつです。

弊社ではFPGA設計や回路図設計、レイアウト設計、ソフトウェア設計、筐体設計などを受託開発しています。

サービス内容をWEBサイトに掲載していますので、ぜひご覧ください。

FPGAの活用に際して設計検討などありましたら、お気軽にお問い合わせください。