メモリ基本講座「LPDDR5/5Xとは何ぞや?~概要編~」

本ブログでは、DDR(Double Data Rate)DRAMのモバイルデバイス向けに開発された低消費電力DDRメモリであるLPDDR(別名Mobile DDR)について解説します。

LPDDRは、エッジ・AI、拡張現実(AR)、自動運転、高解像度映像処理といった増大する帯域幅のニーズに応えるためにさらなる高帯域化、省電力化が進んでおり、LPDDR5/5XはLPDDR4/4Xよりも高いパフォーマンスと低消費を実現する製品です。

1. LPDDRメモリの変遷

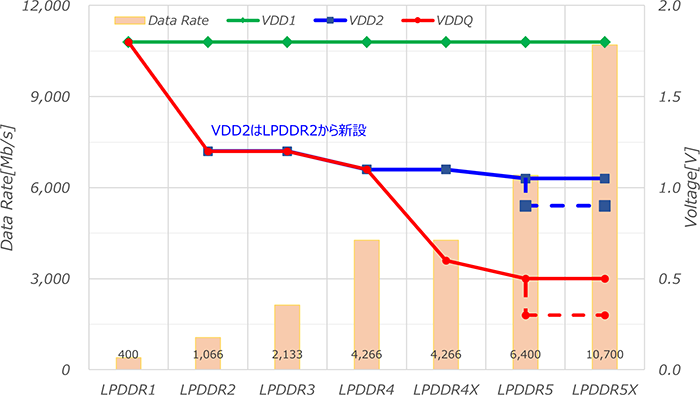

図1にLPDDRメモリの帯域と電圧の変遷を示します。

横軸はLPDDRの初期のLPDDR1から、現在リリースされているLPDDR5、5Xまでとなっています。

縦軸の棒グラフでスピード、いわゆるデータレートの推移を示しています。右肩上がりになっていることから、世代が進むにつれてデータレートが着実に向上していることが分かります。

縦軸の折れ線グラフは電圧の変化を表しており、こちらは世代を追うごとに電圧が下がっている、つまり低消費電力化が進んでいることを示しています。

VDD1(緑線)に変更はありませんが、VDD2(青線)やVDDQ(赤線)は、世代が進むにつれて低電圧化されています。これが、さらなる省電力化に貢献しているポイントです。

また、点線と実線の違いですが、LPDDR5世代以降では動作モードがより細かく分かれており、点線は設定によって、より低消費電力で動作させることが可能であることを示しています。ただし、これらのモードを利用するには、メモリ側だけでなく、CPUやFPGAなどホスト側のコントローラが対応している必要があります。

2. LPDDR4/4Xとの比較

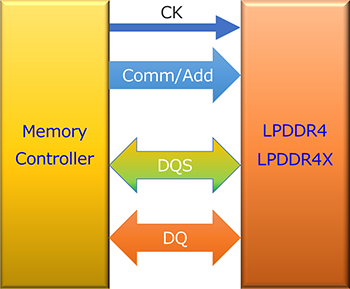

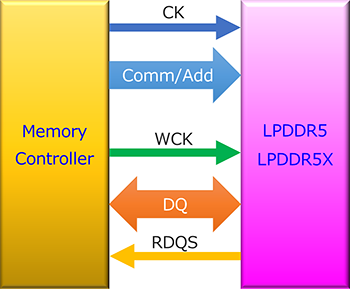

LPDDR4/4XとLPDDR5/5Xの基本仕様比較を表1に、通信方式の違いを図2に示します。

| LPDDR | LP4 | LP4X | LP5 | LP5X |

|---|---|---|---|---|

| VDD1 | 1.8V | |||

| VDD2 | 1.1V | VDD2H = 1.05V | ||

|

VDD2L = 1.05(Single Core Power Rail)

VDD2L = 0.9V(Dual Core Power Rail) |

||||

| VDDQ | 1.1V | 0.6V |

0.5V(term)

0.3V(un-term) |

|

| data rate | ≤4,266 Mb/s | ≤6,400 Mb/s | ≤10,700 Mb/s | |

| Bank | 8 banks | BG Mode | ||

| 8B Mode | — (JEDEC規格適用外) |

|||

| 16B Mode | ||||

| Burst Length | BL16/BL32 | BG Mode: BL16/BL32 | ||

| 8B Mode: BL32 | — (JEDEC規格適用外) |

|||

| 16B Mode: BL16/BL32 | ||||

| prefetch | 16n | 16n/32n (bank architectureによる) |

||

| Rx Mask shape | 長方形 | 六角形 | 六角形 | |

表1や図2から通信方式の変更や消費電力削減、高帯域化、バンクアーキテクチャの変更が確認できます。

帯域幅は2倍以上の向上、消費電力は約20%削減となります。

LPDDR4からLPDDR5への移行で大きく変わった点の一つが、クロック構成です。

LPDDR5では新たにWCK(Write Clock)が追加され、ライト専用のクロックとして使われるようになりました。

また、リード時にはRDQSがストローブ信号としてクロックの役割を担います。これにより、従来とは異なる動作モードになっています。

LPDDR4では、リード・ライトともにDQS(Data Strobe)を使い、そのエッジを基準にデータ(DQ)のやり取りを行っていましたが、LPDDR5/5Xではこの仕組みを細分化することで、不要なクロック動作を抑え、低消費電力化を実現しています。

電圧面でも改善が進んでおり、VDD2は1.1Vから1.05Vや0.9Vへ、VDDQもLPDDR5/5Xではモードによって0.5Vや0.3Vまで下げることが可能です。

その一方で、データレートはLPDDR4の最大4,266 Mb/sから、LPDDR5/5Xでは桁が一つ上がるレベルまで向上しており、高速化と低消費電力化を両立している点が大きな特徴です。

3. LPDDR5/5Xの特徴

電圧

新機能であるDVFSCを実現するために、電源電圧の構成にも変更が加えられています。

従来はVDD2として一つだった電圧が、VDD2H(High)とVDD2L(Low)の2系統に分離されました。

これにより、常に高い電圧をかけるのではなく、必要なタイミングだけVDD2Hを使用し、通常時はVDD2Lで動作させるといった制御が可能になります。こうした仕組みが、さらなる低消費電力化につながっています。

- VDD2H

- 高周波動作用(1.05V・メモリバンクやコアロジックなど向け)

- VDD2L※

- 低周波動作用(0.9V・周辺回路やIO機能向け)

※ シングルVDD2レールの場合はVDD2L = 1.05Vで省電力効果なし。

つまり、常に電圧をかけ続けるのではなく、本当に必要な場面だけ電圧を供給するという仕組みになります。

新機能であるDVFSQを実現するために、動作中のVDDQ電圧を可変できます。

- VDDQ = 0.5V(通常動作)

- VDDQ = 0.3V(低速DVFSQ時、さらなる消費電力削減)

VDDQについても、電圧を可変にすることで、消費電力を抑える仕組みになっています。

クロック

これまで1つだったクロックを次の2種に分離し、新たにCKとWCKという2種類のクロックが導入されました。

従来は単一のクロックで動作していましたが、役割ごとに分けることで、より効率的な制御が可能になっています。

特長は以下のとおりです。

- CK

- 制御回路向けの低速クロック(前世代のCKよりも低速)

- WCK

- データ回路向けの高速クロック(read/write実行時のみ動作)

- CK、WCKどちらも差動クロックのダブルデータレート(DDR)

- WCKはCKの2倍または4倍の周波数で動作

- RDQS(DDR)はWCKから生成(read実行時のみ動作)

CKは比較的低速で動作し、LPDDR4と比べてもややスピードを抑えた設計になっています。一方で、内部ではWCKを使って高速なクロック動作を行います。

さらに、このWCKはリード・ライトといった実際にデータの読み書きを行うタイミングだけ動作する仕組みになっており、不要なクロック動作を抑えることで、余計な消費電力が発生しないよう工夫されています。

CKとWCKはどちらも差動クロックとなっており、ダブルデータレート(DDR)方式で動作します。

立ち上がり・立ち下がりの両エッジを使ってデータのやり取りを行う点が特徴です。従来のCKでは立ち上がりエッジのみを使っていましたが、差動化によって両エッジを活用できるようになっています。

WCKはCKの2倍、または4倍の周波数で動作します。CK自体は比較的低速に抑えつつ、内部では高速なWCKを使うことで、全体としての高速化を実現しています。

表2ではクロック構成の一例として、WCKがCKの4倍で動作するケースを示しています。例えば、CKが800 MHzの場合、WCKはその4倍の3,200 MHzで動作します。右側に示しているLPDDR5でも同様に、CKが1,066 MHzの場合、WCKは4倍の周波数になります。

| Signal | Speed | |

|---|---|---|

| LPDDR5 | LPDDR5X | |

| CK_t / CK_c | 800 MHz | 1,066 MHz |

| CA(DDR) | 1,600 Mb/s | 2,133 Mb/s |

| WCK_t / WCK_c | 3,200 MHz | 4,266 MHz |

| DQ(DDR) | 6,400 Mb/s | 8,533 Mb/s |

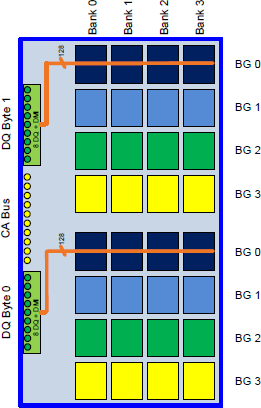

バンクアーキテクチャ

LPDDR5/5Xでは様々なシステム構成に対応するため、複数のバンクアーキテクチャをサポートします。

メモリの内部構造を見ると、「メモリバンク」という考え方があります。

LPDDR5では、このバンク構成にいくつかの選択肢が用意されており、3つのモードが存在します。

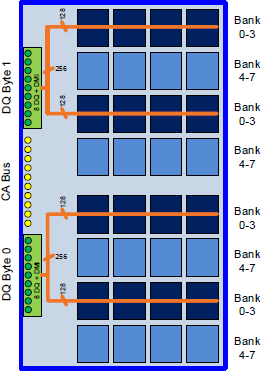

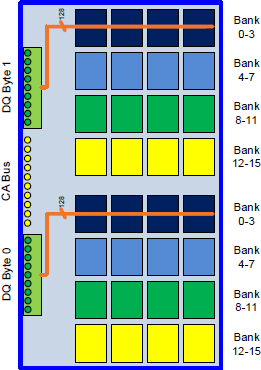

左から順に、バンクグループ(BG)モード、8バンク(8B)モード、16バンク(16B)モードです。

用途や動作条件に応じて、これらのモードを使い分けられるような構成になっています。

ただし、8BモードはLPDDR5のみに適用されます。

LPDDR5Xでは、さらなる高速化(8,533 Mb/s以上)の実現やモードを減らすことによる設計の簡素化などの観点から、8BモードがJEDEC規格によりサポート対象外となったため、BGモードと16Bモードの2つのモードとなります。

出典:JESD209-5

表3では、バンクアーキテクチャの違いをまとめています。

各モードにバンク構成と対応するデータレートの関係を整理しています。

まずBGモードは、「4バンク×4バンクグループ」という構成で、データレートは3,200以上に対応しています。

次に8Bモードです。こちらは名前の通り8つのバンクで構成されており、バンクグループはありません。データレートはメモリが持つ最大スピードまで対応可能ですが、備考欄に記載している通り、対応するのはLPDDR5のみで、LPDDR5Xには適用されません。

最後に16Bモードですが、16個のバンクを持ち、こちらもバンクグループはありません。対応するデータレートは最大3,200までとなるため、どちらかというと低速動作時に使われるモードという位置づけになります。

| Mode | architecture (banks / bank groups) |

data rate | 備考 |

|---|---|---|---|

| BG | 4 / 4 | >3,200 Mb/s | — |

| 8B | 8 / 0 | すべてのデータレート範囲 | LPDDR5のみ適用 |

| 16B | 16 / 0 | ≤3,200 Mb/s | — |

表4では、LPDDR5/LPDDR5XのSDRAM x16モードにおけるアドレッシングをまとめています。

先ほどご紹介したバンクグループモード、8バンクモード、16バンクモードそれぞれで、アドレス構成がどのように変わるのかを数値で比較できるようにしています。

| Bank Mode | BG Mode | 8B Mode (LP5のみ) |

16B Mode |

|---|---|---|---|

| Memory Density | 32 Gb | ||

| Configuration |

128 Mb

× 16 DQ × 4 BG × 4 banks |

256 Mb

× 16 DQ × 8 banks |

128 Mb

× 16 DQ × 16 banks |

| Number of Banks | 4 | 8 | 16 |

| Number of Bank Groups | 4 | — | — |

| Array Pre-Fetch | 256 | 512 | 256 |

| Number of Rows | 131,072 | ||

| Number of Columns(fetch boundaries) | 64 | ||

| Page Size(Bytes) | 2,048 | 4,096 | 2,048 |

| Density | 34,359,738,368 | ||

| Bank Address | BA0-BA1 | BA0-BA2 | BA0-BA3 |

| Bank Group Addresses | BG0-BG1 | — | — |

| Row Addresses | R0-R16 | ||

| Column Addresses | C0-C5 | ||

| Burst Addresses | B0-B3 | B0-B4 | B0-B3 |

| Burst Starting Address Boundary |

128-bit | ||

| Native Burst Length | 16 | 32 | 16 |

各バンクアーキテクチャでサポートされる動作データレートは、以下のとおりです。

表5では、LPDDR5の動作データレートをまとめています。オペレーティングモードやスピードグレードごとに区分しており、WCKとCKの比率などの条件によって、対応する最大データレートが変わる点がポイントです。

続く表6では、LPDDR5Xの動作データレートを同じ形式で整理しています。LPDDR5と比較しながら、各モードで対応可能なデータレートを確認できるようにしています。

| OPERATING MODE / SPEED GRADE | LP5-6400 | |||

|---|---|---|---|---|

| WCK:CK Ratio |

Banks | Burst Length |

DVFSC | Max data rate[Mb/s] |

| 4:1 | BG | BL16/BL32 | Disabled | 6,400 |

| 8B | BL32 | 6,400 | ||

| 16B | BL16/BL32 | 3,200 | ||

| 2:1 | BG | — | Not Supported | |

| 8B | BL32 | 3,200 | ||

| 16B | BL16/BL32 | 3,200 | ||

| 4:1 | BG | — | Enabled | Not Supported |

| 8B | BL32 | 1,600 | ||

| 16B | BL16/BL32 | 1,600 | ||

| 2:1 | BG | — | Not Supported | |

| 8B | BL32 | 1,600 | ||

| 16B | BL16/BL32 | 1,600 | ||

| OPERATING MODE / SPEED GRADE | LP5X-7500 | LP5X-8533 | LP5X-9600 | ||||

|---|---|---|---|---|---|---|---|

| WCK:CK Ratio | Banks | Burst Length | DVFSC | Enhanced DVFSC | Max data rate [Mb/s] | ||

| 4:1 | BG | BL16/BL32 | Disabled | Disabled | 7,500 | 8,533 | 9,600 |

| 16B | 3,200 | ||||||

| 2:1 | BG | — | Not Supported | ||||

| 16B | BL16/BL32 | 3,200 | |||||

| 4:1 | BG | — | Enabled | Disabled | Not Supported | ||

| 16B | BL16/BL32 | 3,200 | |||||

| 2:1 | BG | — | Not Supported | ||||

| 16B | BL16/BL32 | 3,200 | |||||

| 4:1 | BG | — | Disabled | Enabled | Not Supported | ||

| 16B | BL16/BL32 | 3,200 | |||||

| 2:1 | BG | — | Not Supported | ||||

| 16B | BL16/BL32 | 3,200 | |||||

4. 新機能

このブログでは、LPDDR5をベースに、現在主流となっているLPDDR5/5Xにおいて、どのような新機能が追加されているのかを整理しています。こうしたさまざまな追加機能や新機能によって、高速化だけでなく、低消費電力化にも大きく貢献しています。

LPDDR5/5Xの主な新機能は以下のとおりです。

信号品質・エラー耐性

- Link ECC

- コントローラとメモリ間のデータ転送経路で行うエラー訂正

- DFE (Decision Feedback Equalization)

- 高速データ転送時の波形歪み補正

- Pre-Emphasis

- 送信側で信号の変化を事前に強調させ、高速データ転送時の波形歪み補正(DFEと連携)

電力制御(電圧・周波数スケーリング)

- DVFSC (VDD2 Dynamic Voltage and Frequency Scaling Core)

- core電力削減

- EDVFSC (Enhanced-DVFSC)

- DVFSCの拡張版(LPDDR5Xのみ)

- DVFSQ (VDDQ Dynamic Voltage and Frequency Scaling VDDQ)

- IO電力削減

動作最適化による消費電力削減

- Data copy

- IOおよびコア消費電力(IDD4W、IDD4R)削減

- Write X

- 繰り返しデータパターンの書き込み動作における消費電力削減

- PARC (Parity Array Refresh Control)

- 消費電力(IDD5)削減

- Deep Sleep

- 最も低い消費電力動作モード

信頼性・保護機構

- RFM (Refresh Management)

- row hammer攻撃対策

今回はLPDDR5/5Xの基本的な情報をご紹介しました。まずは概要として、全体像を押さえていただく内容になります。

次回以降は、今回の内容をもとに、ポイントを絞りながらより踏み込んだ解説をしていく予定です。少しずつ内容も深くなっていきますので、ぜひ引き続きご覧ください。

導入や評価に関するご相談、製品の詳細仕様についてのご質問は、下記よりお問い合わせいただけます。