AMD社7シリーズ FPGA 設計における DRAM 転送効率の最適化ガイド:MIG とアドレスマッピングの選択

FPGA 設計において FPGA ~ DRAM 間の転送効率が期待値を大幅に下回ってしまった経験はありませんか?

その大きな要因の一つが Bank / Row を切り替える際のコマンド発行にあります。

本ブログでは、FPGA ~ DRAM 間のデータ転送に関する基礎知識とアドレスマッピングによる転送効率の差異について解説します。

MIG、DRAM について

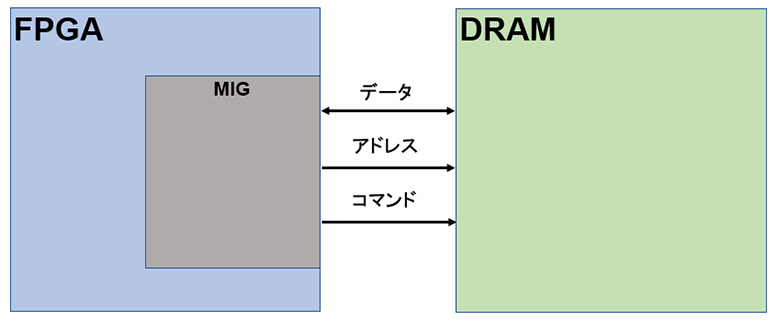

FPGA は DRAM と直接やり取りするのではなく、MIG(Memory Interface Generator)と呼ばれる IP を介して DRAM とアクセスします。

FPGA と DRAM の間では、主に次の3種類の信号がやり取りされることでデータ転送が実現します。

- データ : 読み書きされる情報そのもの

- アドレス : アクセス先を指定する信号

- コマンド : 読み書きの動作を指定する制御信号

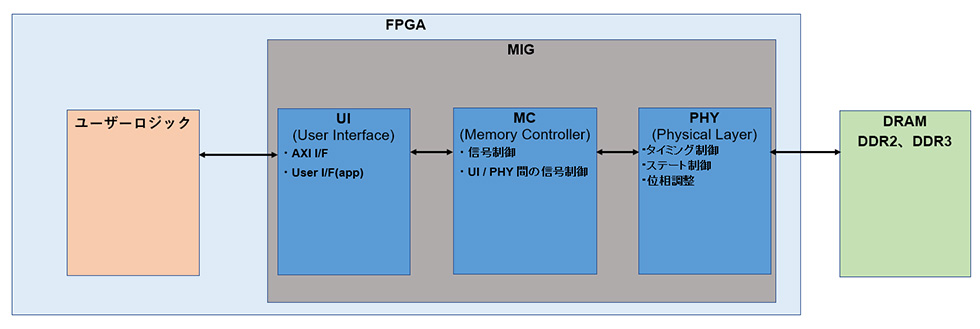

MIG は FPGA と DRAM を接続するための IP です。

ユーザーロジックでは設計が難しいキャリブレーション(信号の位相調整を行うプロセス)や、信号制御をIPが代わりに行いDRAM との通信を可能にします。

MIG は以下の要素で構成されています。

- User Interface(ユーザーロジック側インターフェイス)

AXI、またはネイティブインターフェイスを介して DRAM へのアクセスを提供します。 - Memory Controller(DRAM コントローラ)

UI からのアクセス要求を DRAM コマンドへ変換し、発行タイミングを制御します。 - Physical Layer(DRAM 側インターフェイス)

FPGA とDRAM 間で、遅延・位相をキャリブレーションしながらデータを正しいタイミングで送受信するインターフェイスです。

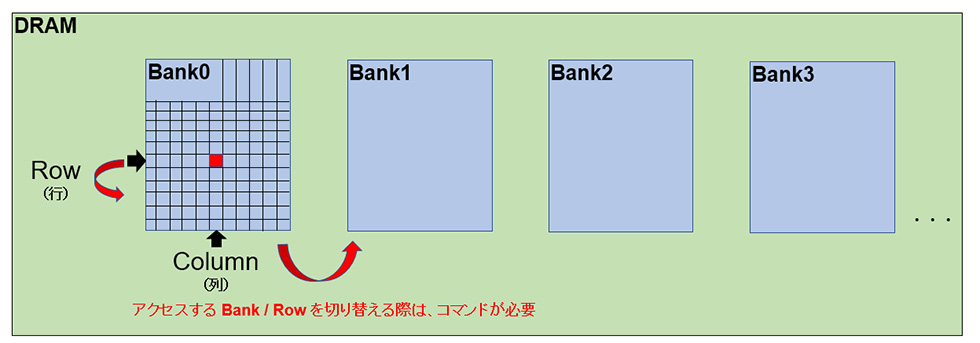

DRAM は階層構造(Bank / Row / Column)を持っているため、異なる Bank / Row にアクセスを切り替える際にはコマンドの発行が必要になります。

- Row 切り替え : Precharge コマンド + Active コマンド(2段階)

- Bank 切り替え : Active コマンドのみ(1段階)

これらのコマンド処理中はデータ転送が停止するため、転送効率が低下します。

そのため、期待通りの転送効率を実現するためには以下の2点について考える必要があります。

- Bank / Row 切り替えが最小限になるようにアクセスパターンを工夫する

- アクセスパターンに適したアドレスマッピングを選択する

アドレスマッピングの違いによる転送効率の違い

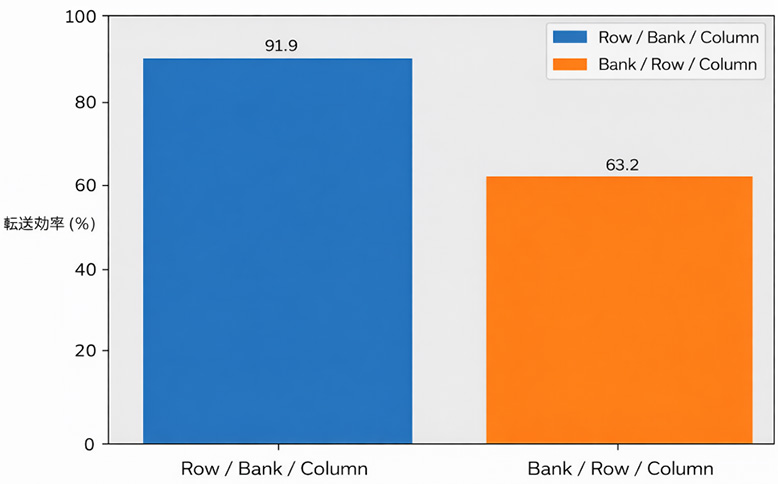

アドレスマッピングの差異によって生まれる転送効率の差について紹介します。

シミュレーション環境は以下のとおりです。

| デバイス | Kintex-7 |

|---|---|

| メモリ | DDR3 |

| 動作周波数 | 800MHz |

シミュレーションで使用したデザインは、Columnから順番にシーケンシャルアクセスを行うデザインです。

以下のグラフを見てわかるように、アドレスマッピングの選択によって転送効率に約1.5倍の違いがあります。

※転送効率は以下の式に則って計算しています。

転送効率(%)= (実効帯域 ÷ 理論帯域) × 100

このように、デザインのアクセスパターンに適したアドレスマッピングを選択しないと転送効率が低下する可能性があります。そのため、適したアドレスマッピングの選択は転送効率の向上を考える上で重要です。

資料ダウンロード

本ブログの内容について、ご興味を持った皆さまへ、

転送効率を向上させるアクセスパターンやアドレスマッピングの選び方について、解説した資料をご用意しております。

また、上記内容に加えて以下の内容についても解説しております。

- DRAM の内部構造とコマンド発行によるステート遷移

- アクセスパターンに適したアドレスマッピングの具体例

- シミュレーションを用いた複数のアクセスパターン、アドレスマッピングでの転送効率比較

ご興味があれば、ぜひダウンロードしていただき、AMD社の7シリーズファミリ FPGA 設計における転送効率最適化のガイドとしてご活用ください。

まとめ

FPGA ~ DRAM間の転送効率改善は、ハードウェア設計において重要な要素です。

本ブログならびに添付資料で解説している基本概念をご理解いただき、アクセスパターンを工夫し、適したアドレスマッピングを選択することで、期待通りの性能を実現できます。

本資料をご参考いただき、皆様の DRAM 転送性能の最適化がより効果的になれば幸いです。

最後までご覧いただきありがとうございました。