AMD社Versal™適応型SoCの進化:最新機能と未来への展望

皆さん、こんにちは。

FPGAを用いた組み込み開発を行う方々にとって注目の製品であるAMD社の適応型SoC(System on Chip)であるVersal™ 適応型SoC。本ブログでは、Versal 適応型SoCにおける新機能、採用事例、そして最新のGen 2情報などを、詳細に解説していきます。

まずは、Versal適応型SoCの基本的な概念とラインナップについて見ていきます。その後、Versalの新機能であるDSPエンジン、AIエンジン、NoC(ネットワーク・オン・チップ)について詳しく説明します。さらに、Versal Gen 1の採用事例を通じて、実際の応用例を具体的に紹介します。最後に、今後の展望としてVersal Gen 2の情報をお伝えします。

*掲載情報は、2024年8月時点の情報です。

目次

Versal適応型SoCとは

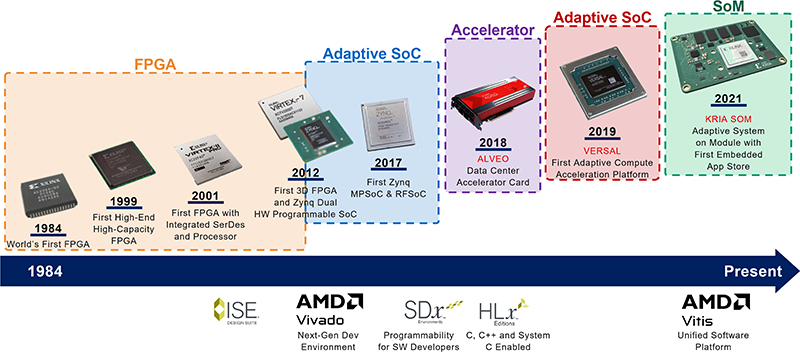

図1はAMD社のFPGAプロダクトラインナップを示しています。

AMD社は、1984年に世界初のFPGAを開発し、その後、Arm CPUを内蔵したSoCタイプの製品を「Zynq™」シリーズとしてリリースしています(図1の青枠部分)。そして、図1の赤枠部分が最新の「Versal」シリーズです。

図1. AMD社FPGAプロダクトラインナップ

本ブログで紹介するVersal適応型SoCは、CPU、FPGAに加え、Intelligentエンジンを搭載しています。

FPGAおよびSoCの特徴の一つとしては、長期供給が挙げられます。

AMD社は、15年以上の供給をポリシーとして継続しており、Spartan™ 6および7シリーズにおいては、少なくとも2030年、2040年までには供給することを発表しています。

Spartan 6は2009年にリリースされ、今年で15年目を迎えますが、20年を超える供給を約束しています。

今まで通り、また今後も安心してご検討いただければと思います。

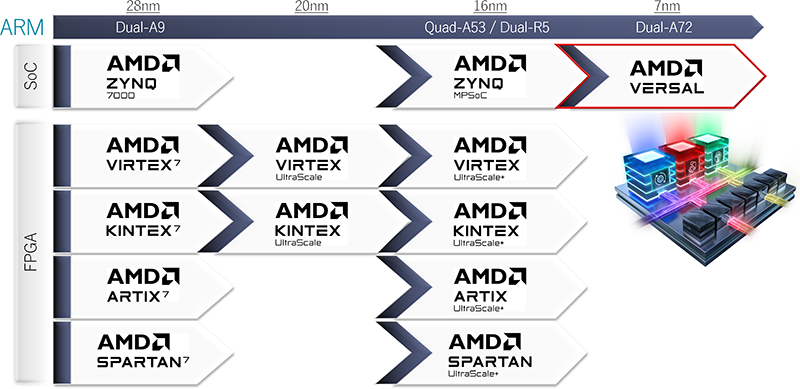

図2がデバイスのポートフォリオになります。SoCタイプのZynq、Versal、そしてFPGAはハイエンドからVirtex™、Kintex™、Artix™、Spartanと幅広いファミリーを用意しています。

本ブログでは「Versal」についてお伝えさせていただきます。

図2. FPGA/SoCラインナップ

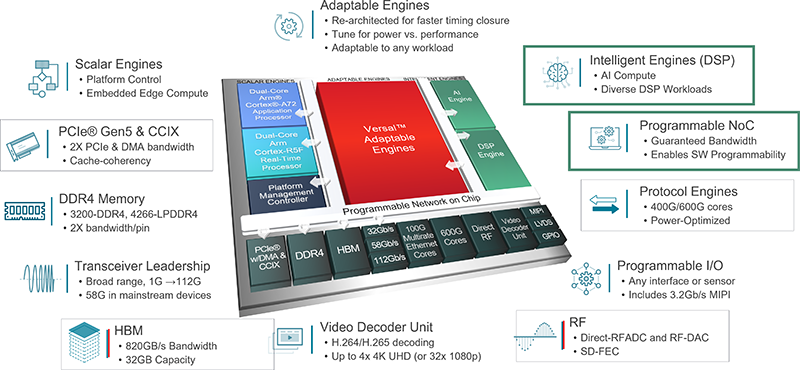

図3が「Versal」のアーキテクチャになります。大きな構成としては、青色のCPU、赤色のFPGA、そして緑色のIntelligent Engineの3つの領域で構成されています。

このIntelligent Engineの中にはAI EngineとDSP Engineがあり、前述した青色、赤色、緑色の3種類のエンジンおよびメモリコントローラなどのハードブロックを接続しているNoC(ネットワーク・オン・チップ)があります。

「Versal」の最大の特徴は、図3内の枠で囲った2項目です。

図3. Versal アーキテクチャ概要

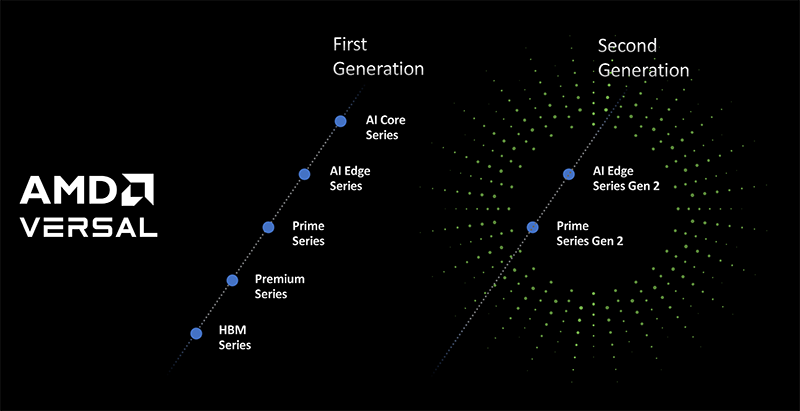

AMD社が提供する「Versal」は、現在、図4のように5つのシリーズで展開されています。この中でも、AI Coreシリーズ、AI Edgeシリーズ、PremiumシリーズにはAIエンジンが搭載されています。これらのAIエンジンを活用することで、GPUよりも高い性能を実現できるとされています。

図4の右側にあるのがSecond Generationで、つい先日発表されたものです。AI EdgeとPrimeに関してはGen 2という名前が付けられています。

また、Gen 2のラインアップも発表されており、量産デバイスは2025年末よりリリース予定です

(2024年8月時点の情報です)。

図4. Versal ラインナップ

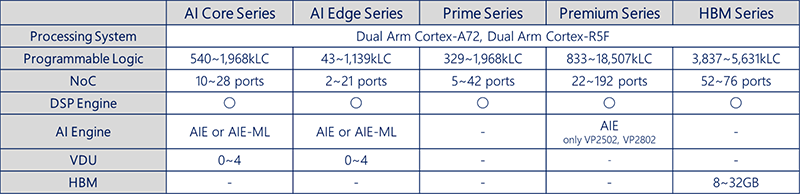

表1. Versal シリーズについて

さて、シリーズのロジックサイズやCPU部分の構成に関する情報を表1にまとめてみました。Cortex-A72、Cortex-R5Fを搭載し、AI Engine、Video Decode Unit(VDU)、HBMの有無によってシリーズが分けられています。

表2. Gen 2について

次に表2にGen 2についてまとめています。

Gen 2については、CPU部分、AI Engineに違いがあります。今回は細かいシリーズの説明はしませんが、大きな特徴はこちらの3つです。

Intelligent EngineはDSP EngineとAI Engineがあります。

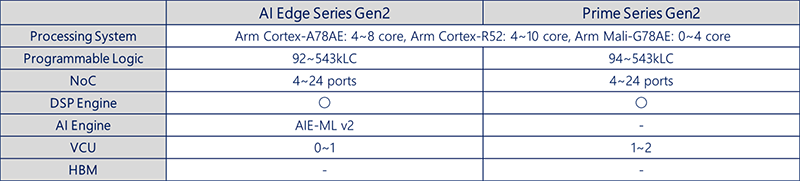

まず、DSP Engineは既存のFPGA領域にあったDSPエンジンの進化版で、FPGA領域にあるブロックです。FP32など新規に対応している機能があります。

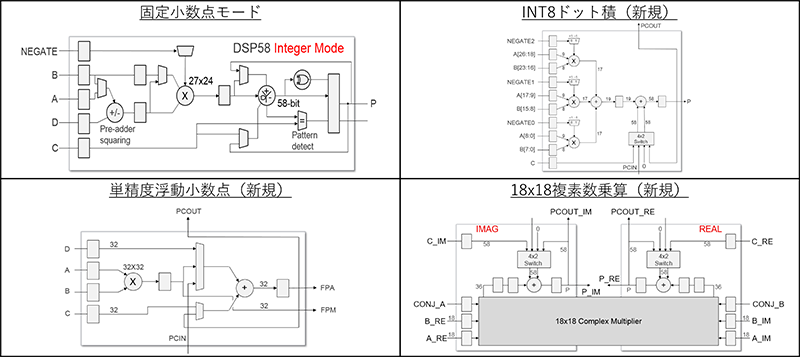

次に、AI Engineは1.3GHzで動作する演算ユニットとメモリが1つのタイルで構成されています。AI推論以外にも、画像処理も高速化できる汎用的に使用できるエンジンです。

NoCはNetwork on Chipの略で、AXIインタフェースがハードブロックとして実装されています。CPU、FPGA、Intelligent Engine、メモリコントローラ等の各種ハードブロックが相互接続されています。

まとめると以下のとおりです。

- Versalの主な特徴

- DSP Engine

- DSPブロックの進化版

- FP32対応等、単体性能が向上(リソース最適化)

- AI Engine

- 1.3GHz VLIW/SIMD ベクトル型プロセッサ

- 演算ユニットとメモリが1つのタイルに格納

- NoC(Network on Chip)

- AXIインタフェースをハードブロック化

- CPU、FPGA、Intelligent Engine、各種ハードブロックが相互接続

それでは、次項では「Versal」の新機能として追加されたDSP Engine、AI Engine、NoCに焦点を絞りご紹介していきます。

Versal 新機能

DSP Engine

DSP Engineは、既存のFPGA領域にあったDSPブロックを大幅にアップデートした進化版です。各モードがあり、固定小数点モードではビット幅が拡張され、ドット積による行列演算が可能になりました。従来のDSPブロックと比較すると、演算効率が1.5倍向上しています。

FP32(単精度浮動小数点)も新機能として追加されました。これまではDSPブロックとロジックを組み合わせる必要がありましたが、DSPブロック単体で処理ができるようになりました。

複素数乗算については、2つのブロックを組み合わせて構成することで、従来よりも30%のリソースを削減できます。DSPブロック単体で対応できる範囲が増え、より少ないリソースで演算量を増やせるのは非常に良い特徴です。

図5. DSP Engine

出典: AMD, Versal ACAP DSP Engine Architecture Manual (AM004)

AI Engine

ここからは、AI Engineについてお話します。

このAI、は人工知能のAIではなく、Adaptable Intelligent という造語となります。ですから、AI処理以外も実行可能です。FIRやFFTなどの大規模計算が必要な場合に優秀です。

図6. AI Engineのアーキテクチャ

続いて「Versal」のコンセプトについてご紹介します。

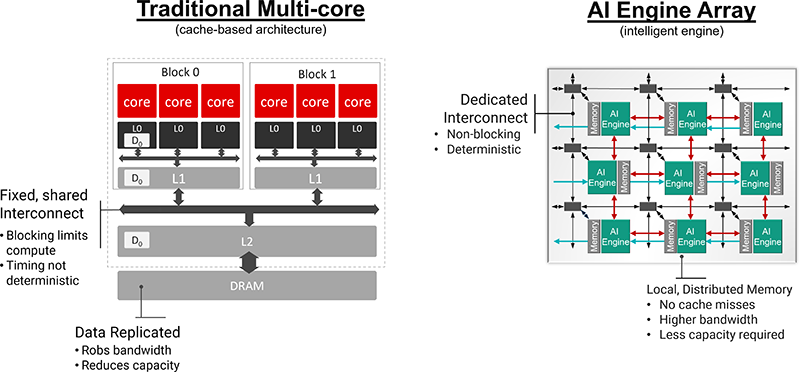

図7は既存の構成図とAI Engine構成図の比較となります。図7の左側は既存の構成図です。複数のコアの下にキャッシュメモリが構成されていて、外部メモリに接続されています。このような構成だと、コア数または動作周波数が増加していくと、インターコネクトやキャッシュがボトルネックになりかねません。

それに対して図7の右側がAI Engineの構成ですが、コアのすぐ隣にメモリを持っています。タイル同士の接続やメモリ自体をカスケードするといった構成も取れるため、スムーズに演算をしていくことが可能です。

図7. 既存システムとAI Engineの比較

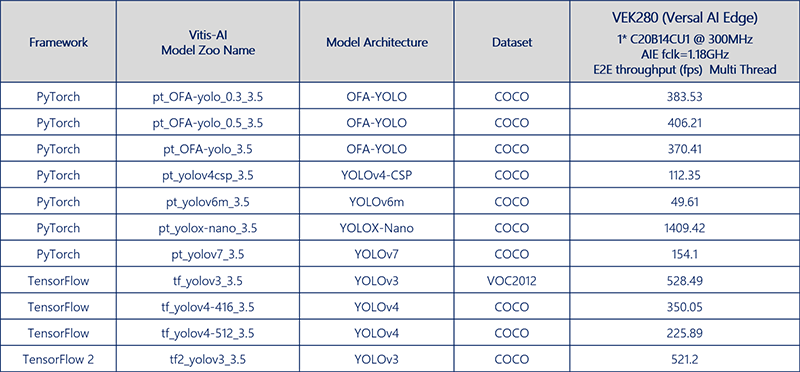

次の表3および表4にAI EngineにおけるAI パフォーマンスと画像処理性能に関する実際のベンチマーク結果をお見せします。

表3. AI Engine AI パフォーマンス

出典: Vitis AI Model Zoo — Vitis™ AI 3.5 documentation (xilinx.github.io)

表3にAI Engine 置けるAI パフォーマンスを示しました。

AI性能については、よく使うYOLOというモデルのところだけを抜粋しています。

左から順にフレームワーク、使用モデル、モデルアーキテクチャ、データセット、実際のフレーム/秒、FPS、E2E throughput(エンド・ツー・エンドのスループット)を示しています。

結果をみると、300fpsも出ており、非常に良い結果となっています。

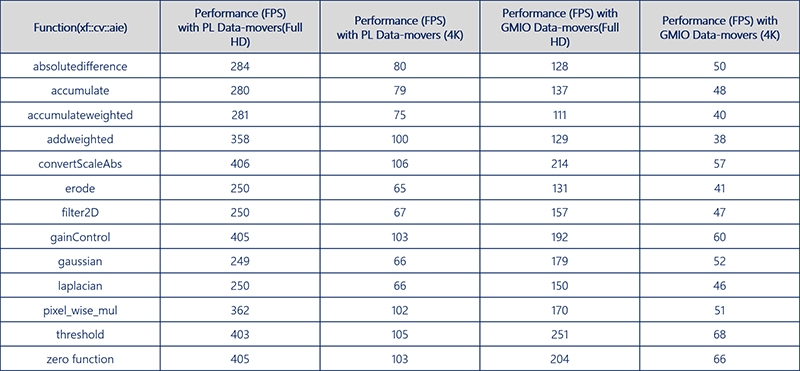

表4. AI Engine 画像処理性能

出典: xilinx.github.io/Vitis_Libraries/vision/2022.1/index.html

Vitisで使用できるライブラリをそのままVitis Libraryと呼び、いくつかのライブラリを用意しています。

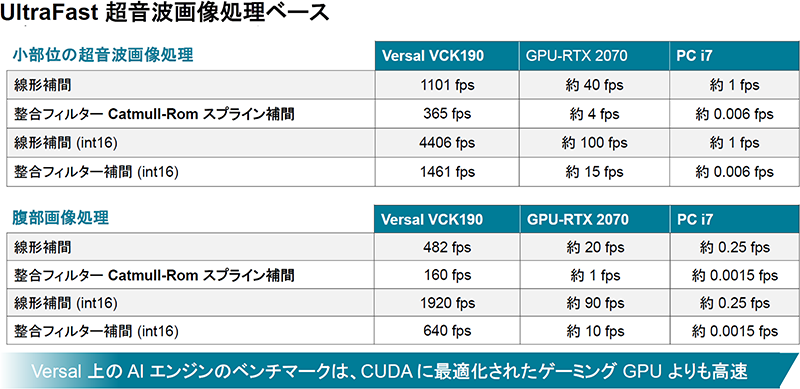

図8. AIエンジンにおける画像処理のユースケース

図8は超音波の画像処理の実測値になります。左側がVersal、真ん中がGPU、右側がCPUで実行した際の結果です。

一目瞭然、桁が全然違うことがお分かりいただけると思います。

こちらは医療機器を対象としておりますが、高解像度のデータをリアルタイムで処理しなければならないケースでは、AIに限らず、GPUよりも圧倒的な性能を発揮します。

NoC

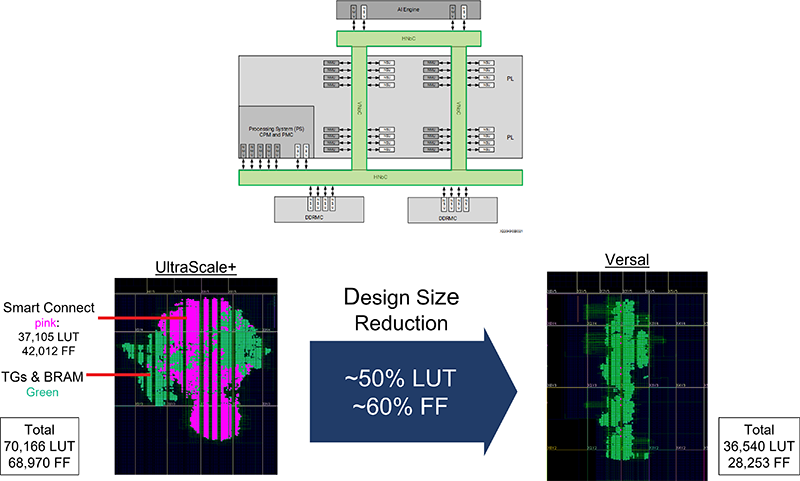

次にNoC(Network on Chip)についてです。

NoCは、デバイスの中にAXIインタフェースが張り巡らされている形をしています。

図9. NoCについて

従来AXI Smart ConnectなどのインターコネクトをFPGA領域に実装する必要がありましたが、ハードブロックで実装されているため、ロジックは使用しません。

図9のとおりLUTは50%削減という結果が出ています。ロジックを効率的に使うことができるようになります。

それでは、ここからはAMD社のVersal Gen 1における採用事例について見ていきましょう。

Versal Gen 1の採用事例

採用事例①

まず、キヤノン株式会社様にご採用いただいた事例を紹介します。

3D空間でバーチャルカメラを操作してスタジアム内を自由に動き回り、試合中にフィールド上の選手の中にいるような身体感覚を疑似体験できる、全く新しい没入感のある映像体験ができる「Free Viewpoint Video System」。

Versalを使用することで超低レイテンシー処理により、ライブリプレイ映像の生成をほぼリアルタイムで実行可能です。

AMD(米国本社:米カルフォルニア州サンタクララ、社長兼CEO:リサ・スー)は本日、スポーツのライブ放送やウェブキャストの視聴体験に革命を起こすと期待されているキヤノンのFree Viewpoint Video Systemに、AMD AI Engineテクノロジーを搭載した Versal™ AI Core シリーズが採用されたことを発表しました。

AMD(2022/6/30)

AMD、キヤノンの画期的な自由視点映像システムで リアルタイムのエッジAI処理を実行、スポーツ中継を変革

【プレスリリース】 https://www.amd.com/ja/newsroom/press-releases/2022-06-29-amd-ai.html から取得

採用事例➁

次にNEC様の事例を紹介します。

NEC様では、MIMOシステムを使って「ミリ波5G」の実証実験で成功を発表しています。

Tokyo, January 25, 2021 - NEC Corporation (NEC; TSE: 6701) announced today it has demonstrated multiple highly stable simultaneous terminal connections and transmission capacity in a real office environment through distributed-MIMO (*1) in the 28 GHz millimeter-wave frequency band. This demonstration achieved approximately 3 times the number of simultaneous connections and transmission capacity compared to cases without distributed-MIMO in the 28 GHz frequency band. Moreover, transmission deterioration from obstacles was also reduced.

NEC Corporation(参照日2021/1/25)

NEC millimeter-wave distributed-MIMO technique triples the number of simultaneous connections and transmission capacity in a real office setting

【プレスリリース】 https://www.nec.com/en/press/202101/global_20210125_01.html から取得

ミリ波周波数帯を使った5Gは、4Gと比較すると最大で10倍の速度を提供するといわれていますが、その一方で、「範囲が限られていることや壁やその他の障壁を貫通することが難しい」といったさまざまな要因の技術的な課題があります。

それを解決したのがVersalです。

AMD adaptive computing technology enables advanced signal processing capabilities for massive MIMO antennas and beamforming

AMD(参照日2024/8/6)

NEC Deploys Massive MIMO Radio Unit Powered by AMD Versal™ AI Core Adaptive SoCs

【プレスリリース】 https://www.amd.com/content/dam/amd/en/documents/resources/case-studies/nec-case-study.pdf から取得

Versal Gen 2情報

Versal Gen 2の概要

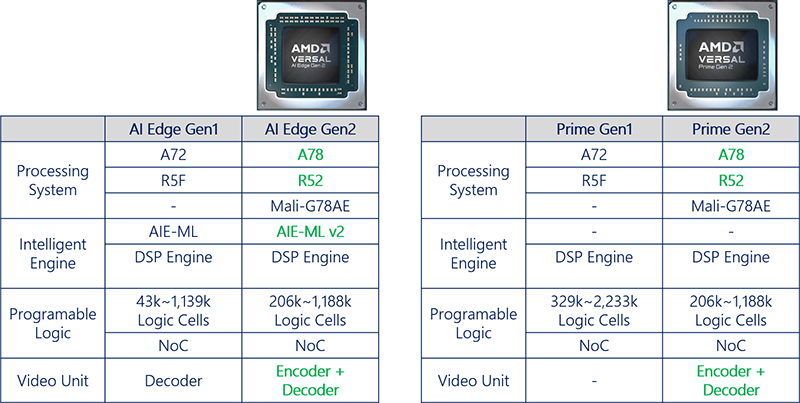

Gen 2はAI EdgeとPrimeの2つが現在発表されています。緑色の部分がアップデート箇所です。

CPUコア、AI Engineがver.2になり、Video Unitではエンコードもサポートします。

図10. Versal Gen 2 概要について

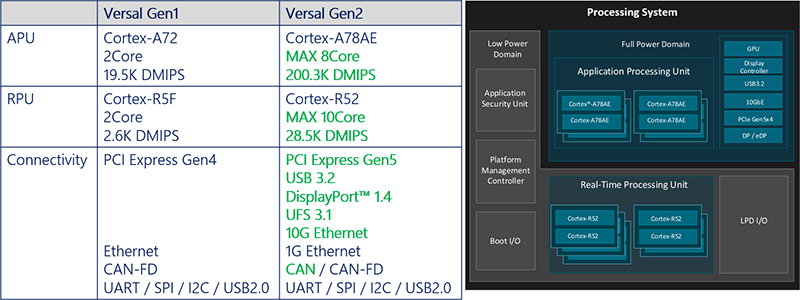

APUがCortex-A72からA78AEにアップデートしてコア数も増え、DMIPSでみると、約10倍となりました。RPUもCortex-R52になり、DMIPSについても約10倍です。

また、インタフェース部分も、USB3.2やDP1.4、10GbE等 高速インタフェースのサポートが大きく増えています。

図11. Versal Gen 2 処理システム

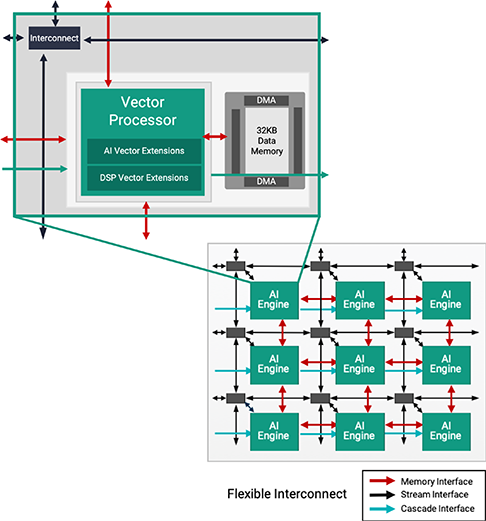

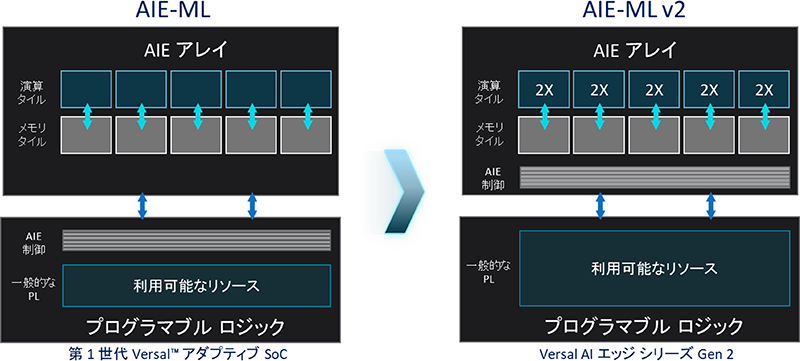

AI EngineはGen 1で使用されていたAIE-MLをベースに AIE-ML v2 に進化し、タイル当たり最大2倍の演算処理能力へと向上しています。大きな特徴はAIEアレイの中に制御プロセッサが内蔵されている点です。

AI Engineへデータ転送するロジックはこれまでFPGA領域に必要でしたが、AI Engine自体に組み込まれているように見えます。

図12. Versal Gen 2 AI Engine

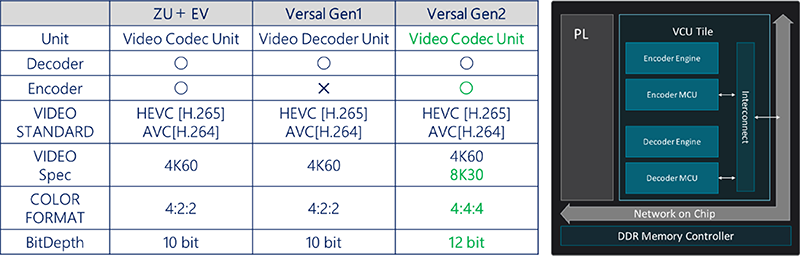

Gen 1ではデコードのみサポートしていましたが、Gen 2ではエンコードもサポートしています。

2つカスケードすれば、8K30pまでサポートしています。

図13. Versal Gen 2 ビデオコーデックユニット

Versal Gen 2における採用事例

こちらは、株式会社SUBARUとAMD社の協業開始に関するニュースです。SUBARU様では、車の衝突防止機能「EyeSight」にVersal™ AI Edge Series Gen 2を採用しています。SUBARU様は次世代のEyeSightを通じて死亡事故ゼロの実現を目指しており、協業を発表しています。

株式会社SUBARU(東京都渋谷区 代表取締役社長:大崎 篤 以下、SUBARU)はAMD(カリフォルニア州サンタ・クララ 会長兼最高経営責任者(CEO):Dr. Lisa T. Su)と、2030年死亡交通事故ゼロ*1実現に向け、ステレオカメラの認識処理とAI推論処理を融合し最適な判断結果を出力可能なSoCの最適化に関する協業を開始することを発表しました。

SUBARUは、AMDにて発表されたVersal™ AI Edge Series Gen 2を採用し、同社とともに最先端のAI推論性能や超低遅延な演算処理を低コストで実現するため、SoC最適化に向けた回路設計を開始します。当社が長年培ってきたステレオカメラの認識処理にさらなる性能向上を合わせ、2020年代後半の次世代EyeSightに搭載することを目指します。

株式会社SUBARU(参照日2024/4/19)

AMD、キヤノンの画期的な自由視点映像システムで リアルタイムのエッジAI処理を実行、スポーツ中継を変革

【プレスリリース】 https://www.subaru.co.jp/news/2024_04_19_154136/ から取得

資料ダウンロード

本ブログでご紹介した内容を資料で確認されたい場合は、以下よりダウンロードが可能です。

まとめ

いかがでしたでしょうか。

AMD社のVersalは3つの特徴があり、DSP Engine、AI Engine、NoCがありました。

Versalシリーズは、キヤノン様やNEC様でも採用実績があります。

Gen 2のリリースは2025年末頃です。CPU、AI Engine、VCUがアップデートされました。

今後もPALTEKではAMD社の最新情報やTipsをお届けしていきます。