非同期転送に潜むCDC問題を、自動で可視化・検証

FPGA / SoC設計の32%がCDC起因で再設計(※)

膨大な非同期信号を、人手に頼らず解析可能

※ Wilson Research Group 2024

CDC検証とは?なぜ必要なのか

CDC検証とは、異なるクロックドメイン間でやり取りされる信号に潜むメタスタビリティやプロトコル違反などの問題を検出・防止するための検証手法です。複雑化するFPGA / SoC設計では、シミュレーションや目視確認だけではこうした問題を見逃しやすく、CDC検証が重要になります。

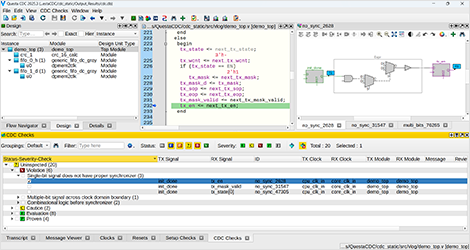

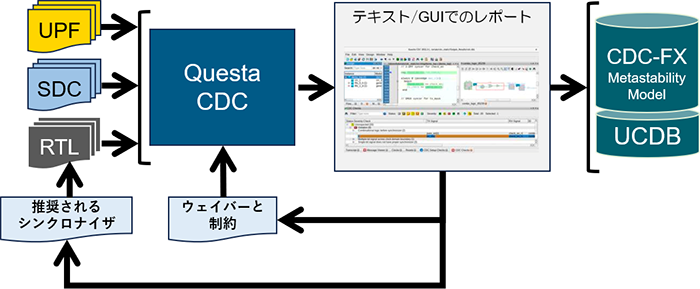

Questa CDCは、CDC検証に加えて、CDC解析(静的解析)を可能にするツールです。

非同期転送における主な課題

複数クロックドメインの管理

今日のデザインでは、多数の非同期クロックを使用しており、管理が複雑化しています。

メタスタビリティリスク

セットアップ / ホールド違反による不安定な動作が発生し、システム全体の信頼性を脅かしています。

増加する発生頻度

半年に一度だった不具合が毎週発生するようになり、開発スケジュールに深刻な影響を与えています。

目視確認の限界

数万の非同期信号を手動でチェックするのは現実的ではなく、かつシミュレーションでは検出することができないため、見落としのリスクが常に存在します。

Questa CDCとは

Questa CDCは、Siemens EDAが提供するCDC検証・解析ツールで、複数クロックドメインを含むFPGA / SoC設計において、非同期転送に関する問題を自動的に検出・可視化します。

Questa CDCが解決する3つの核心的ソリューション

1. シンクロナイザチェック

構造解析により、シンクロナイザの欠如・誤用を自動検出

2. プロトコル検証

転送プロトコル用アサーションを自動生成&シミュレーションで検証

3. メタスタビリティ検証

RTL段階で影響を再現・検証

Questa CDCの技術的特長

AIによる擬似エラー削減

静的解析における擬似エラーをAIが自動分析し、誤情報の少ないレポートを生成

高度な自動化

シンクロナイザに依存するプロトコルの認識からアサーション生成、メタスタビリティモデル挿入まで自動実行

大規模設計対応

ブロックレベル解析結果を上位階層で再利用し、SoC / FPSoC等の大規模設計にも対応

導入効果

検証効率向上

インストール後、迅速に検証効率の向上を体感

精度向上

擬似エラーを大幅削減し、真の問題に集中

再設計リスク低減

CDC起因の再設計リスクを抑制

技術仕様

対応OS

Windows 11 / Linux RHEL 8/9 / Linux CentOS 8.2 / Linux Rocky 9 / Linux SLES 15

統合環境

Questa One ソリューション(共通コンパイラ・GUI・Visualizerデバッグ環境)

技術資料で分かること

- Questa CDCの主要機能と仕組み

- CDC解析 / 検証の具体的アプローチ

- 大規模SoC / FPSoC設計での活用ポイント

設計・検証エンジニア向けの実践的な技術資料です。

Questa CDCの資料ダウンロードはこちら

シーメンス EDAのことなら

PALTEKにご相談ください!