Questa Lint機能

Lintチェックに必要な全ての機能をall-in-oneで装備

- Verilog/SystemVerilog/VHDLと言語混在に対応

- テストベンチなどを必要とせずRTLのみで静的検証

- 静的構造解析により後工程で問題となる記述の早期特定により大きな手戻りを防止

- 社内IPやサードパーティIP、アウトソースしたRTL受け入れの品質スコアリング

- STARC, RMM, ISO26262, DO254のルールセットを装備

- AMD Xilinx, Altera, MicroChip, Latticeの各FPGAベンダ向けルールセットを装備

- ISO26262の認証ツール

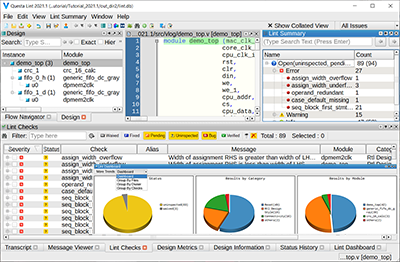

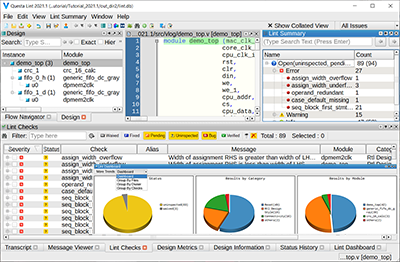

容易な実行とデバッグ

- ウィザードを使用したGUI実行とバッチ実行

- Windows, Linuxオペレーティングシステムをサポート

- テキスト、スケマティック等の可視化により問題点を直感的に把握

- 直近の変更に起因する新たな問題のみをレポート

- 事前にコンパイルされたFPGAライブラリよる迅速な立上げ

Questa統合環境

- Questa共通の完全なLRM準拠によるコード可搬性の確保

- Questa共通のユーザインタフェース、ステータスフローによる最小の学習曲線

チームによる共同デバッグ

- キューイング機能で複数の設計者、プロジェクトで共用

- チームメンバーにアサインし記述の改修、クリーンナップを並行して作業可能

指標による品質維持

- 要件に関連付けされた指標をトレンド分析によりプロジェクト終了まで一貫性を確保

- CI (Continuous Integration) によりクリーンな設計を維持

Questa Lint特長

即効性が期待できるプロダクト

Questa Lintは特定のメソドロジに向け事前に定義された設定と、開発フローに沿ったゴールが提供されており、すぐに価値ある結果が得られます。特定の設計属性を適用することでインテリジェントな推論機能により素早く問題を発見することができます。

データ解析に基づく支援

独自のデータ解析技術を用いてノイズ抑制された実用的な結果を提供します。推定された意図とは異なる結果をもたらす既知の問題や疑似違反に関する分析により、修正が必要な問題のみを重要度に応じてレポートします。

統一された結果管理と操作性

Questa LintはQuesta CDC/Formalなど他のシーメンスプロダクトと同じステータスフローを共有し、リントチェックだけでなく様々な解析を行い、適切な指標とフィードバックが得られるようQuesta統合環境全体としてのソリューションを提供しています。

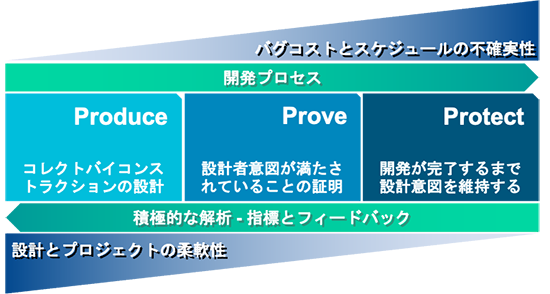

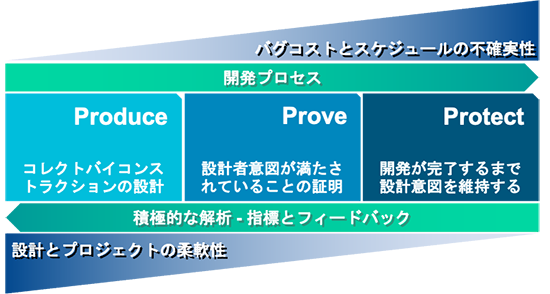

開発プロセスを俯瞰した Questa Design Solutions の戦略

開発プロセスを俯瞰した Questa Design Solutions の戦略

インクリメンタル処理で変更箇所のみレポート

Questa Lintは最新の修正で発生した新たな問題のみをレポートすることができます。最後の変更以降の問題に注目することで、修正サイクルを加速することができます。

チームによる共同修正

Questa Lintでは個々の問題を担当者に割当てられます。チーム全体が協力してクリーンナップを行い、修正の進捗を追跡するコラボレーションメカニズムをサポートしています。

応用分野

デザイン・スコアリング

今日の開発フローでは、内部開発、外部調達を問わず、大量のIPを統合する必要があります。インテグレータの仕事は、必ずしも一緒に動作するように作られていない多くのIPをまとめ上げる困難なものです。Questa Lintは設計品質のスコアリングのメカニズムを提供し、どのIPやブロックが後段で問題を起こしそうか迅速に把握することが可能です。これらのスコアは、独自のアルゴリズムにより生成され、その結果、注意が必要なIPやブロックをより早く特定することができます。

メソドロジのサポート

IP、FPGA、またはSoC開発ごとに、あらかじめ設定されたメソドロジが実装されており、すぐに結果を得られるように設計されています。STARC、ISO26262、DO254など業界標準をサポートするチェックセットも用意されています。

トレーサビリティのサポート

標準に準拠した開発フローでは要件へのトレーサビリティと所定の品質レベルの両方を示さなければなりません。一部の規格では品質指標の時間的推移の提示も求められます。Questa Design SolutionsはSiemensの要件管理に関する長年の蓄積を活用し、機能を実現しています。