潜在的な不具合を見つけるFPGAデバッグツール「VSTAR」

FPGAやSoCにおけるレアな不具合を短時間で解決に導くデバッグツール、「VSTAR(ブイスター)」をご存知ですか?

VSTARは、 ザイリンクス社のVivado® Design Suite HLx editionに対応しており、余計な手間暇をかけずに設計フローを進めていくことが可能です。

今回は、設計者の皆さんの時間効率を高めるVSTARについて紹介いたします。

目次

VSTARとは

従来のChipScope™ Proを用いて行うデバッグ方法では、内部の状態遷移の不正動作をエンジニア自身が想定し、この条件を論理として回路に組み入れて、その前後の信号を観測しています。

そのため、大規模、複雑な回路におけるバグや、再現性の低いバグでは不正動作箇所における波形キャプチャの取得をするには多くの時間を要していました。

このような課題は、ベリフィケーションテクノロジー社のVSTAR2.0を活用すれば解決できます!

VSTARは状態遷移の不正動作を考えることなくイベントにおける状態遷移を観測し、不正と思われる動作を自動で検出することが可能です。

このためバグの発生個所を早期に発見することが容易になります。

また、VSTARは不正と考えられる信号波形を自動で抽出し表示することも可能なツールです。

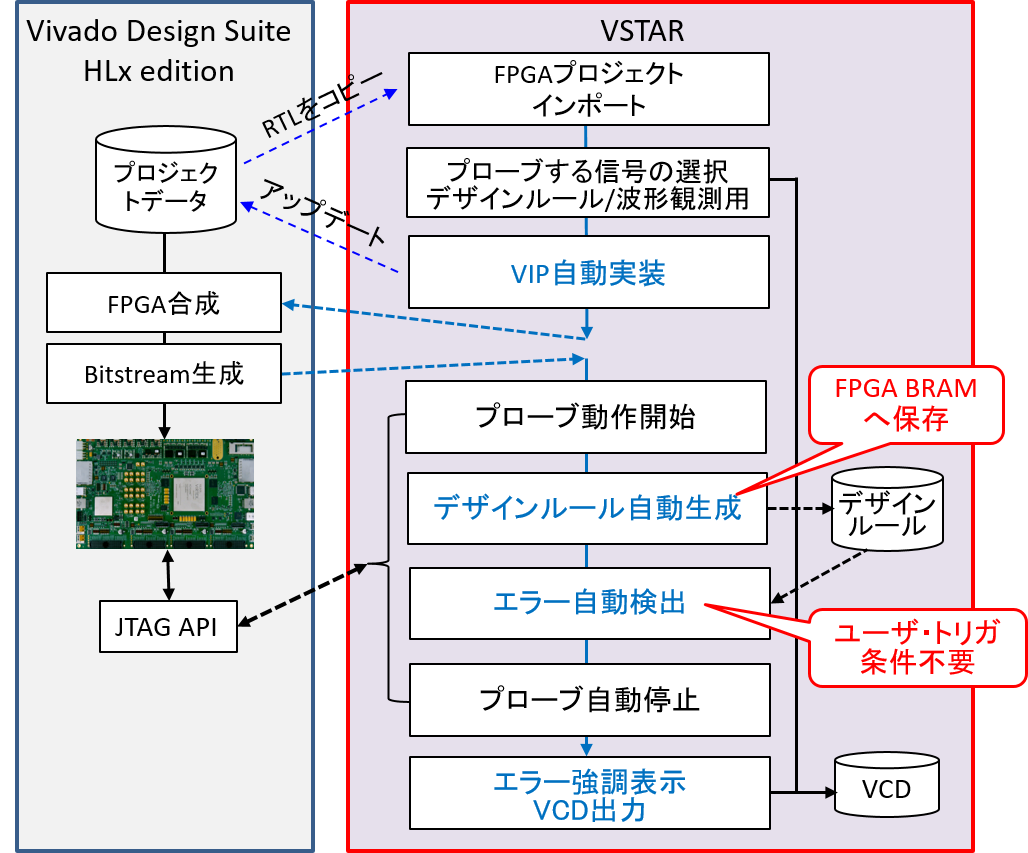

Vivado® Design Suite HLx editionで作成したプロジェクトデータをVSTARの専用GUIよりインポートし、プローブする信号の選択やデザインルール等を設定いただきます。

設定された内容に基づき専用GUIからVIPを自動実装しVivado® Design Suite HLx editionからFPGAやSoCへ合成します。

図 VSTARを活用したデザインフロー

観測開始後、不正と思われる動作を検出した場合、FPGA BRAMへイベント遷移や波形キャプチャが保存されますので、JTAG経由で専用GUIより不正箇所を確認していただくフローとなります。

不正箇所のみをBRAMへ保存するため、今までのようにBRAMの容量が足りず再合成するなどの手間も削減することが可能になります。

事例

ハイスピードカメラの例を紹介します。

ハイスピードカメラにおいて、画像処理のパイプラインの途中で画素が欠落するようなエラーが発生した際、今までは設計者が不正な状態遷移を想像し、この条件を論理として回路に組み入れ信号を観測していました。

しかし、想定するポイントが異なってしまうとバグ箇所を発見するまでにかかる工数が増大します。

このようなケースでVSTARを活用いただくと、瞬時にバグ箇所の特定に至ることができます。

まとめ

「デバッグはしっかりとしたいけど、あまり時間をかけたくない」という方も多いのではないでしょうか。

VSTARは状態遷移の不正動作を考えることなく、不正と思われる動作を自動で検出します。

特に再現性の低いバグを見つけるには、VSTARは非常に有用なツールです。

2020年7月31日まで無償キャンペーンを実施していますので、ご興味のある方は是非お問い合わせください。

今回の記事を資料化したものはこちらからダウンロードできますので、ご活用ください。