HDL PROJECT Block Memory Generator(8.4)でURAMを使用する方法(一例)

FPGA設計中にBlock Memory GeneratorでURAMを使用するケースがありました。

HDL PROJECTのため、URAMを使用するにはXPMから生成する必要がありますが、BLOCK DESIGNを使用する場合においては、Block Memory GeneratorからURAMを選択することが可能です。

そこで本ブログでは、HDL DESIGNを使用したIPIのモジュールを読み出し方法で、Block Memory GeneratorからURAMを選択する方法を紹介します。

- TOOL

- : Vivado™ Ver 2020.2

- DEVICE

- : ZCU104 Evolution Boar

- IP

- : Block Memory Generator(8.4)

このブログは「FPGA設計ブログ一覧」の

1. コーディング・IP設定・プリミティブ設定 のひとつです。

目次

- 背景

- 現象

- 方法

- 1. 生成用PROJECTを新規作成

- 2. 新規BLOCKデザインを作成

- 3. IPを追加

- 4. IP設定

- 5. 外部PORTを生成

- 6. RTLを生成

- 7. RTL PROJECTにインポート

- 8. ファイルインポート

- おわりに

背景

FPGA(RTL BASE)設計中にURAMを使用する時に、Block Memory GeneratorでURAMの選択ができない場合に、URAMを使用するにはXPMから生成することが必要です。

現象

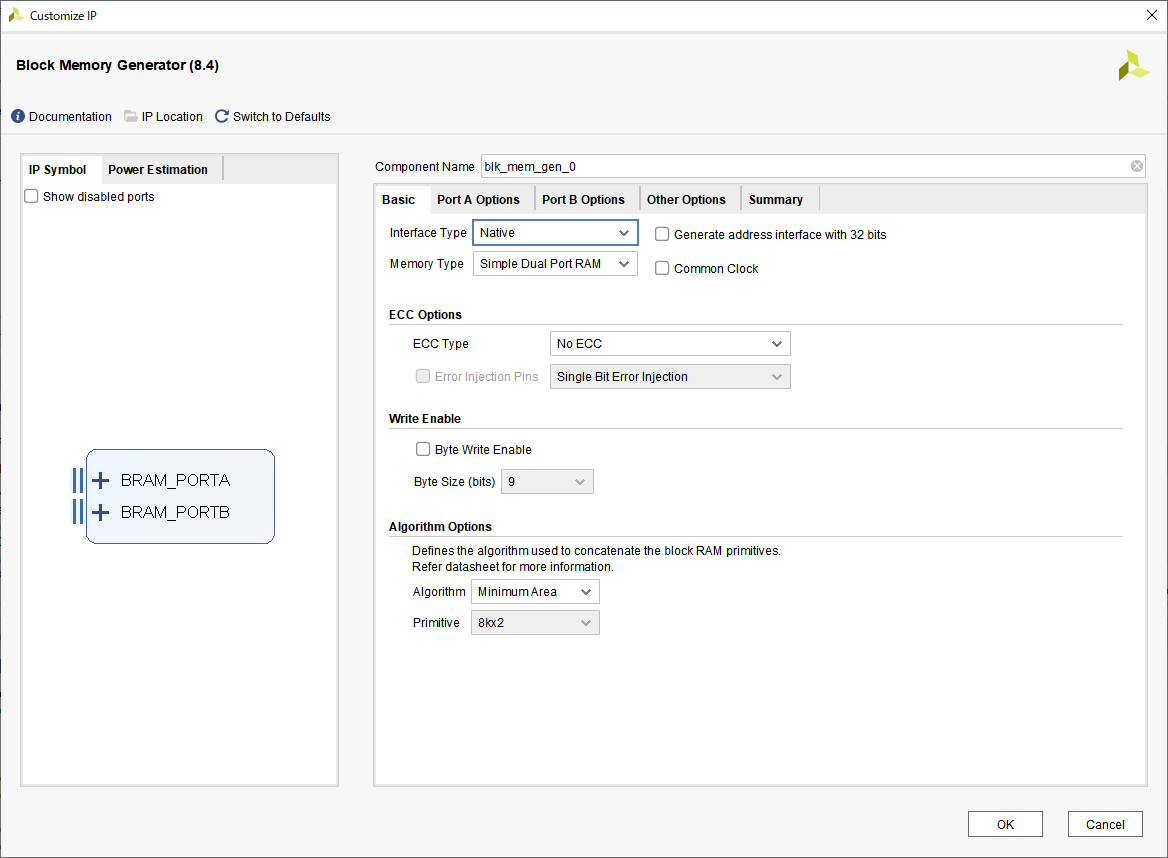

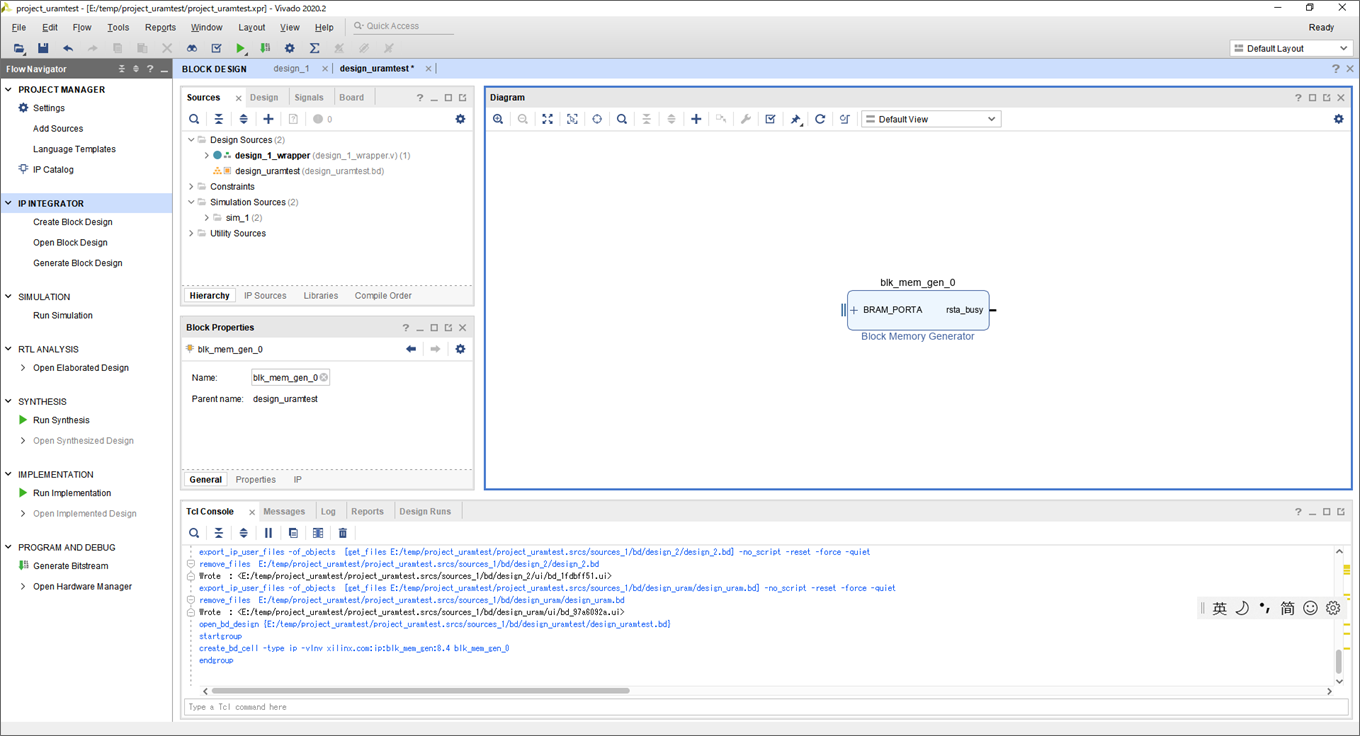

Vivado™でPROJECTを作成し、IP catalogからBlock Memory Generatorを開くと下図のようになり、BRAMとURAMの選択が表示されません。(XPMから生成する必要あり)

出典:Vivado™ ML Edition

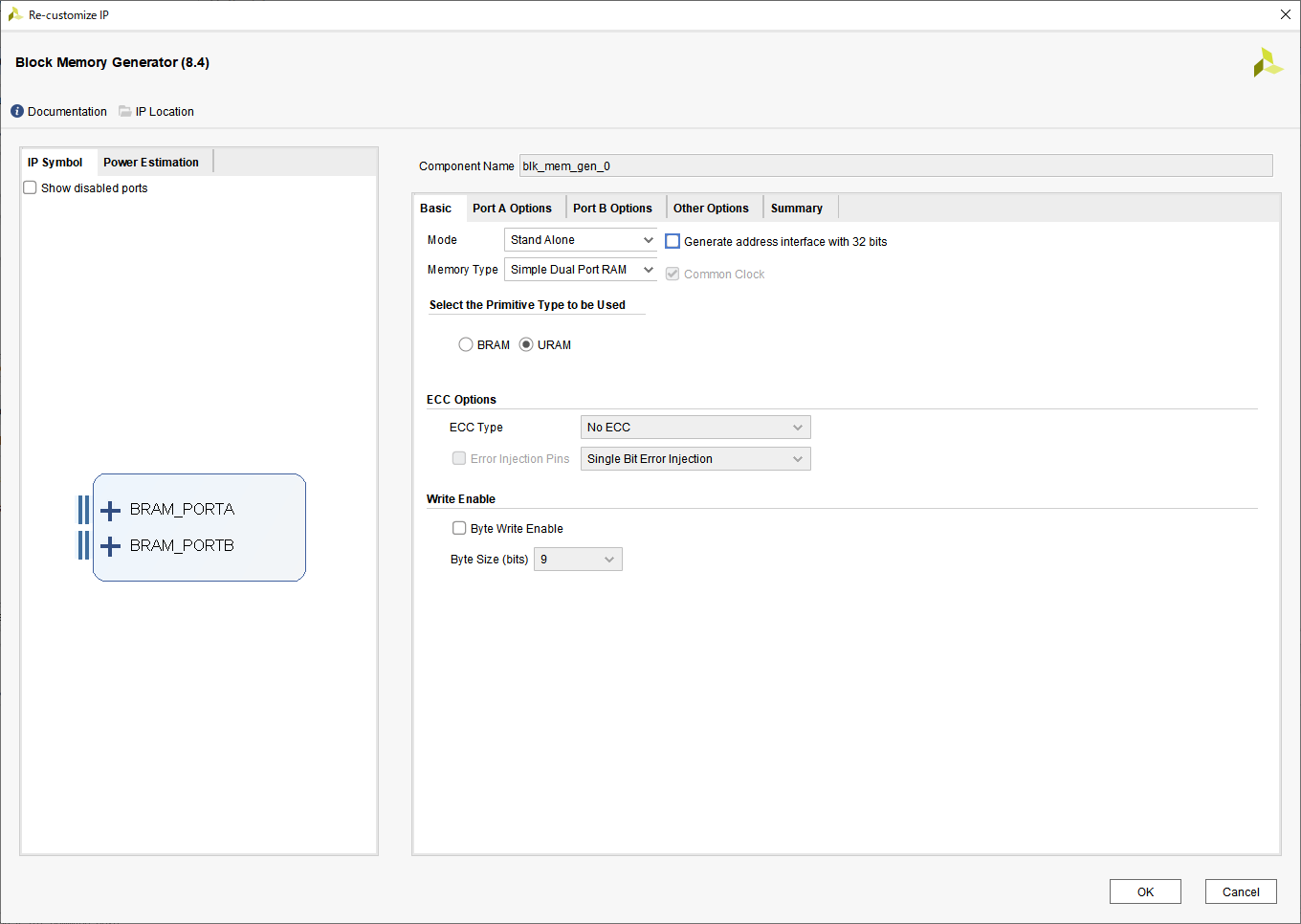

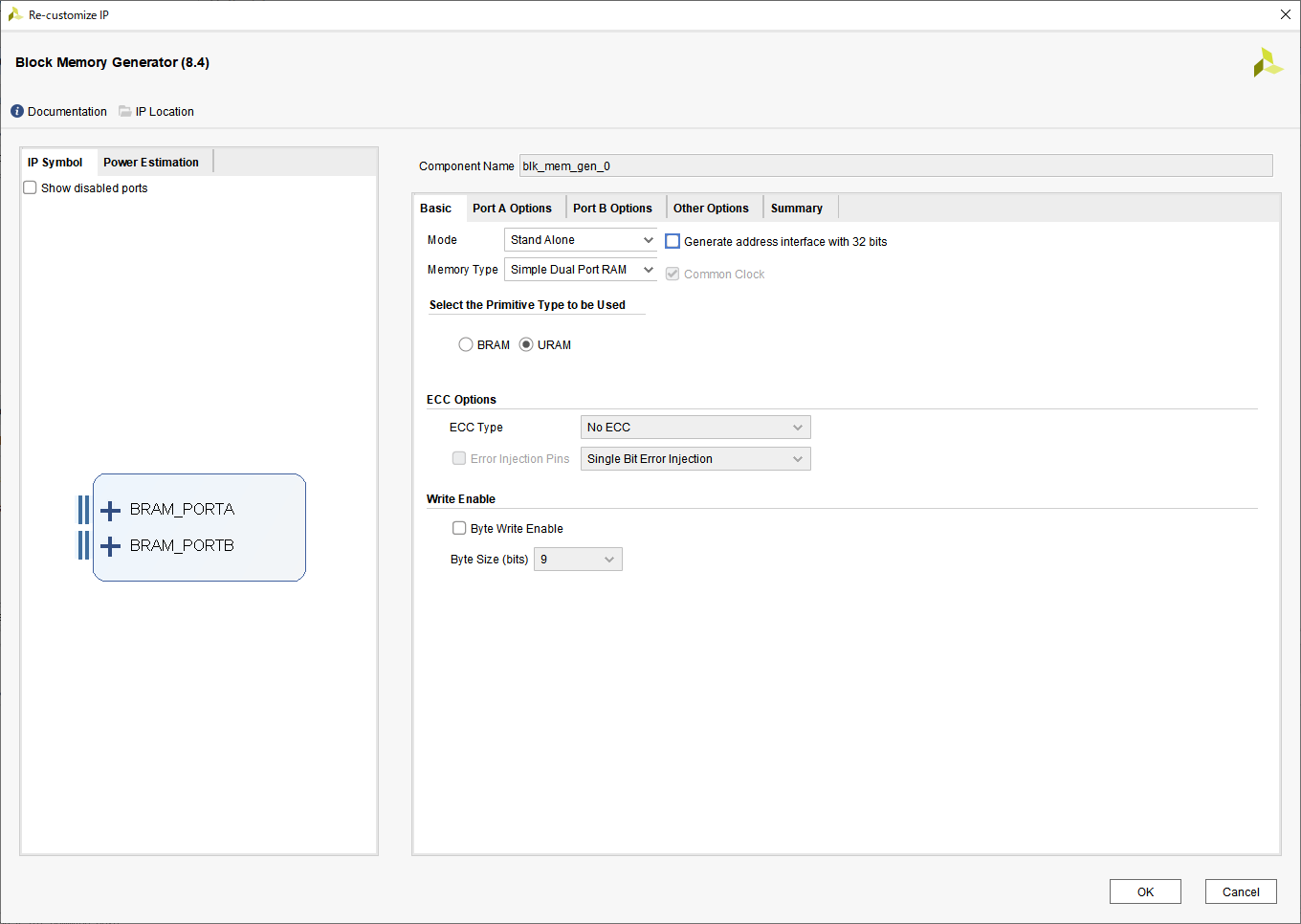

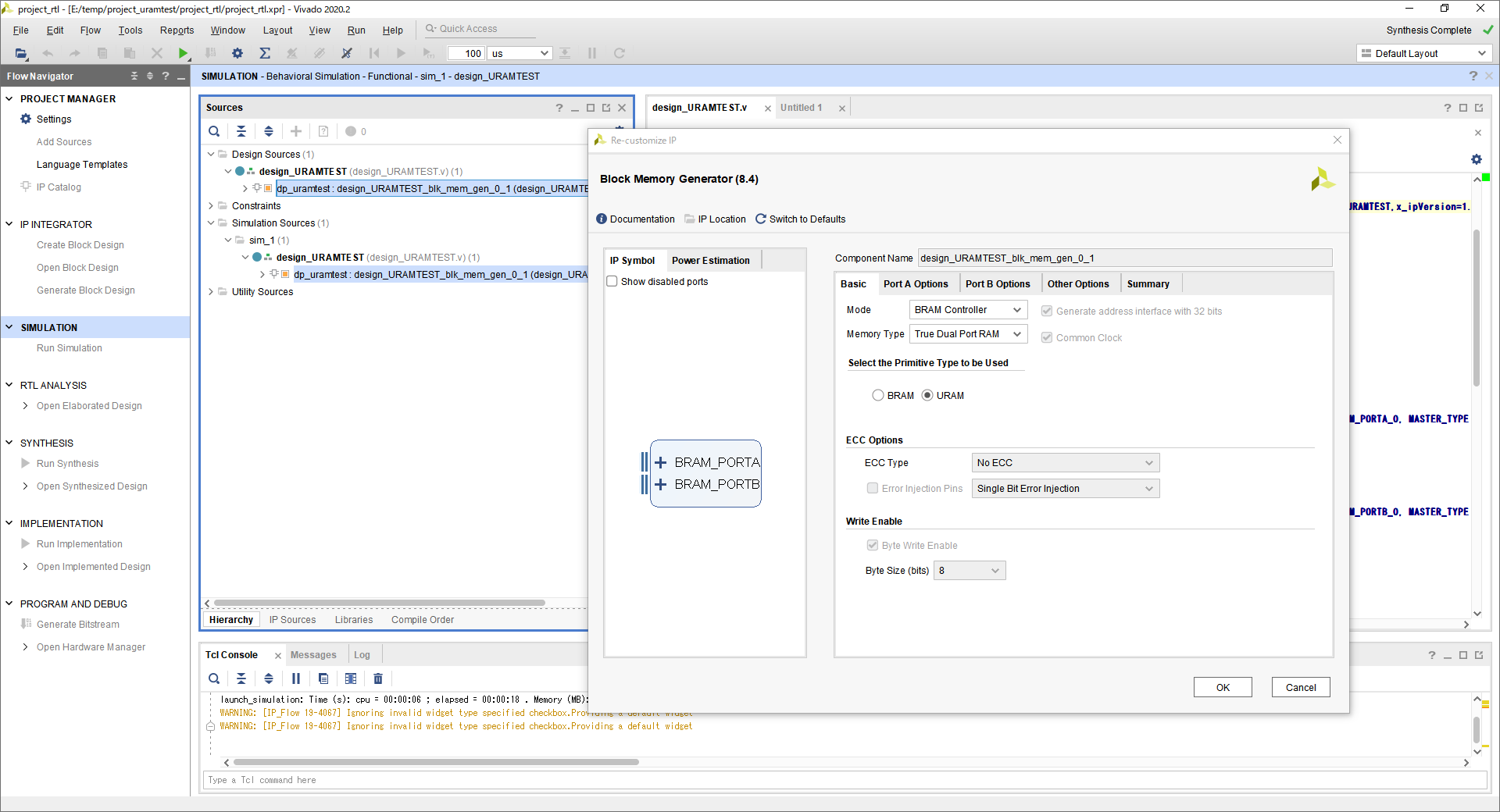

IPインテグレーター(BLOCK DESIGN)の使用のPROJECTでは下図のようにURAMの選択ができます。

出典:Vivado™ ML Edition

方法

IPインテグレーターを使用したBLOCKのBlock Memory Generatorで必要なモジュールを生成し、RTL PROJECTに読み込みする方法もあるので、以下に具体的なやり方を紹介いたします。

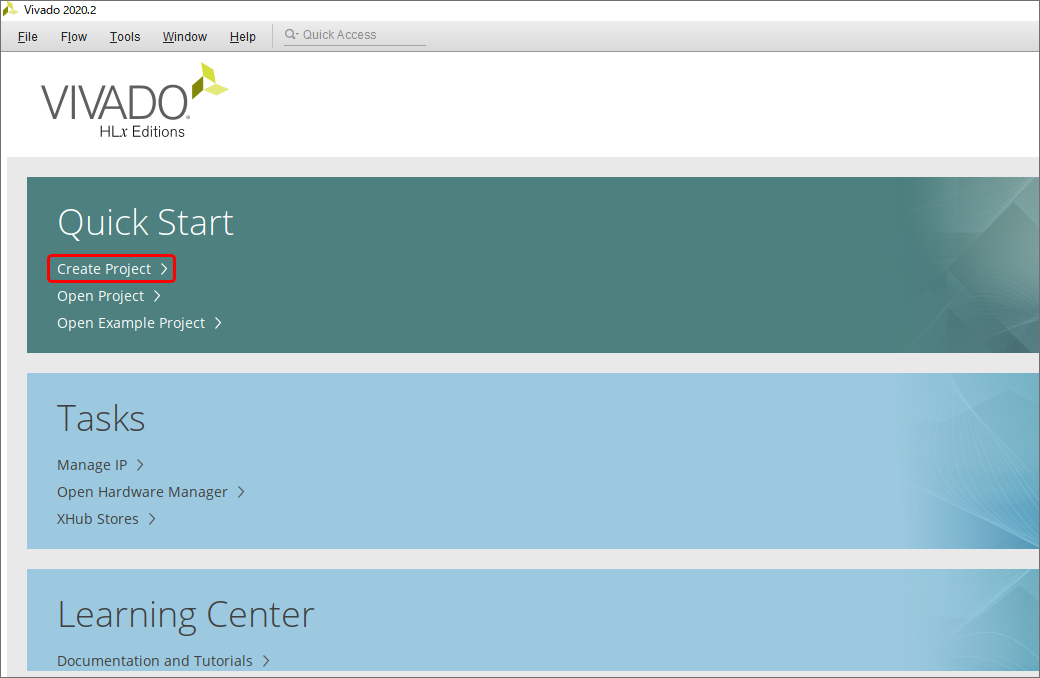

1. 生成用PROJECTを新規作成

出典:Vivado™ ML Edition

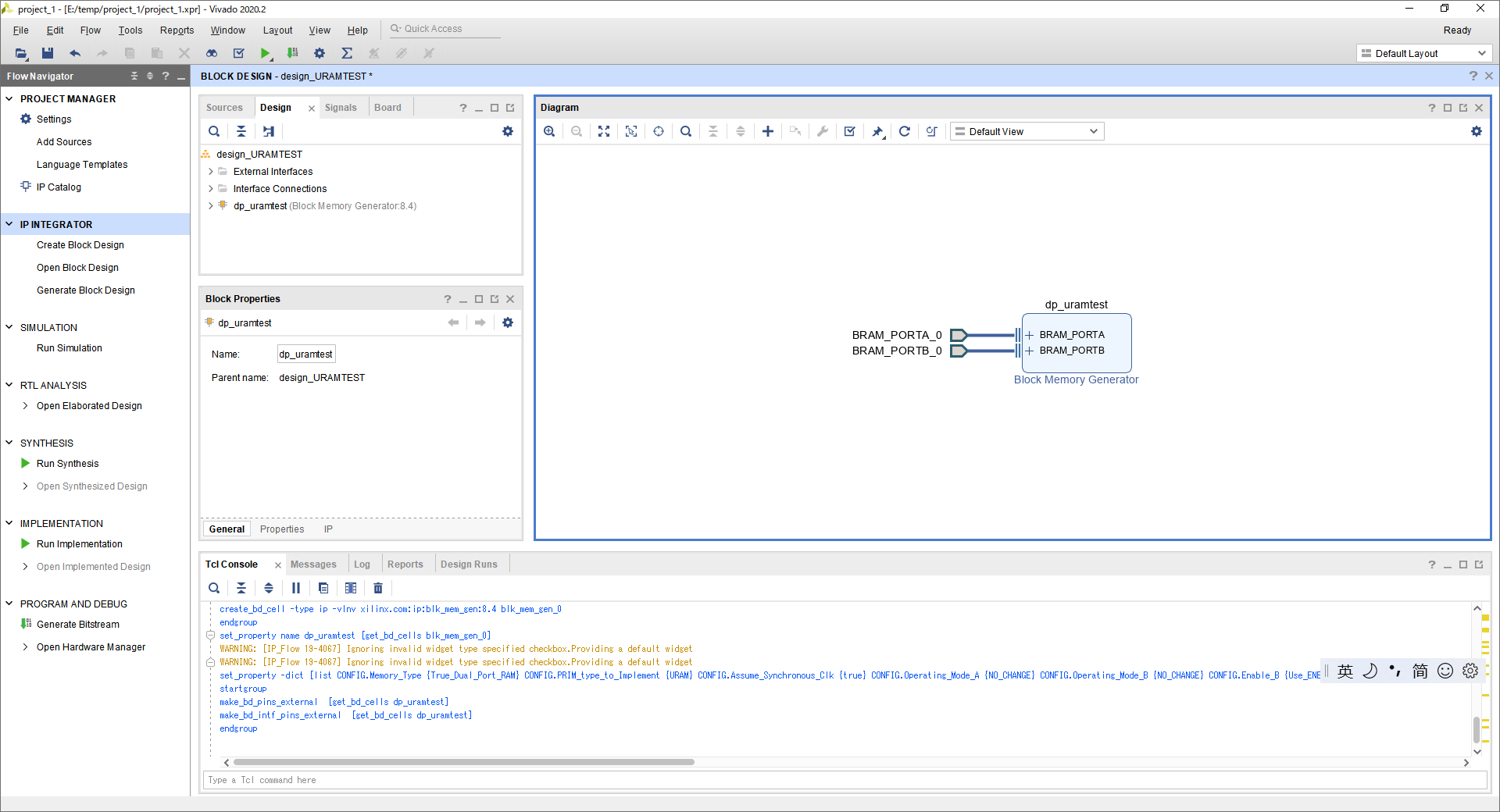

2. 新規BLOCKデザインを作成

出典:Vivado™ ML Edition

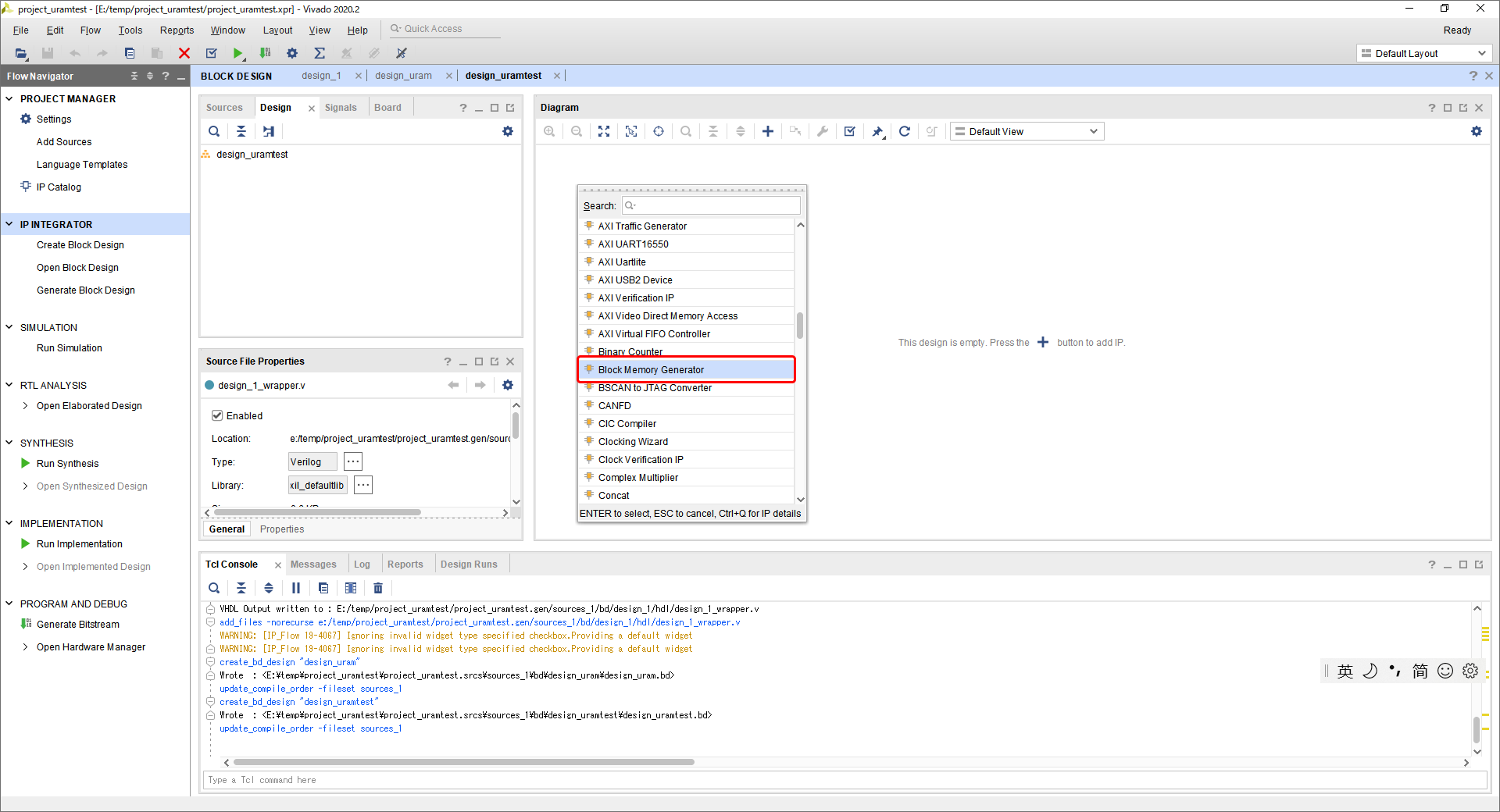

3. IPを追加

+を押して、Block Memory GeneratorでIPを追加します。

出典:Vivado™ ML Edition

出典:Vivado™ ML Edition

4. IP設定

IP、IP名を必要に応じて設定します。

IP

出典:Vivado™ ML Edition

IP名

出典:Vivado™ ML Edition

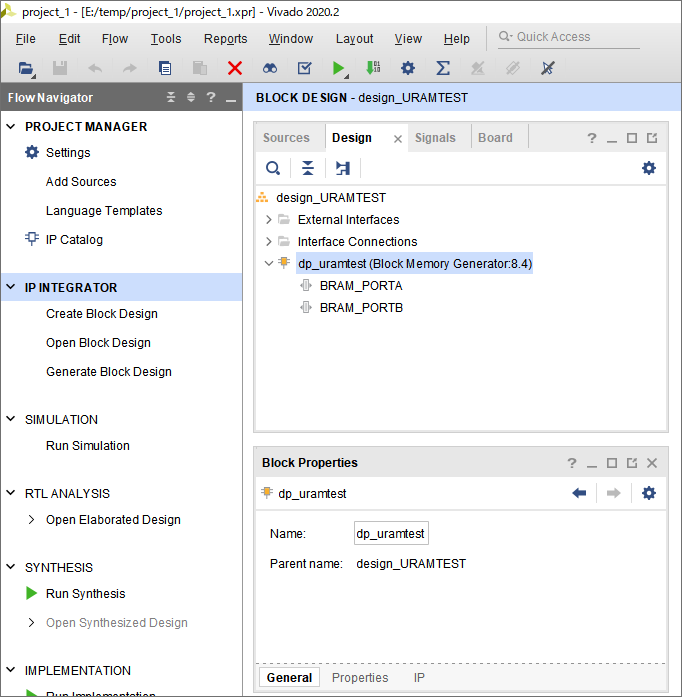

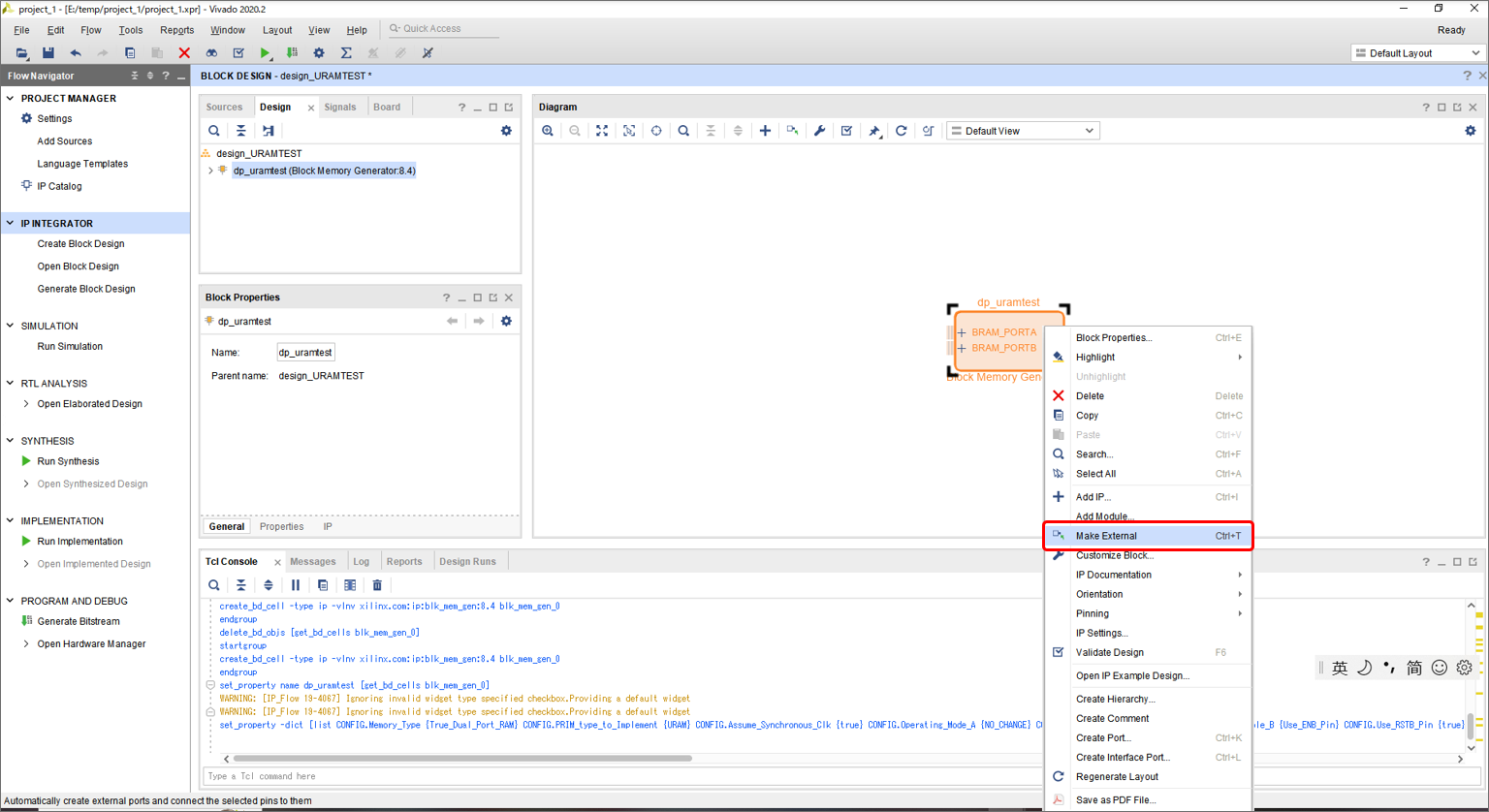

5. 外部PORTを生成

IPを選択し、右クリックからMake Externalで外部PORTを生成します。

出典:Vivado™ ML Edition

出典:Vivado™ ML Edition

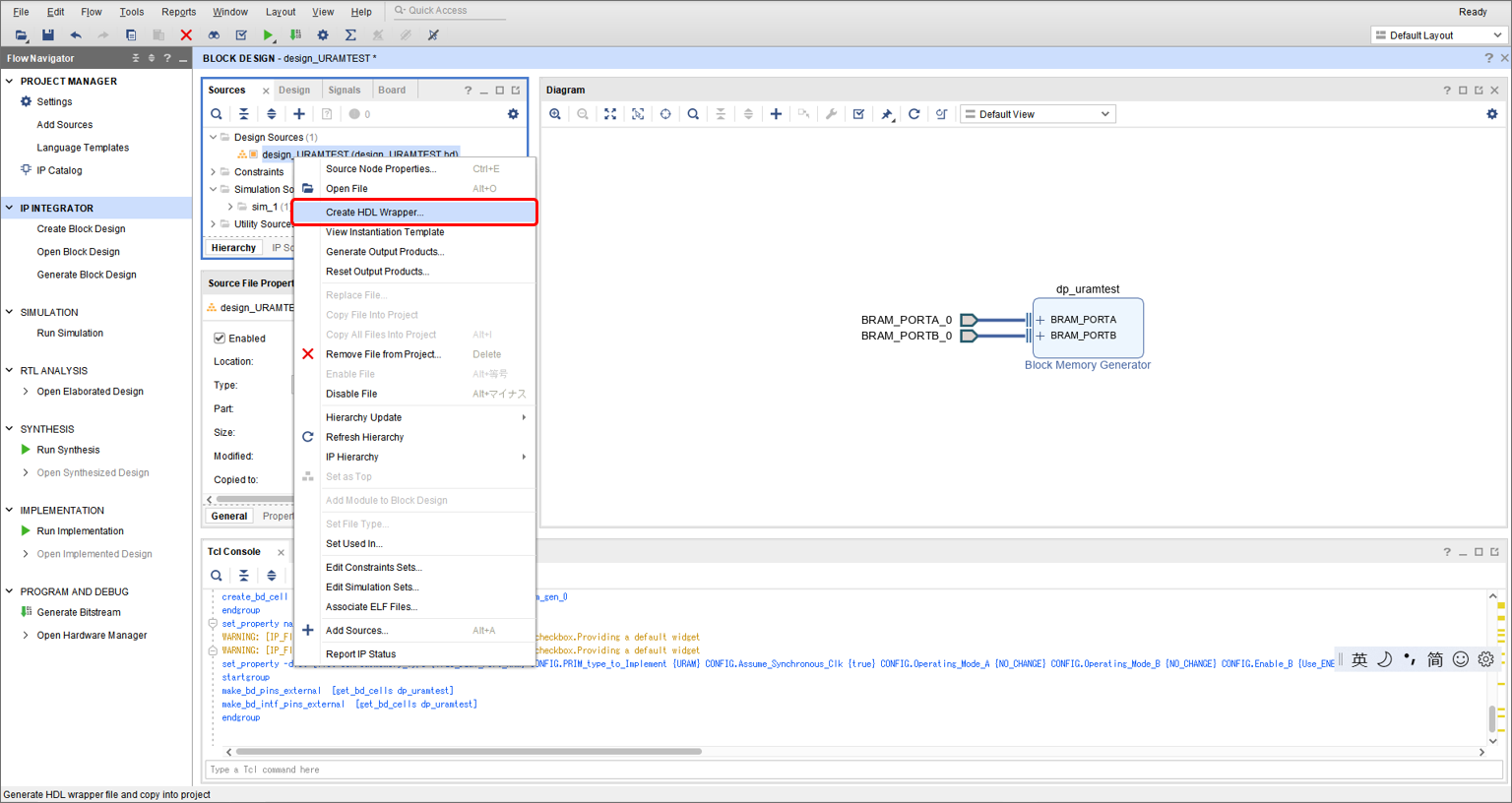

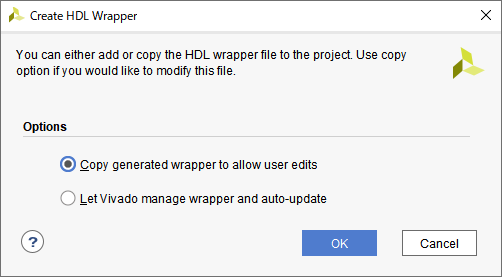

6. RTLを生成

Create HDL WrapperでRTL PROJECTインポートに必要なRTLを生成します。

出典:Vivado™ ML Edition

出典:Vivado™ ML Edition

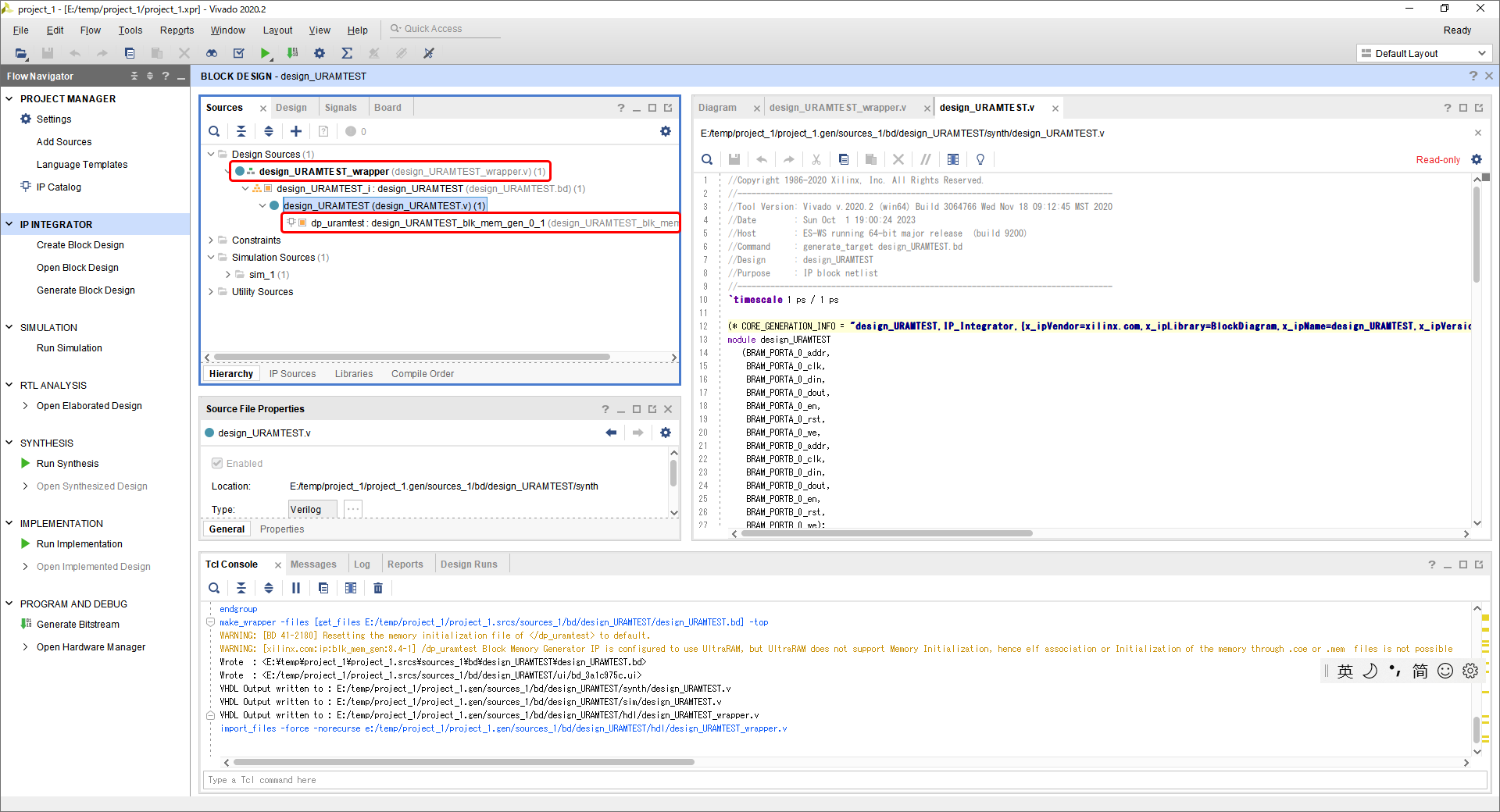

以下のようにRTL WrapperとIPのTOPファイルが生成されます。

出典:Vivado™ ML Edition

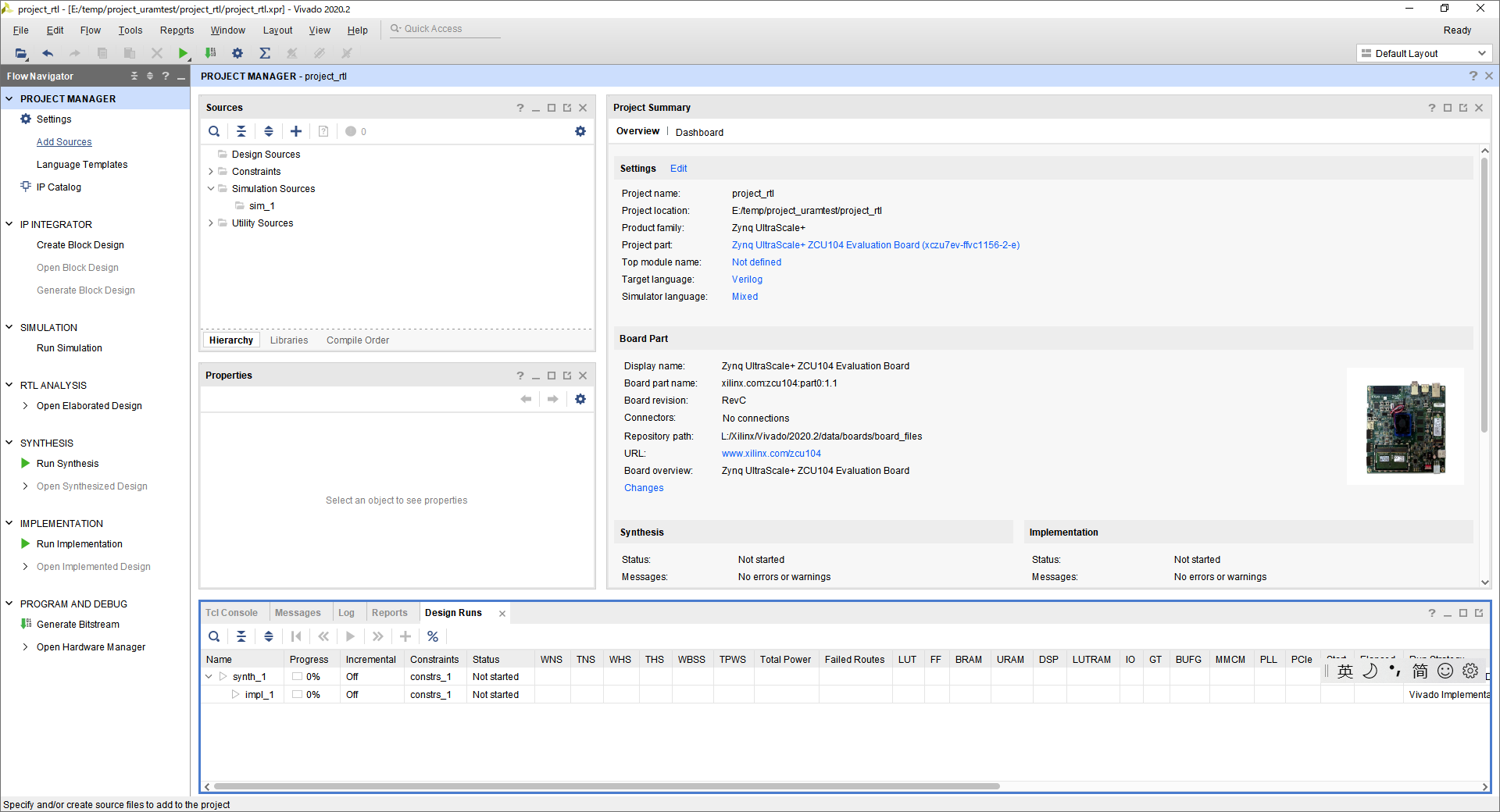

7. RTL PROJECTにインポート

生成されたIPをRTL PROJECTにインポートします。RTL PROJECTを開き、もしくは新規RTL PROJECTを作成します。

出典:Vivado™ ML Edition

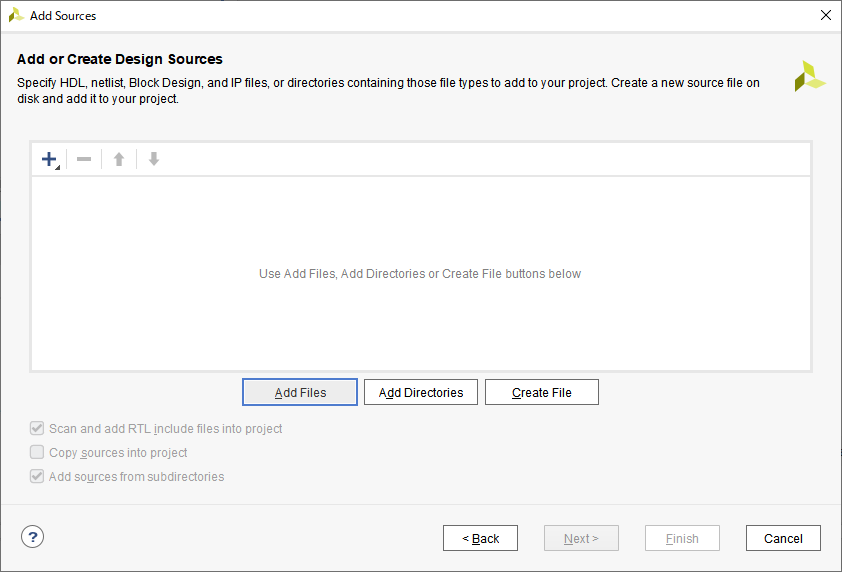

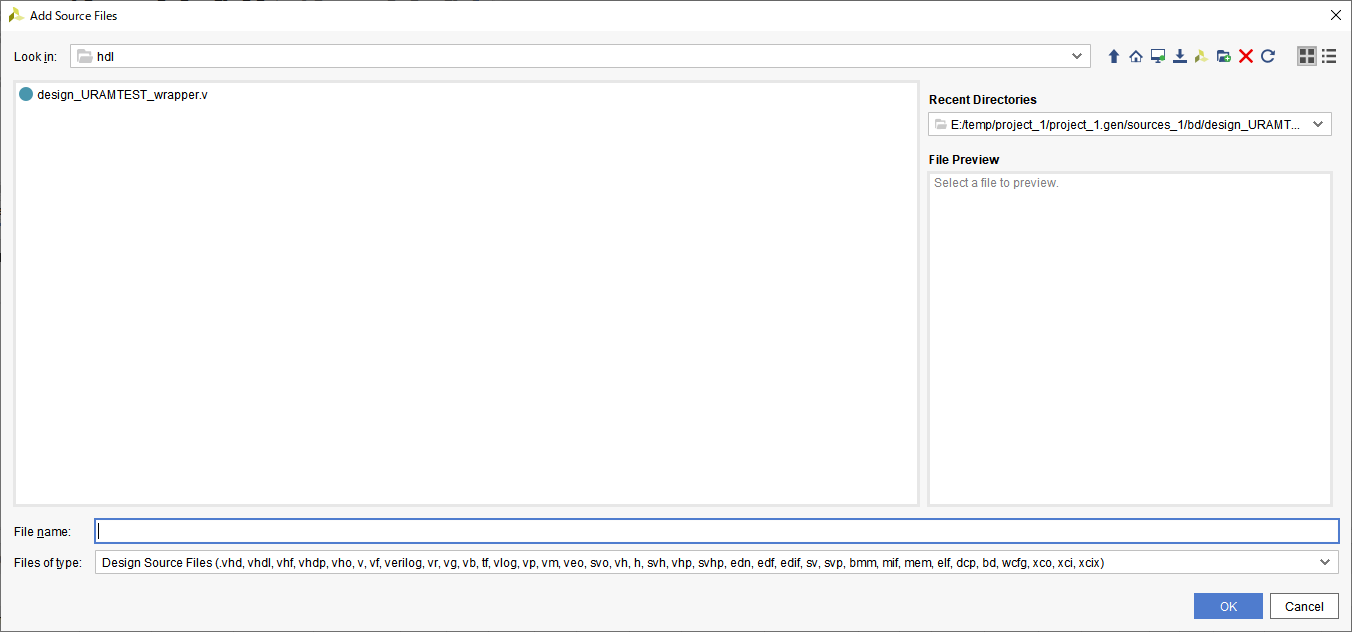

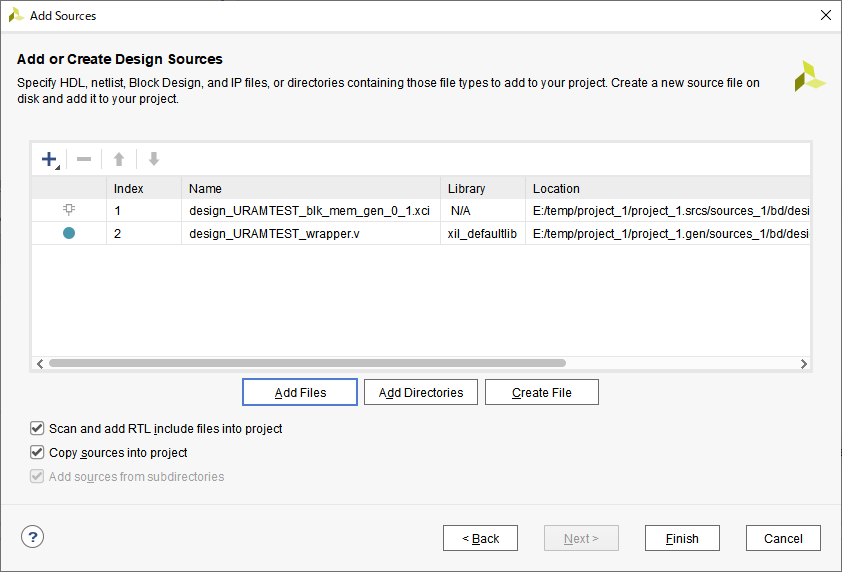

8. ファイルインポート

add source→add or create design sourceを選択し、必要なファイルをインポートします。

出典:Vivado™ ML Edition

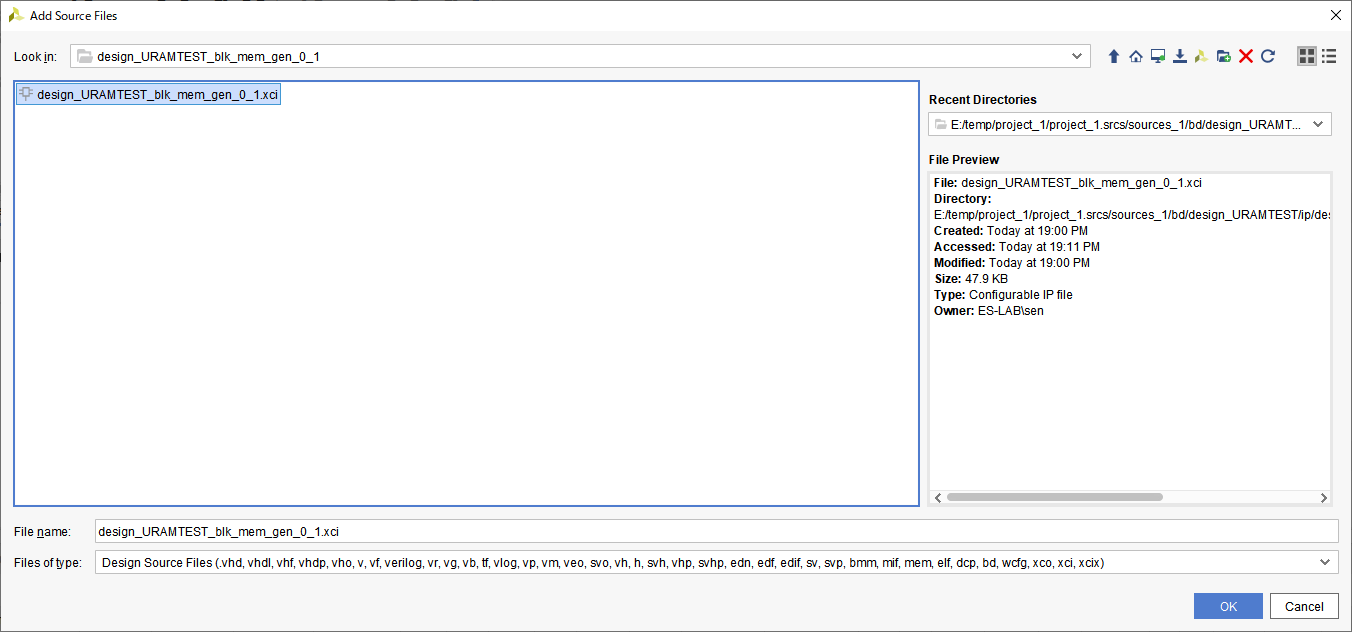

\project_1.srcs\sources_1\bd\design_URAMTEST\ip\design_URAMTEST_blk_mem_gen_0_1\design_URAMTEST_blk_mem_gen_0_1.xciを追加します。

出典:Vivado™ ML Edition

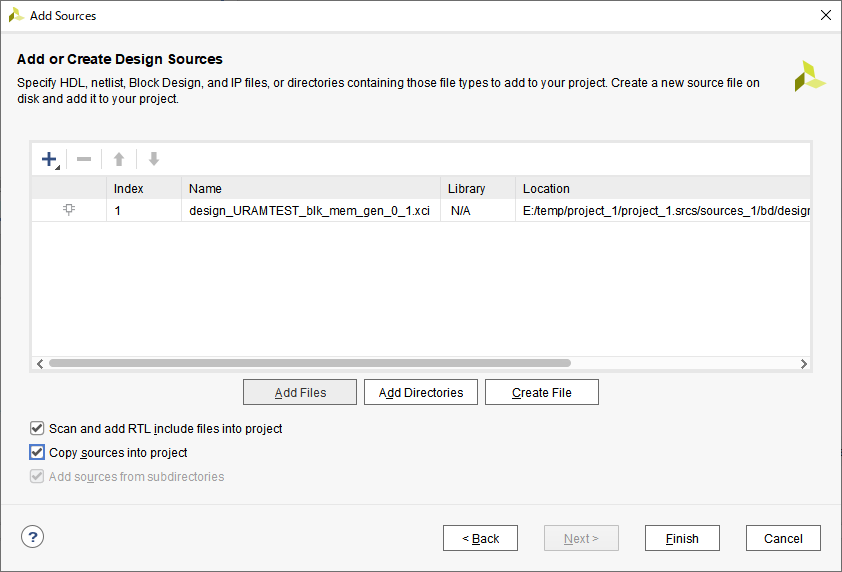

出典:Vivado™ ML Edition

\project_1.gen\sources_1\bd\design_URAMTEST\synth\design_URAMTEST.vを追加します。

出典:Vivado™ ML Edition

scan and add RTL include files into projectとcopy source into projectを選択し、finishをクリックします。

出典:Vivado™ ML Edition

出典:Vivado™ ML Edition

おわりに

いかがでしたでしょうか。

以上でRTL PROJECTにURAMが有効になっているIPが追加されました。

次回は複数URAMを使用した時に動作周波数を改善する方法を紹介したいと思います。

弊社ではFPGA設計や回路図設計、レイアウト設計、ソフトウェア設計、筐体設計などを受託開発しています。サービス内容をWEBサイトに掲載していますので、ぜひご覧ください。

FPGAの活用に際して設計検討などありましたら、お気軽にお問い合わせください。

最後までお付き合いいただきありがとうございました。

このブログは「FPGA設計ブログ一覧」の

1. コーディング・IP設定・プリミティブ設定 のひとつです。