Vivado® Design Suite でIEEE-1735によるソースコード暗号化

FPGAや適応型SoCでの開発においてソースコードを公開したくない場合…

そのようなときのために、Xilinx社Vivado® Design SuiteではIEEE-1735という暗号化の方法がサポートされています。

この方法を使用すれば、ソースコードを暗号化し、非公開に設定することができます。こちらは、Vivado® Design Suite上で設定しますが、Vivado® Design Suite上でしか解読することができないので、ソースコードの情報を守ることができます。

今回はXilinx社のVivado® Design SuiteでIEEE-1735によるソースコード暗号化の手順についてお伝えします。

このブログは「FPGA設計ブログ一覧」の

3. 論理合成(ツールが言語を回路図化する)の

ひとつです。

目次

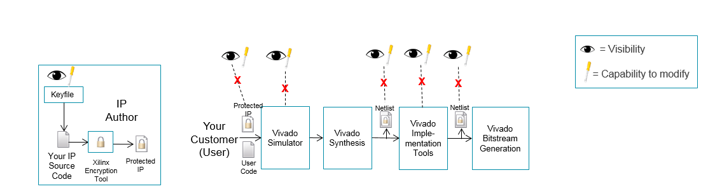

IP Encryption

Xilinx社のVivado® Design SuiteはIEEE-1735-2014バージョン2ベースの暗号化をサポートしています。IP Encryptionでは、HDL (SystemVerilog、Verilog、VHDL) デザイン入力からビットストリーム生成まで対応します。IP作成者は、ツールによるIPの管理方法を定義することで、自分のIPのアクセス権を管理できます。

出典 : https://japan.xilinx.com/products/intellectual-property/ip-encryption.html

各種キー(ライセンス管理)

- バージョン2の暗号化は、Vivado® Design Suite 2016.3以降のバージョンでサポートされています。

Vivado® Design Suite 2017.2.1または、それ以降のバージョンのご使用をおすすめします。 - 現在、VHDL、Verilog、SystemVerilogをサポートしています。

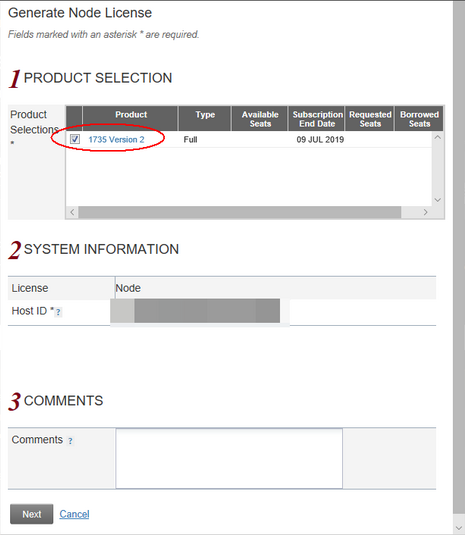

- 暗号化機能にはライセンスが必要です。(無料)

- 復号化にライセンスは不要です。

- 暗号化されたIPのライセンス

- シミュレーション専用キー

このキーでは、論理シミュレーションのみを実行できます。ISE® Design Suiteソフトウェアには、ほとんどの有償LogiCORE™ IPコアのシミュレーション専用キーが含まれています。

ハードウェア評価用キー

このキーでは、デザインのシミュレーションと実装、タイミング解析の実行、および時間制限付きビットストリームを生成してザイリンクスFPGAや適応型SoCをプログラム可能です。デバイスにプログラムされたコアは、2〜8時間 (コアによって異なる) ハードウェア上で機能します。プロセッサIPコアのハードウェア評価用キーは、ISE® Design Suite Embedded Editionソフトウェアに含まれています。

量産用キー

フルライセンスキーでは、シミュレーション、インプリメンテーション、タイミング解析、およびザイリンクスFPGAをプログラムして制限時間のないハードウェア検証が可能なためIPコアを量産品に使用できます。

暗号化の手順

Vivado® Design SuiteでIEEE-1735によるソースコード(vhdl)暗号化手順

STEP 1 : 1735のライセンス申請

STEP 2 : keyfile作成

- `protect version = 2

`protect encrypt_agent = "XILINX"

`protect encrypt_agent_info = "Xilinx Encryption Tool 2017"

`protect begin_commonblock

`protect control error_handling = "delegated"

`protect control runtime_visibility = "delegated"

`protect control child_visibility = "delegated"

`protect control decryption=(activity==simulation) ? "false" : "true"

`protect end_commonblock

`protect begin_toolblock

`protect rights_digest_method="sha256"

`protect key_keyowner = "Xilinx", key_keyname= "xilinxt_2017_05", key_method = "rsa", key_public_key

MIIBIjANBgkqhkiG9w0BAQEFAAOCAQ8AMIIBCgKCAQEAxngMPQrDv/s/Rz/ED4Ri j3tGzeObw/Topab4sl+WDRl/up6SWpAfcgdqb2jvLontfkiQS2xnGoq/Ye0JJEp2 h0NYydCB5GtcEBEe+2n5YJxgiHJ5fGaPguuM6pMX2GcBfKpp3dg8hA/KVTGwvX6a L4ThrFgEyCSRe2zVd4DpayOre1LZlFVO8X207BNIJD29reTGSFzj5fbVsHSyRpPl kmOpFQiXMjqOtYFAwI9LyVEJpfx2B6GxwA+5zrGC/ZptmaTTj1a3Z815q1GUZu1A dpBK2uY9B4wXer6M8yKeqGX0uxDAOW1zh7tvzBysCJoWkZD39OJJWaoaddvhq6HU MwIDAQAB

`protect control xilinx_configuration_visible = "false"

`protect control xilinx_enable_modification = "false"

`protect control xilinx_enable_probing = "false"

`protect control xilinx_enable_netlist_export = "false"

`protect control xilinx_enable_bitstream = "true"

`protect control decryption=(xilinx_activity==simulation) ? "false" : "true"

`protect end_toolblock = ""

STEP 3 : 暗号化(TCL実行)

- Vivado® tcl console:

encrypt -key keyfile.txt -ext .vhdp -lang vhd SAP_MAIN.vhd

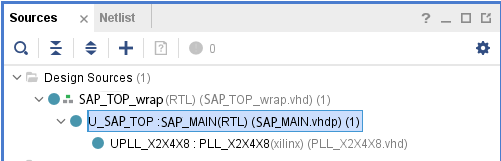

STEP 4 : wrap file作成(OPTION)

- library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

library unisim;

use unisim.vcomponents.all;

entity SAP_TOP_wrap is

port(

ARST_SAP_X : in std_logic;

CLK_DRV_SAP_P : in std_logic;

CLK_DRV_SAP_N : in std_logic;

CCDID_B2D : in std_logic_vector(4 downto 0);

PLL_LOCKED_B2D : in std_logic;

ABSEL_DRV_F2D : in std_logic;

JTAG_SEL_B2D : in std_logic;

JTAG_TDO_B2D : in std_logic;

SCID2_F2D_TXD : in std_logic;

DSW_SAP : in std_logic;

CCD_CLK_LV_P : out std_logic;

CCD_CLK_LV_N : out std_logic;

FR_VD_LV_P : out std_logic;

FR_VD_LV_N : out std_logic;

CLK_CCD_D2F : out std_logic;

JTAG_APTDI_SCID2_TXD : out std_logic;

CLK_SCID_D2F : out std_logic;

IIC_SYSCLK : out std_logic;

ARST_IIC_X : out std_logic;

chipclk : out std_logic;

MON : out std_logic_vector(29 downto 0)

);

end SAP_TOP_wrap;

architecture RTL of SAP_TOP_wrap is

component SAP_MAIN

port (

ARST_SAP_X : in std_logic;

CLK_DRV_SAP_P : in std_logic;

CLK_DRV_SAP_N : in std_logic;

CCDID_B2D : in std_logic_vector(4 downto 0);

PLL_LOCKED_B2D : in std_logic;

ABSEL_DRV_F2D : in std_logic;

JTAG_SEL_B2D : in std_logic;

JTAG_TDO_B2D : in std_logic;

SCID2_F2D_TXD : in std_logic;

DSW_SAP : in std_logic;

CCD_CLK_LV_P : out std_logic;

CCD_CLK_LV_N : out std_logic;

FR_VD_LV_P : out std_logic;

FR_VD_LV_N : out std_logic;

CLK_CCD_D2F : out std_logic;

JTAG_APTDI_SCID2_TXD : out std_logic;

CLK_SCID_D2F : out std_logic;

IIC_SYSCLK : out std_logic;

ARST_IIC_X : out std_logic;

chipclk : out std_logic;

MON : out std_logic_vector(29 downto 0)

);

end component;

begin

U_SAP_TOP : SAP_MAIN

port map (

ARST_SAP_X => ARST_SAP_X ,

CLK_DRV_SAP_P => CLK_DRV_SAP_P ,

CLK_DRV_SAP_N => CLK_DRV_SAP_N ,

CCDID_B2D => CCDID_B2D ,

PLL_LOCKED_B2D => PLL_LOCKED_B2D ,

ABSEL_DRV_F2D => ABSEL_DRV_F2D ,

JTAG_SEL_B2D => JTAG_SEL_B2D ,

JTAG_TDO_B2D => JTAG_TDO_B2D ,

SCID2_F2D_TXD => SCID2_F2D_TXD ,

DSW_SAP => DSW_SAP ,

CCD_CLK_LV_P => CCD_CLK_LV_P ,

CCD_CLK_LV_N => CCD_CLK_LV_N ,

FR_VD_LV_P => FR_VD_LV_P ,

FR_VD_LV_N => FR_VD_LV_N ,

CLK_CCD_D2F => CLK_CCD_D2F ,

JTAG_APTDI_SCID2_TXD => JTAG_APTDI_SCID2_TXD,

CLK_SCID_D2F => CLK_SCID_D2F ,

IIC_SYSCLK => IIC_SYSCLK ,

ARST_IIC_X => ARST_IIC_X ,

chipclk => chipclk ,

MON => MON

);

end RTL ;

STEP 5 : wrapファイルとvhdpファイルを一緒に読み込む

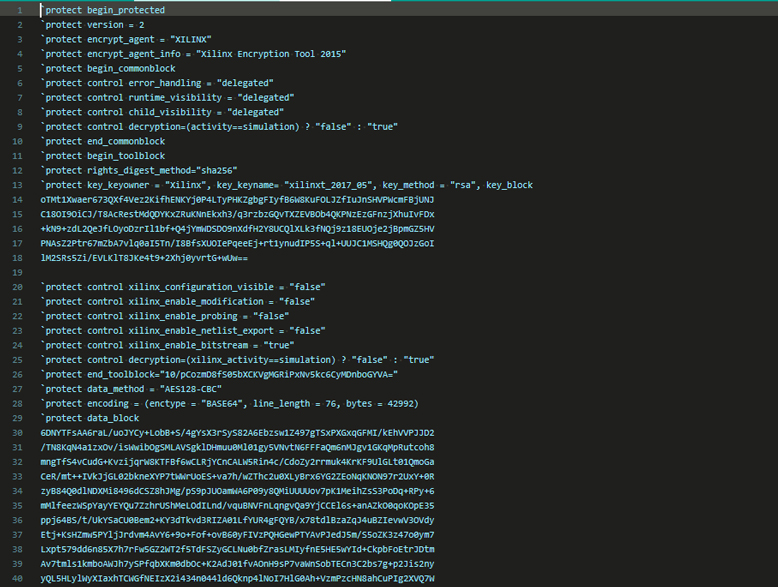

参考:.vhdpファイルの中身

手順まとめ

- STEP1:1735のライセンス申請

- STEP2:keyfile作成

- STEP3:暗号化(TCL実行)

- STEP4:wrap file作成(OPTION)

- STEP5:Vivado® Design Suite wrapファイルとvhdpファイルを一緒に読み込む

いかがでしたでしょうか?

これで公開したくないRTLを暗号化できるようになります。

最後までお付き合いいただきありがとうございました。

このブログは「FPGA設計ブログ一覧」の

3. 論理合成(ツールが言語を回路図化する)の

ひとつです。