【Vivado®使用方法】Vivado®IPの参考デザインの出力方法

皆さん、こんにちは。

FPGAが持っている機能を使いたい場合や、AMD社が提供している特定の処理ロジックを使いたい場合、IP Catalogから選択、パラメータを設定し、自分のデザインに組み込むと思います。

単純なものであれば何も考えずに使用すると思いますが、難しいものであれば事前に使い方の把握や各信号の動作確認などを行いたいですよね。

そこで今回は、

- 設計を初めたばかりの方

- 昔Xilinx ISE®は使用したことはあるけどVivado®は不慣れという方

に向けて、IPの参考(example)デザインの出力方法をお届けしたいと思います。

今回は次の環境をベースにお話しいたします。

- Vivado®:ML Edition 2022.2.2

- FPGA:Artix™ UltraScale+™

それでは、はじめましょう。

目次

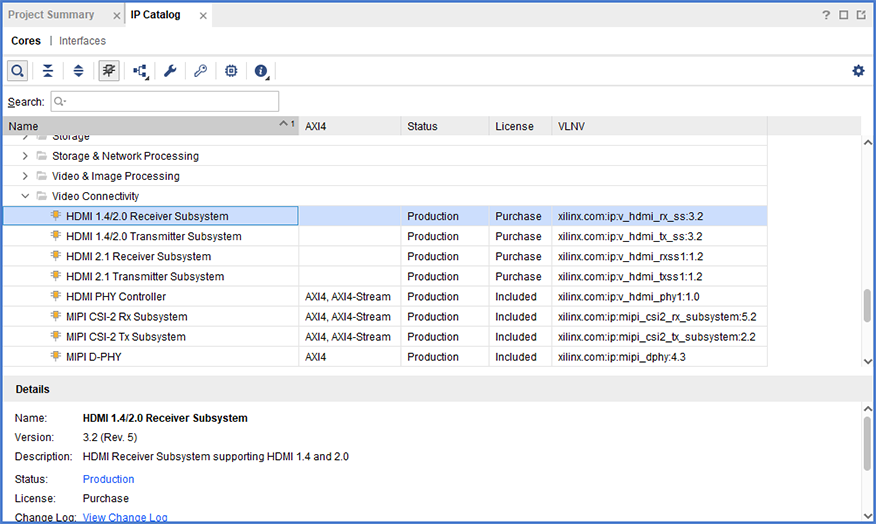

IPを追加

まずは1つ、次のIPを追加してみます。

- IP:HDMI 1.4/2.0 Receiver Subsystem v3.2

- Component Name:v_hdmi_rx_ss_0

出典:Vivado® 2020.2.2 IP Catalog画面 (参照 2023/06/29)

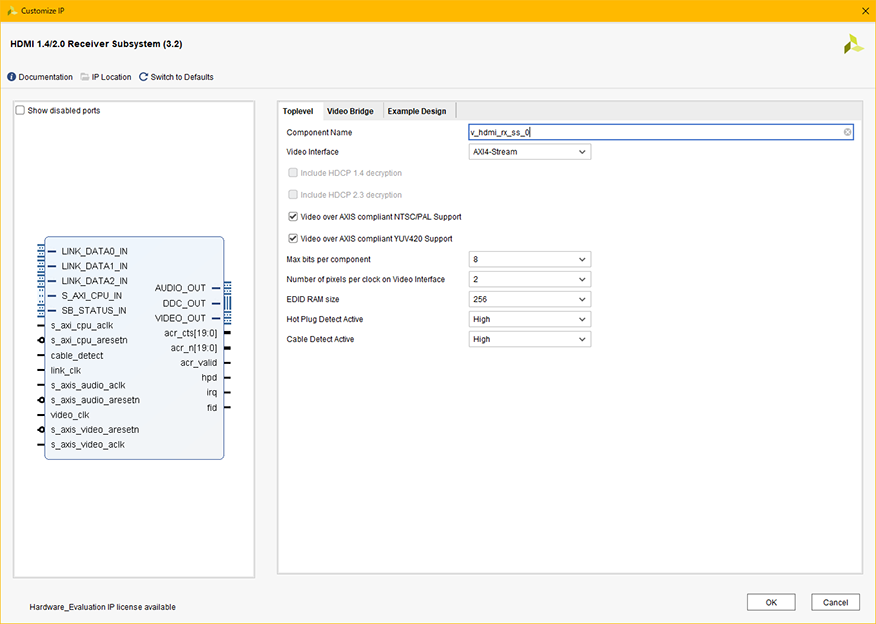

パラメータはデフォルトのままとします。

出典:Vivado® 2020.2.2 Customize IP画面 (参照 2023/06/29)

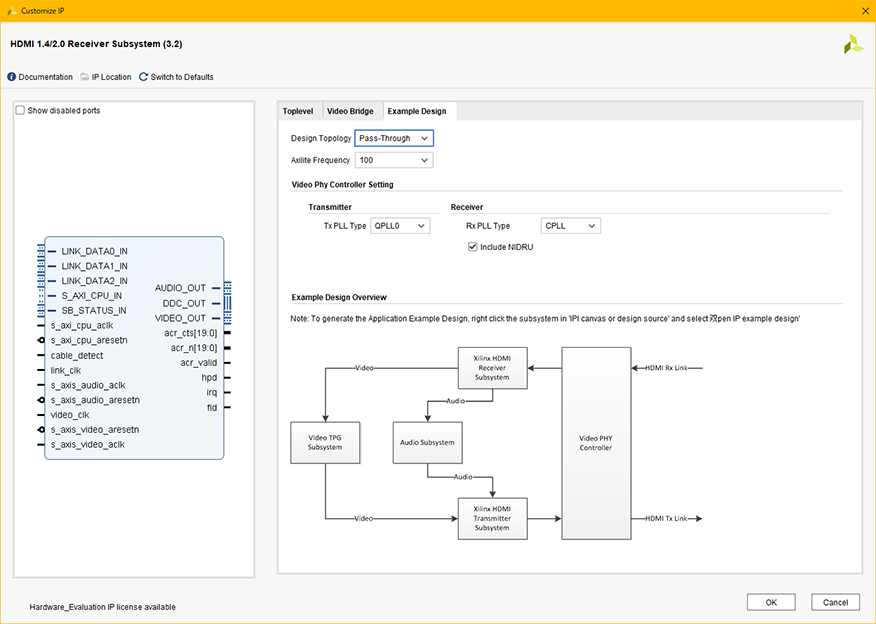

IPの中には「Example Design」のタブがあり、参考デザインの内容などを選べる場合があります。

今回は「Pass-Through」を選択します。

出典:Vivado® 2020.2.2 Customize IP画面 (参照 2023/06/29)

設定内容を確認しOKを押してGenerateを実行します。

参考デザインの出力

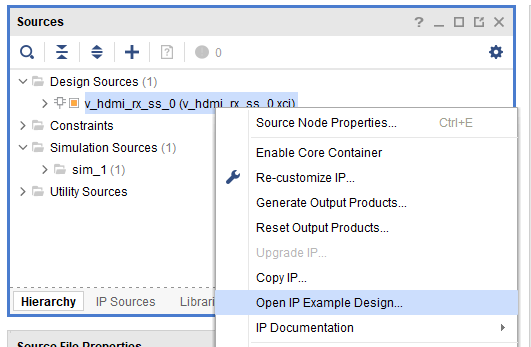

ISE®のときにはCORE Generator™でIPを生成すると一緒に参考デザインもできていましたが、Vivado®では別途作成しなければいけません。

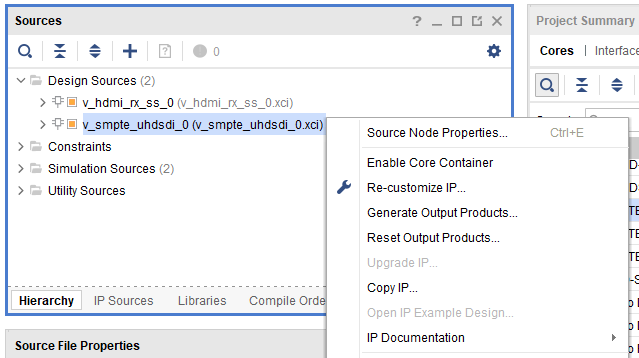

Sourceウィンドウの中から作成したIP「v_hdmi_rx_ss_0」を右クリックし、メニューの中から「Open IP Example Design」を実行します。

出典:Vivado® 2020.2.2 Sources画面 (参照 2023/06/29)

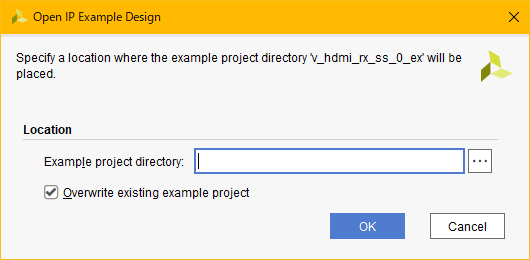

作成場所を聞かれますので、場所を指定してOKを押します。

出典:Vivado® 2020.2.2 Location設定画面 (参照 2023/06/29)

エラー発生について

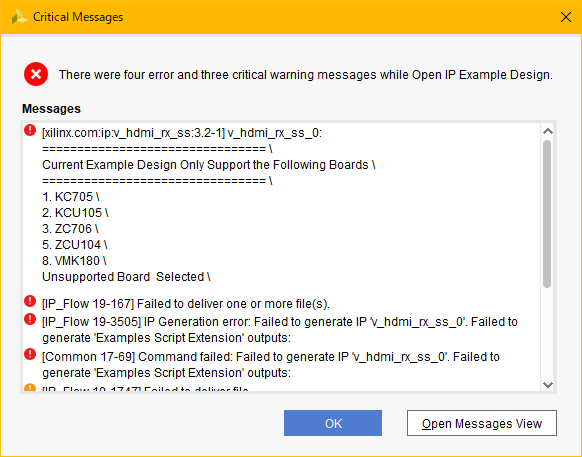

作成場所を指定してOKを押すと

出典:Vivado® 2020.2.2 Error Message画面 (参照 2023/06/29)

残念なことにエラーが出てしまい、参考デザインができませんでした。

Vivado®では参考デザインは評価基板で動作するものが生成されます。

つまり、IPが使用できるFPGAを選択していても、そのFPGAが搭載され、かつ実機用に参考デザインが用意されていない場合には生成できないのです。

今回、Artix™ UltraScale+™を選択していますが、実機用に参考デザインが用意されていないためこのエラーになりました。

参考デザインを出力するために

参考デザインを出力するためには、エラーメッセージにある評価ボードに搭載されているFPGA、または同じシリーズのFPGAをターゲットにして別途プロジェクトをつくる必要があります。

メッセージには次の5つの評価ボードが挙げられています。

- 1. KC705

- ← Kintex™ 7

- 2. KCU105

- ← Kintex™ UltraScale™

- 3. ZC706

- ← Zynq™ 7000

- 5. ZCU104

- ← Zynq™ UltraScale+™

- 8. VMK180

- ← Versal™

今回は選択しているArtix™ UltraScale+™に近い同じアーキテクチャでCPUが内蔵されていない「2.KCU105」の「Kintex™ UltraScale™」をターゲットにしたプロジェクトをつくります。

プロジェクト作成後、再度IPの作成・参考デザインの作成を行います。

評価ボードを使用したプロジェクト作成

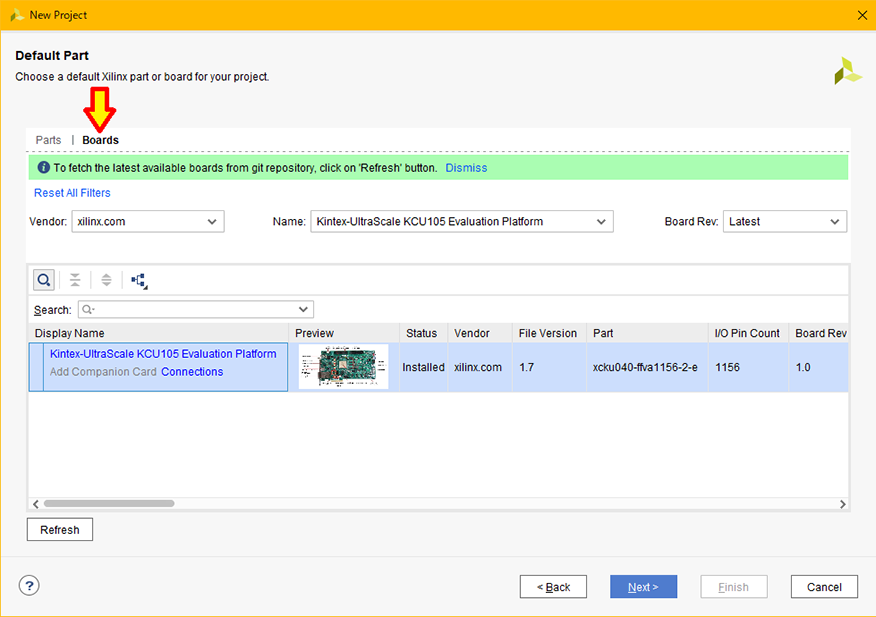

プロジェクトを作成する際に、「KCU105と同じFPGAにしたいけど搭載されているのはなんだろう?調べないと…」と思われた方、安心してください。

実は、パーツ選択ウィンドウの左上にある「Boards」を押すと、評価ボードの一覧が表示されます。

ここからKCU105を選ぶと搭載FPGAの詳細が分からなくてもプロジェクトがつくれるので非常に便利です。

出典:Vivado® 2020.2.2 プロジェクト 設定画面 (参照 2023/06/29)

参考デザインの出力

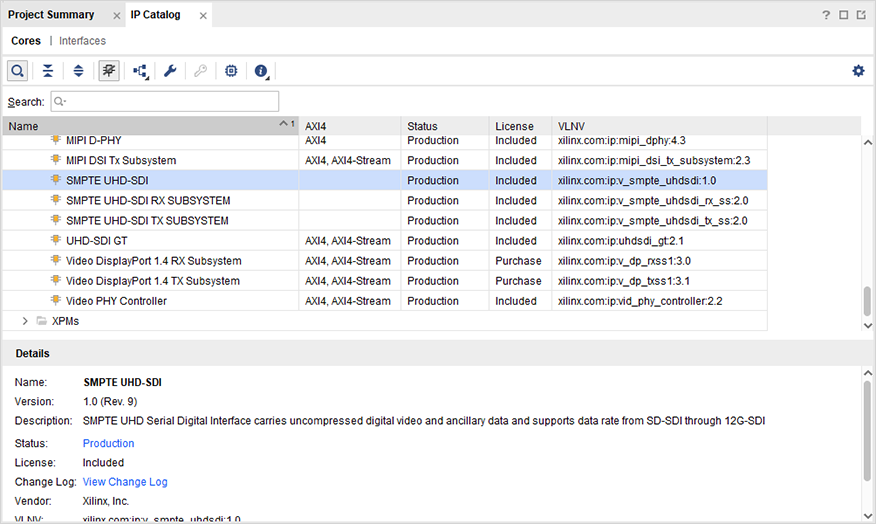

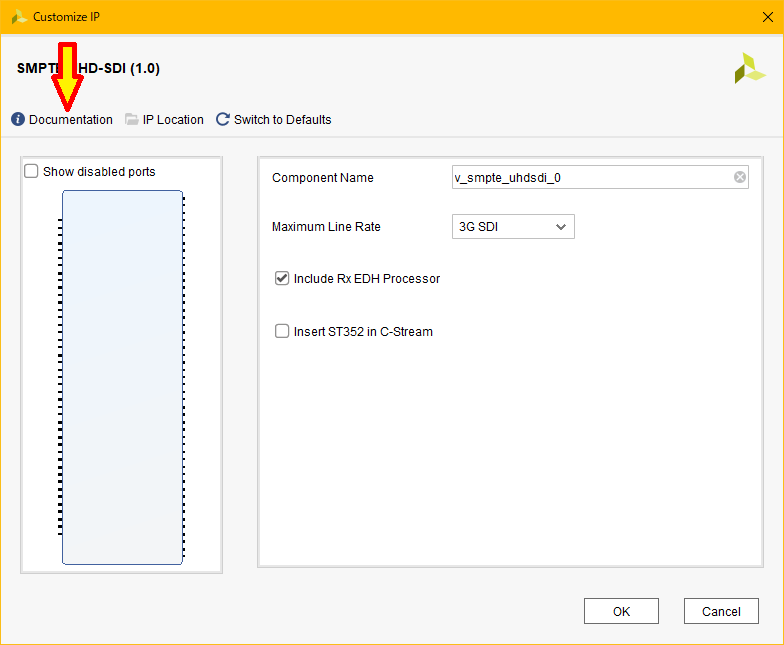

別のIPで参考デザインを出力してみましょう。それでは、もう1つIPを追加してみます。

- IP:SMPTE UHD-SDI v1.0

- Component Name:v_smpte_uhdsdi_0

出典:Vivado® 2020.2.2 IP Catalog画面 (参照 2023/06/29)

先ほどと同じようにsourceウィンドウの中から作成したIP「v_smpte_uhdsdi_0」を右クリックし、メニューの中から「Open IP Example Design」を実行…できませんでした。

出典:Vivado® 2020.2.2 Sources 画面 (参照 2023/06/29)

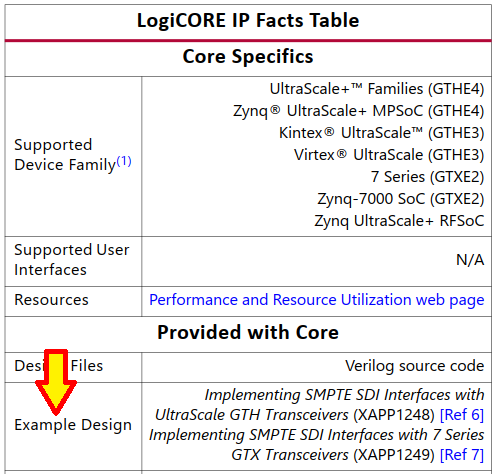

再度IP設定画面を開き、左上の「Documentation」を押し、Product Guide(PG205 September 28, 2020)を開いてIPの説明を見てみましょう。

出典:Vivado® 2020.2.2 Customize IP画面 (参照 2023/06/29)

すると、説明内に参考デザインは「XAPP1248またはXAPP1249」として用意されていると書かれていました。

※XAPPをダウンロードする際にはサイン・インが必要です。

出典: PG205 SMPTE UHD-SDI v1.0 Product Guide <P.4> (参照 2023/06/29)

このようにProduct Guideのどこかに説明が記載されている場合がありますので、IPをご使用される際には一読することをおすすめします。

おわりに

最後までご覧いただきましてありがとうございました!

これからもブログを通じて、皆様の設計にお役立てできればと思います。

次回のブログもどうぞよろしくお願いいたします。

弊社ではFPGA設計や回路図設計、レイアウト設計、ソフトウェア設計、筐体設計などを受託開発しています。

サービス内容をWEBサイトに掲載していますので、ぜひご覧ください。

FPGAの活用に際して設計検討などありましたら、お気軽にお問い合わせください。