AC701を用いた4CH_GTPサンプルデザインの作成と実機動作確認

皆さん、こんにちは。

本ブログでは、AMD社Artix-7の評価キットAC701 GTP Bank216用7 Series FPGAs Transceivers Wizardに合わせた設定方法や、サンプルデザインの修正方法、ONBOARD GTREFCLKの追加方法と実機の評価方法を紹介したいと思います。

- TOOL

- : Vivado™ Ver 2021.2

- DEVICE

- : AC701(Artix-7)

このブログは「FPGA設計ブログ一覧」の

6. 実機評価のひとつです。

目次

サンプルデザインの作成

1. AC701のPROJECT作成

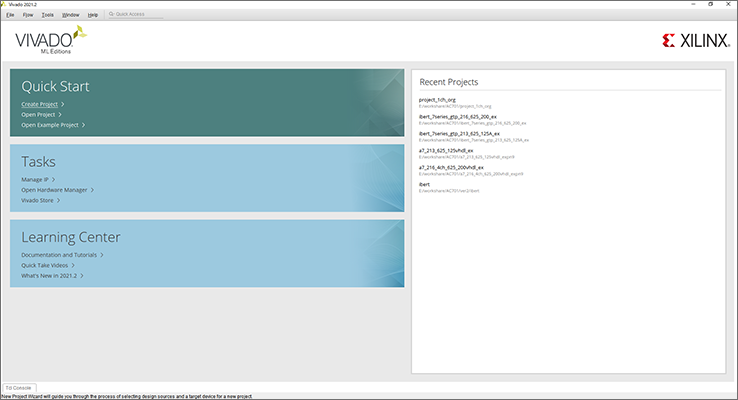

- 1-1.

- Vivado™を起動し、Create Projectをクリックします。

(出典:Vivado™ ML Edition)

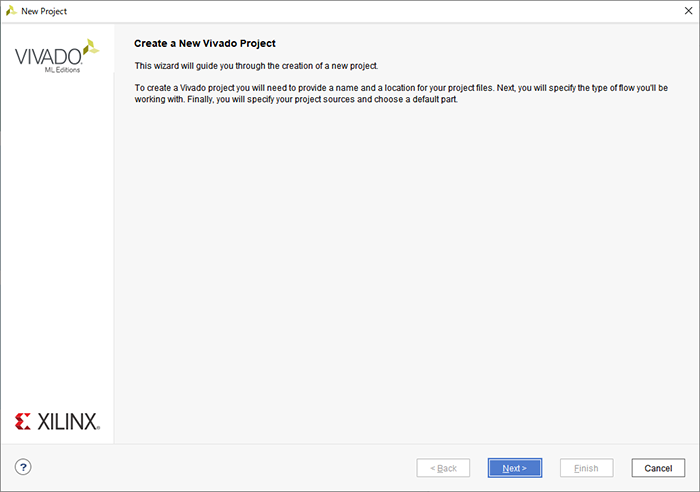

- 1-2.

- Nextをクリックします。

(出典:Vivado™ ML Edition)

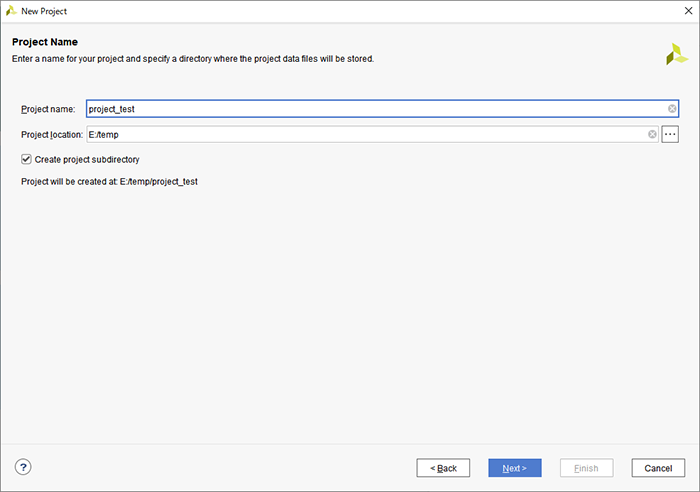

- 1-3.

- Project nameを入力し、Nextをクリックします。

(出典:Vivado™ ML Edition)

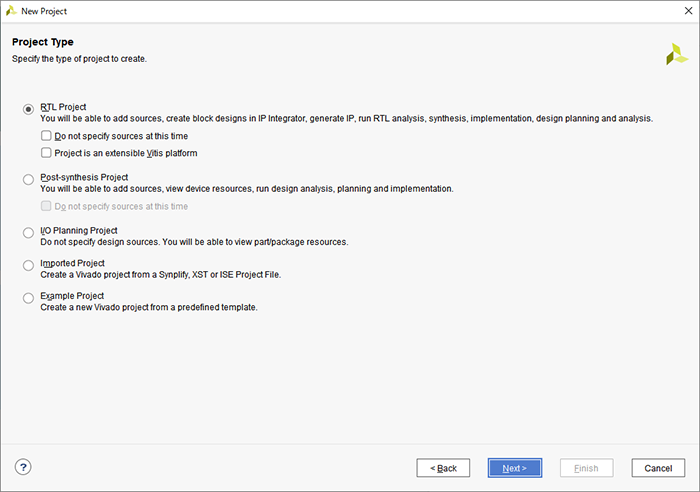

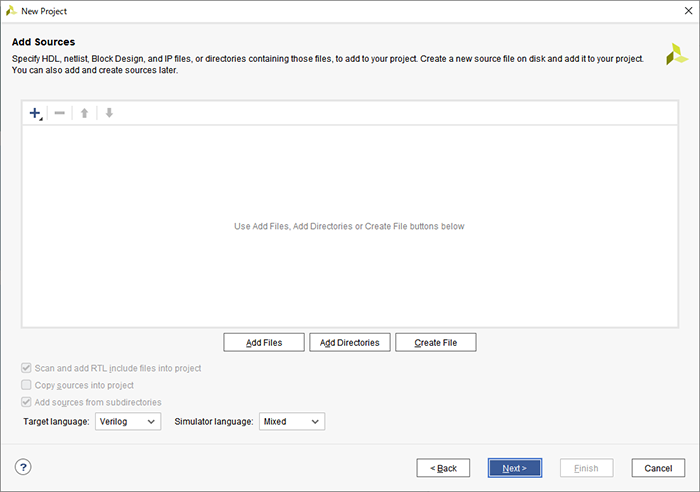

- 1-4.

- このまま、Nextをクリックします。

(出典:Vivado™ ML Edition)

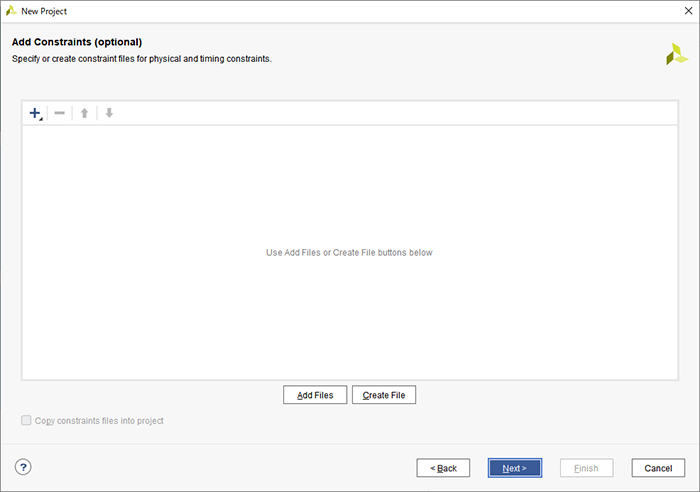

- 1-5.

- このまま、Nextをクリックします。

(出典:Vivado™ ML Edition)

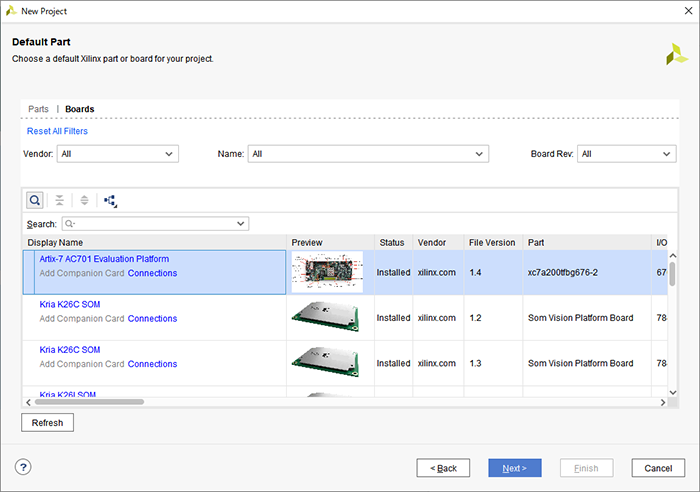

- 1-6.

- このまま、Nextをクリックします。

(出典:Vivado™ ML Edition)

- 1-7.

- Boardsをクリックし、AC701を選択し、Nextをクリックします。

(出典:Vivado™ ML Edition)

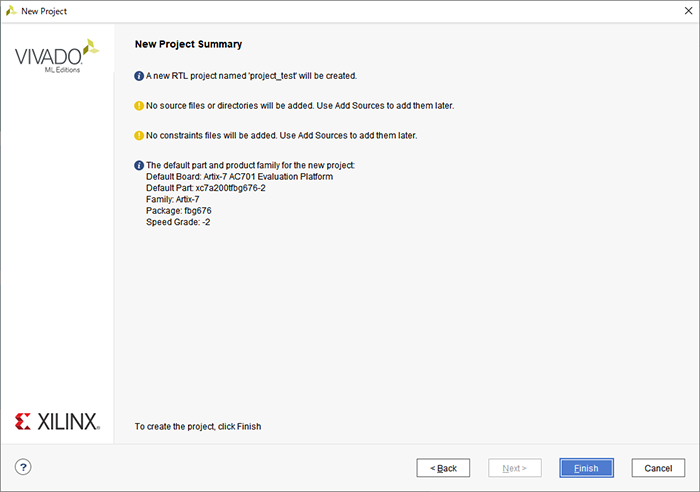

- 1-8.

- Finishをクリックします。

(出典:Vivado™ ML Edition)

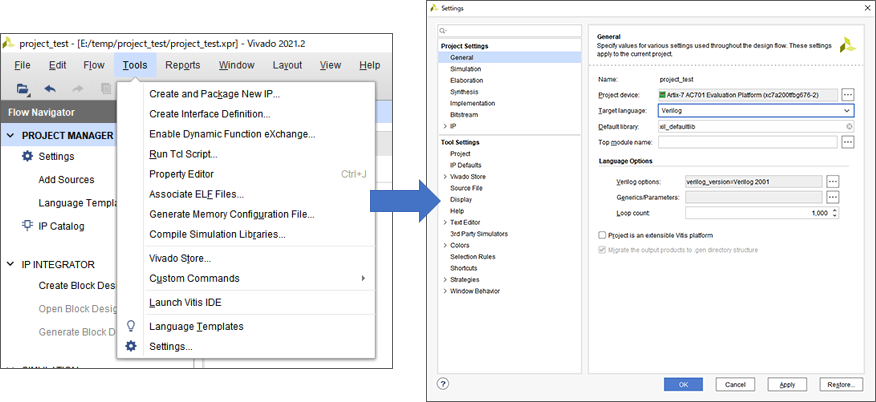

- 1-9.

- Tools→Settingsで必要に応じて言語の種類(VHDL、Verilog)を選択します。

(出典:Vivado™ ML Edition)

2. IPを生成(設定)

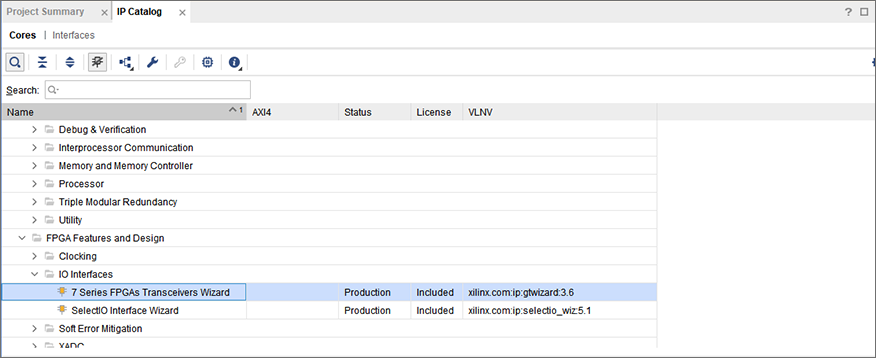

- 2-1.

- IP catalogから7 Series FPGAs Transceivers Wizardを開きます。

(出典:Vivado™ ML Edition)

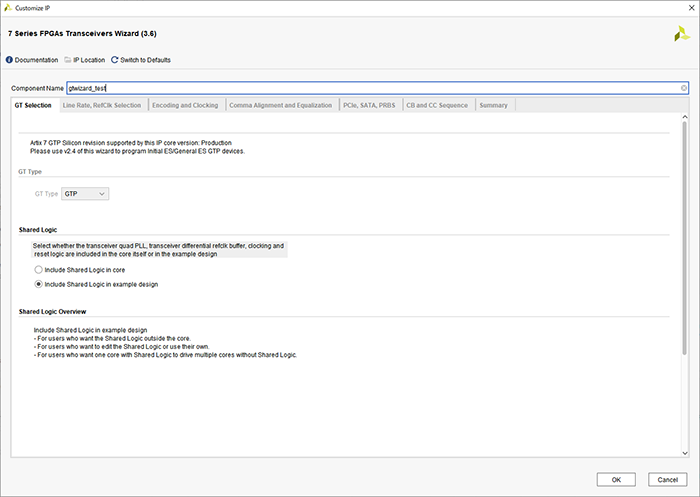

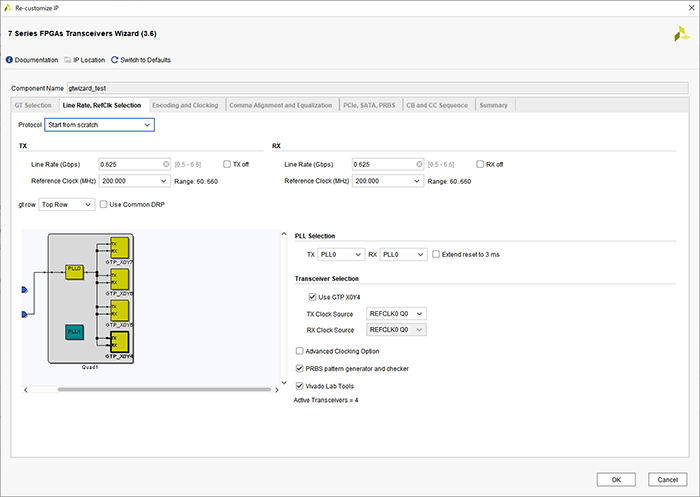

- 2-2.

- Component Nameを入力します、GT Selection sheetを以下のように設定します。

(出典:Vivado™ ML Edition)

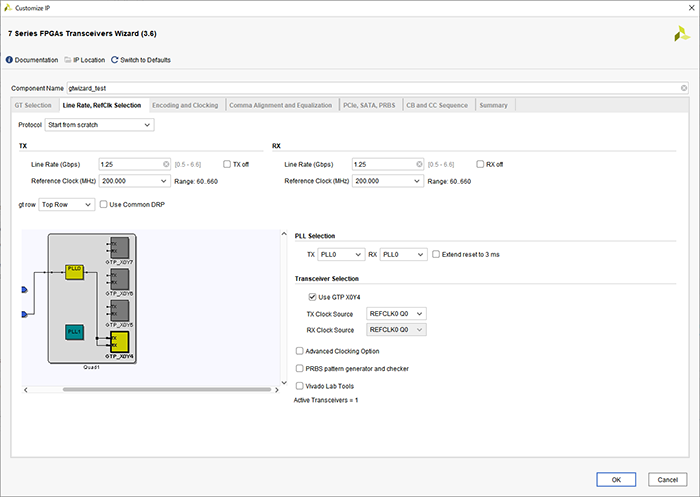

- 2-3.

- Line Rate, RefClk Selectionを以下のように設定します。

- まず、下図のようにGTP_X0Y4だけUSED状態でTX Clock sourceをREFCLK0 Q0に設定します。

次にReference Clockを200MHzと選択します。

(必要に応じて変更は可能ですが、その場合はREFCLKの周波数を合わせる必要があります)

(出典:Vivado™ ML Edition)

- 2-4.

- 上記2-3の設定をしてからGTP_X0Y5, GTP_X0Y6, GTP_X0Y7を使用するようにします。

PRBS pattern generator and checkerとVivado Lab Toolsを選択します。

- 2-3→2-4の順番で設定する必要があり、先にGTP_X0Y5, GTP_X0Y6, GTP_X0Y7をUseにすると、

REFCLKの変更ができなくなります。

(出典:Vivado™ ML Edition)

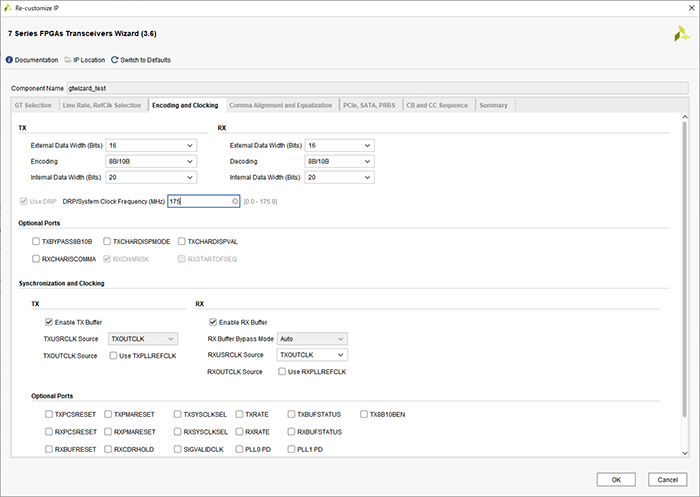

- 2-5.

- Encoding and Clockingを必要に応じて設定します。

DRP/System Clock Frequencyを175MHzに設定します。

- DRPを使用するときに、デザイン上にDRP CLKを生成することを推奨します。

(出典:Vivado™ ML Edition)

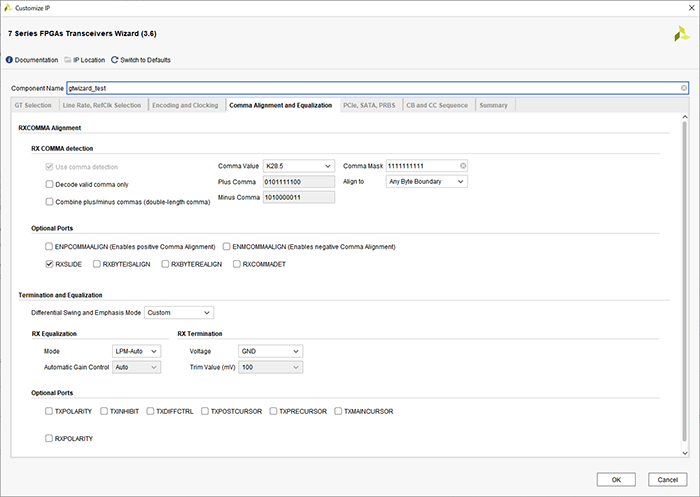

- 2-6.

- Comma Alignment and Equalizationを設定します。

- Defaultのままで構いません。

(出典:Vivado™ ML Edition)

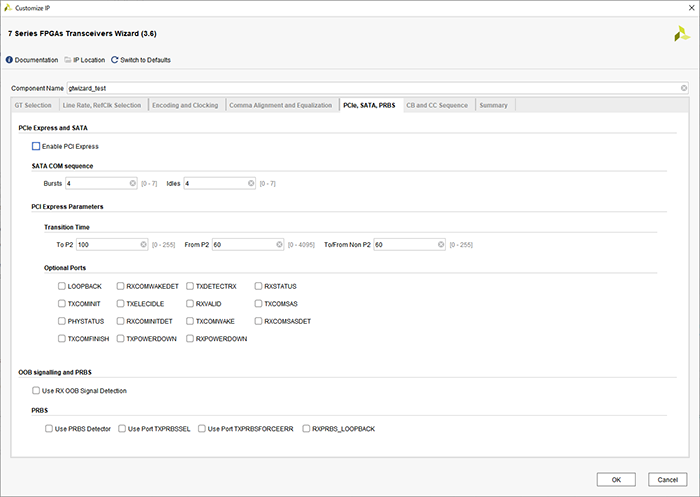

- 2-7.

- PCIEなど使わないので、Defaultのままにします。

(出典:Vivado™ ML Edition)

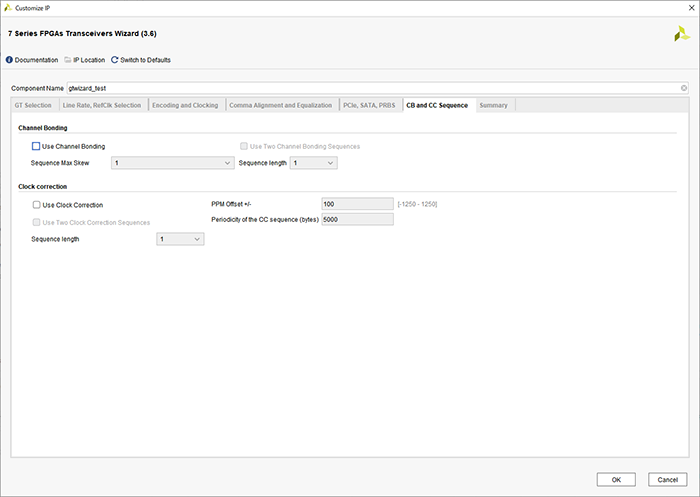

- 2-8.

- CB and CC Sequenceは、Defaultのままにします。

(出典:Vivado™ ML Edition)

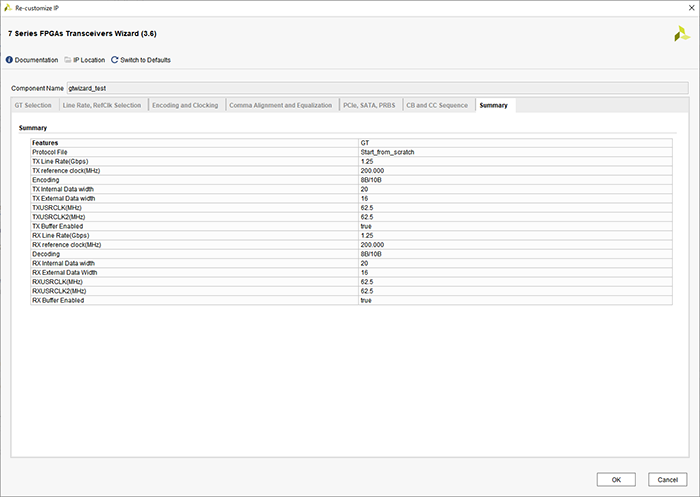

- 2-9.

- Summaryで確認します。

(出典:Vivado™ ML Edition)

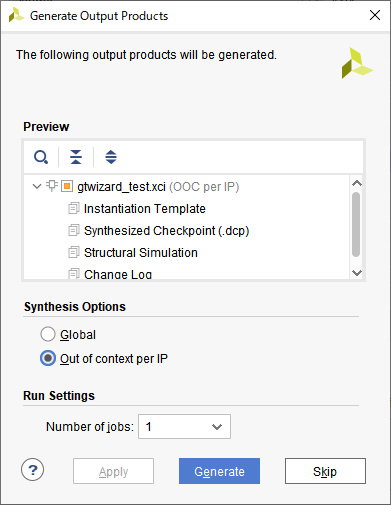

- 2-10.

- 設定完了後、OKをクリックします。

(出典:Vivado™ ML Edition)

- 2-11.

- Generateをクリックします。

- Vivado™の右上が以下のようになるので“Ready”となるまで待ちます。

(出典:Vivado™ ML Edition)

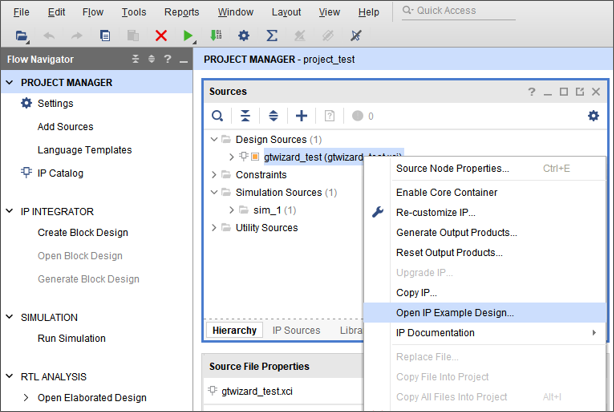

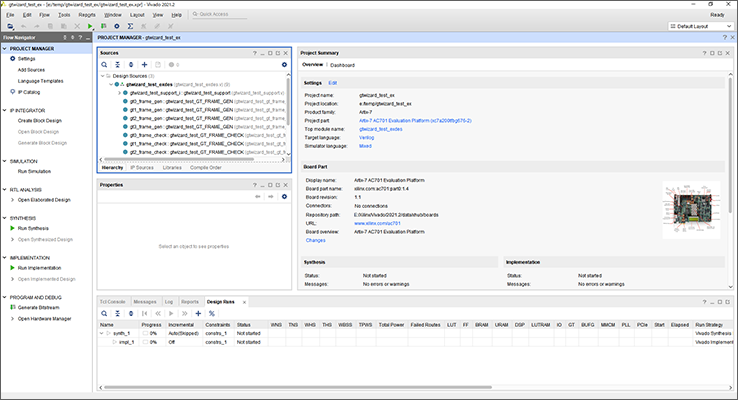

- 2-12.

- 生成されたIPを右クリックし、Open IP Example Designをクリックして、

EXAMPLEデザインが生成します。

(出典:Vivado™ ML Edition)

3. EXAMPLEデザインのカスタム(修正&機能追加)

(出典:Vivado™ ML Edition)

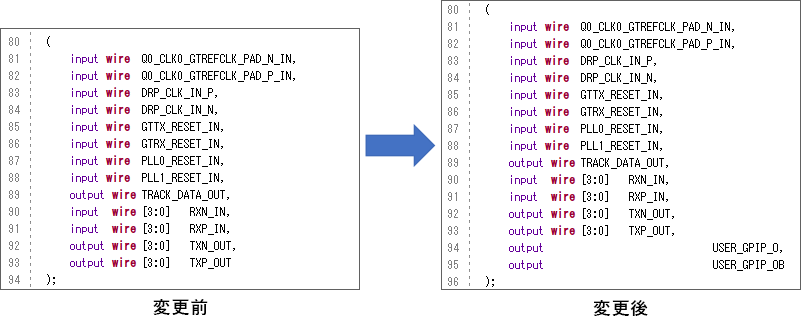

- 3-1.

- EXAMPLEデザインのTOPファイルgtwizard_test_exdes.vを以下のように

PORT USER_GPIP_O, USER_GPIP_OBを追加します。

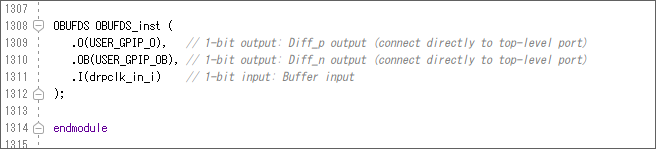

- 3-2.

- EXAMPLEデザインのTOPファイルgtwizard_test_exdes.vを以下のように

OBUFDSを追加します。

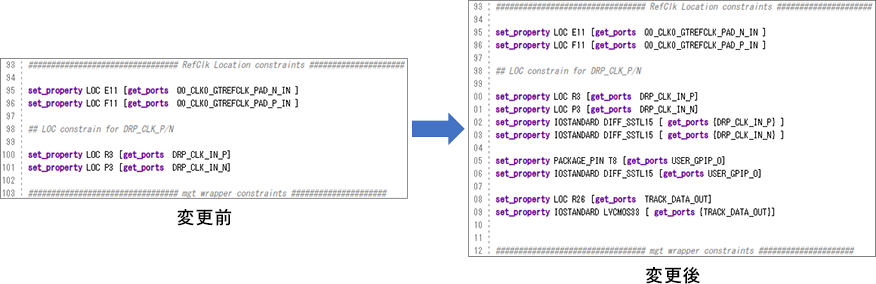

- 3-3.

- EXAMPLEデザインの制約ファイルgtwizard_test_exdes.xdcを以下のように変更します。

- 3-4.

- Generate Bitstreamをクリックし、bitファイルを生成します。

4. 実機(AC701)動作確認

- 4-1.

- Xilinx #AR54139を参考し、評価ボードAC701を出荷状態に設定します。

-

- 注意:

- 注意:#AR54139にあるコンフィギュレーションのモード スイッチ表に以下の記載がありますが、SW13-*は基板シルクよりSW1-*となります。

- コンフィグレーションモードは、下記のJTAGコンフィグレーションモードに設定します。

SW13-3 = AC701 SW1-1 M2

SW13-4 = AC701 SW1-2 M1

SW13-5 = AC701 SW1-3 M0

| Switch | Setting | |

|---|---|---|

| SW13-3 | FPGA_M2 | 1 |

| SW13-4 | FPGA_M1 | 0 |

| SW13-5 | FPGA_M0 | 1 |

- 4-2.

- AC701評価キットのPCIEエッジコネクターに接続治具を接続し、接続治具のREFCLKケーブルを

AC701のUSERR GPIO PとUSERR GPIO Nに接続します。

- 接続治具の仕様は下記LINKのLOOPBACKモジュールを参照、手元にないため、自作の簡易治具で

動作確認しました。

https://www.whizzsystems.com/loopback-card/

- 4-3.

- AC701評価キットのUSB JTAGと電源を接続します。

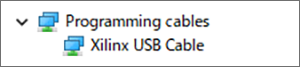

- 4-4.

- PCのデバイスマネージャーに以下のように認識されていることを確認します。

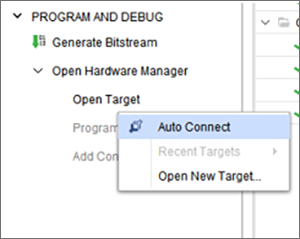

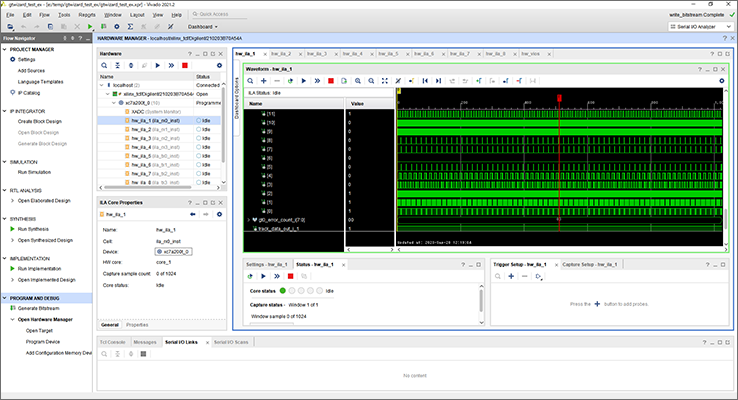

- 4-5.

- Vivado™でEXAMPLEデザインを開いた状態でOpen Hardware Manager→Auto Connectを

クリックします。

- 4-6.

- Program device→Programをクリックします。

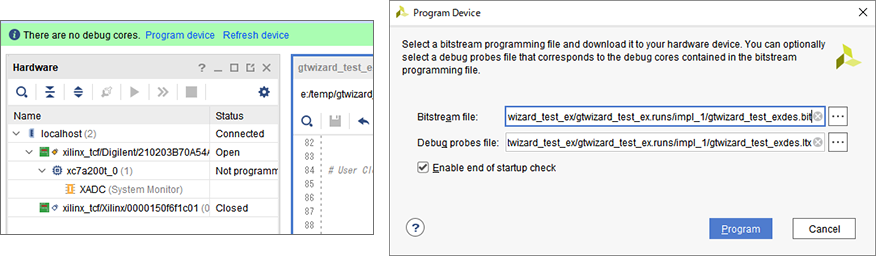

- 4-7.

- Program完了後、AC701のGPIO LED0が点灯し、GTPの送受信できていることを

確認ができます。

- ST_LINK_UP(受信CHECKエラーなし)→ TRACK_DATA_OUT → GPIO LED0

- 下図のようにVivado™ ilaからもDATAが受信していることを確認することは可能です。

(出典:Vivado™ ML Edition)

おわりに

いかがでしたでしょうか。

今回紹介した内容は一例となりますが、本工程でAC701のPCIEエッジ側のGTP通信ができました。

なお、本ブログで使用したEXAMPLEデザインにつきましては以下よりダウンロード可能です。

参考資料(参照2023-09-26)

このブログは「FPGA設計ブログ一覧」の

6. 実機評価のひとつです。

弊社ではFPGA設計や回路図設計、レイアウト設計、ソフトウェア設計、筐体設計などを受託開発しています。

サービス内容をWEBサイトに掲載していますので、ぜひご覧ください。

FPGAの活用に際して設計検討などありましたら、お気軽にお問い合わせください。

最後までお付き合いいただきありがとうございました。