Questa Base / Coreトレーニングウェビナー

いずれも3か月に1~2回開催

- Questa Base / Coreトレーニングウェビナー

- ① シミュレーション・バッチ実行編

- ② シミュレーション・デバッグ編

- ③ コードカバレッジ編

- ④ アサーション編

Siemens EDA/シーメンス EDA

ModelSimは、FPGA開発で最も多く採用されているデファクトスタンダードのHDLシミュレータです。

ModelSimはFPGA開発で最も多く採用されているデファクトスタンダードのHDLシミュレータで、VHDL、Verilog、SystemVerilog設計記述の混在設計をシングルカーネルでシミュレーションします。PSL/SVAアサーションを使用するとバグの発生時間とバグの発生箇所を容易に特定できます。またソースコード、波形、プロセス表示機能とそのクロスハイライト連携によりデバッグ効率が格段に向上します。またコードカバレッジを用いてテストの網羅性を測定し定量化できるため、シミュレーシの抜け、漏れを防ぐことができます。ModelSimは標準規格を厳格にサポートしており、どのような設計フローにも開発プロセスにも、容易に取り込むことが可能です。

ModelSimコマンドオプション一覧表の

ダウンロードはこちら

ModelSimはSystemVerilogの設計構文およびアサーション、Verilog、VHDL、SystemC、PSLといった言語をネイティブにサポートしています。どのような言語混在の設計に対しても優れたシミュレーション性能を実現し、高度なコードカバレッジとデバッグ機能が使用可能です。ModelSimの使いやすさと統合デバッグ/シミュレーション環境は、今日のFPGA設計者に対して、高機能と高い生産性を提供します。

ModelSimでは高度なコードカバレッジ機能と使い勝手の良さにより、ツールラースをより有効に活用できます。コードカバレッジは体系立てられた検証を実現するのに重要なメトイセンス、時間、設計者、計算機といった貴重な検証リソリクスを提供します。測定されたカバレッジはすべて、UCDB(Unified Coverage DataBase)と呼ばれる非常に効率の高いデータベースに収集され、一元化されます。カバレッジのマージやテストランキングなどの解析ユーティリティが備わっており、テスト開発に向けた意思決定が可能です。カバレッジ結果は、各シミュレーション後にインタラクティブに表示することも、複数シミュレーション結果のマージ後をHTML表示することもできます。

ModelSimでは、ステートメントカバレッジ、ブランチカバレッジ、コンディションカバレッジ、エクスプレッションカバレッジ、フォーカスエクスプレッションカバレッジ、トグルカバレッジ、ステートマシン(FSM)カバレッジをサポートしており、これらをUCDBで一元管理することが可能です。

アサーションを使用することで、設計内部で発生する振舞いに対する可視性を上げることができます。これによりバグを特定するまでの時間、バグの修正およびバグが修正されたことを確認するまでの時間を短縮することができます。またアサーションを追加することで、波形を目視確認する作業を自動化することができます。追加されたアサーションは設計とともに再利用することができ、プロジェクトチームや組織として検証の生産性を向上させることができます。

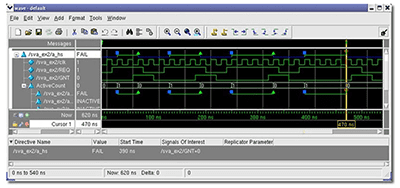

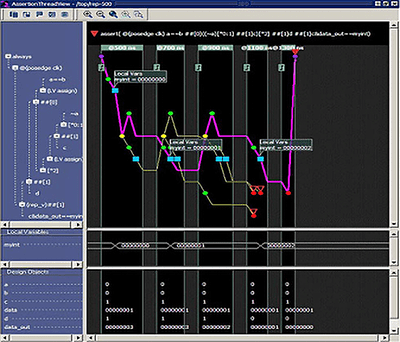

ModelSimでは、SVAやPSL、OVLといったアサーション言語やライブラリをネイティブにサポートしています。記述されたアサーションに指示されたメッセージを表示するだけでなく、パス/フェイルしたアサーションのリスト表示、波形表示が可能です。またサイクルが進むに連れ発生/消滅するスレッドを分かりやすく表示するATV(Assertion Thread Viewer)が搭載されており、アサーションそのもののデバッグや、ローカル変数を使用したアサーションのスレッド解析に有効です。

「アサーションベース設計 立ち上げ支援サービス」をご利用ください

Wilson Research Groupが実施した機能検証の市場調査によれば、アサーションを使用する大多数はSystemVerilog Assertions(SVA)を使用しています。SVAは2005年にIEEE標準となっています。新たな手法が登場したときに、それを開発フローに導入するには、言語の習得に始まり、その効果を評価しては改善するなど、多くの労力を要します。

PALTEKではこの労力を低減し、誰もがアサーションを使い始められるようにするための支援策として、「アサーションベース設計 立ち上げ支援サービス」を提供しています。

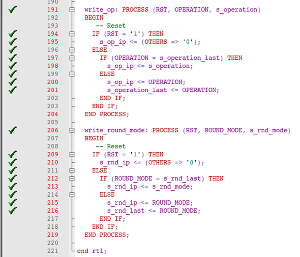

ModelSimのデバッグ環境は、あらゆる言語において、テストデータ、設計データ、コードカバレッジ、アサーションのすべてを効率的に表示し直感的に操作できる環境を提供しています。デバッグや解析はシミュレーション中にリアルタイムで行うことも、またバッチシミュレーション後に保存された結果に対しても実行することが可能です。

ソースコード表示、オブジェクト表示、波形表示などすべてのウィンドウ間においてハイパーリンクによるナビゲーションが可能で、あらゆる角度からデバッグ/解析を進めることができます。ウィンドウ操作は非常に直感的で、本来のデバッグ/解析作業に集中することができます。またデータフロー表示は、バグの原因特定にも威力を発揮します。

※ ModelSim PEは ModelSim DEと同じカーネルを使用し、同じシミュレーション性能を提供しますが、PSL/SVAなどのアサーション機能を使用することはできません。また64ビットOSには対応していません。

ASIC / IC / FPGA 設計業界において、ModelSim/Questaは幅広く活用され多くの実績がございます。

また、多くのエディション/グレードが存在し、お客様の用途に合わせ柔軟な選択が可能です。

弊社経由で ModelSim/Questa Core/Questa Primeの保守/タームライセンス契約をいただいているお客様には、無償でウェビナーや技術資料をご提供しています。

詳しくは 「シーメンスEDAご契約者様向けサービス」 をご覧ください。

いずれも3か月に1~2回開催

3‐4カ月に1回開催

ご希望者へ個別開催