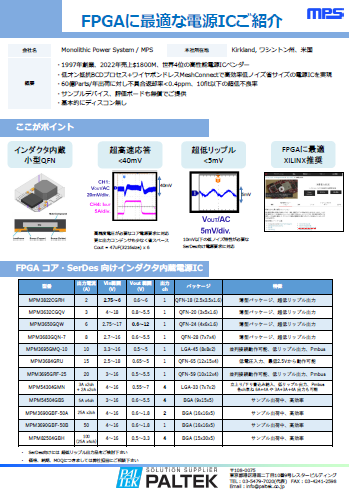

Monolithic Power Systems/モノリシック パワーシステムズ

FPGAに最適な電源IC

超高速応答

基板設計の困りごと高精度な、低電圧・大電流の供給が必要

最新FPGAを採用するたびにコア電圧が低くなり、許容される電圧範囲もどんどん狭くなります。

130nmプロセスを用いたコア電圧1.5V世代のFPGAの論理規模は最大50,000個セル程度でしたが、現在主流の28nmプロセスを用いたコア電圧1.0Vの世代のFPGAの論理規模は40倍の2,000,000個セル以上になりました。

推奨されるコア電圧の範囲は、1.5Vの時は±5%、つまり1.425Vから1.575Vの幅150mVだったのが1.0Vになると±3%、つまり0.97Vから1.03Vの幅60mVと許容される電圧範囲が1/2以下になり電源電圧精度が従来以上に要求される事になりました。

論理規模が大きくなると共に高速シリアルインターフェースの数や速度も向上したため、FPGAに必要になる電流量が大きくなるだけでなく、動的な変動幅もより大きくなりました。つまり電流量が動的に大きく変動する条件下でも、安定して高精度で低電圧かつ大電流を供給する必要が出てきました。

最新の14nmプロセスを用いたFPGAではコア電圧が0.85Vですので、許容される電圧範囲が0.825Vから0.875Vの幅50mVと更に幅が狭まっています。

ご参考:最新FPGAのコア電圧の許容範囲は 0.85V を中心に±25mV / 50mV 以内です

MPSの電源モジュールICなら解決出来ます!

MPSの電源モジュールICのメリット③

超高速応答

- FPGAのコア向け電源に最適

- 出力コンデンサの数量削減が容易

1. FPGAのコア向け電源に最適

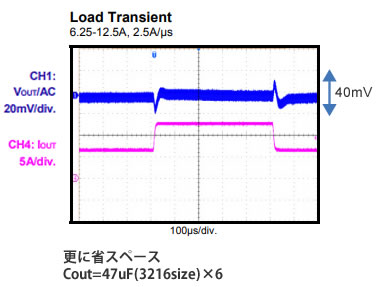

利用場面により急激に変動するFPGAコア電流。変動が6Aから12Aに2.5A/usと急激に変動する過渡応答条件下でも、MPSの電源モジュールICの出力変動は±20mV / 40mV 以内に収まります。コア電圧1V時に定格±3%、つまり±30mV以内の高精度な電圧仕様が必要なFPGAコア電源要求に対応します。

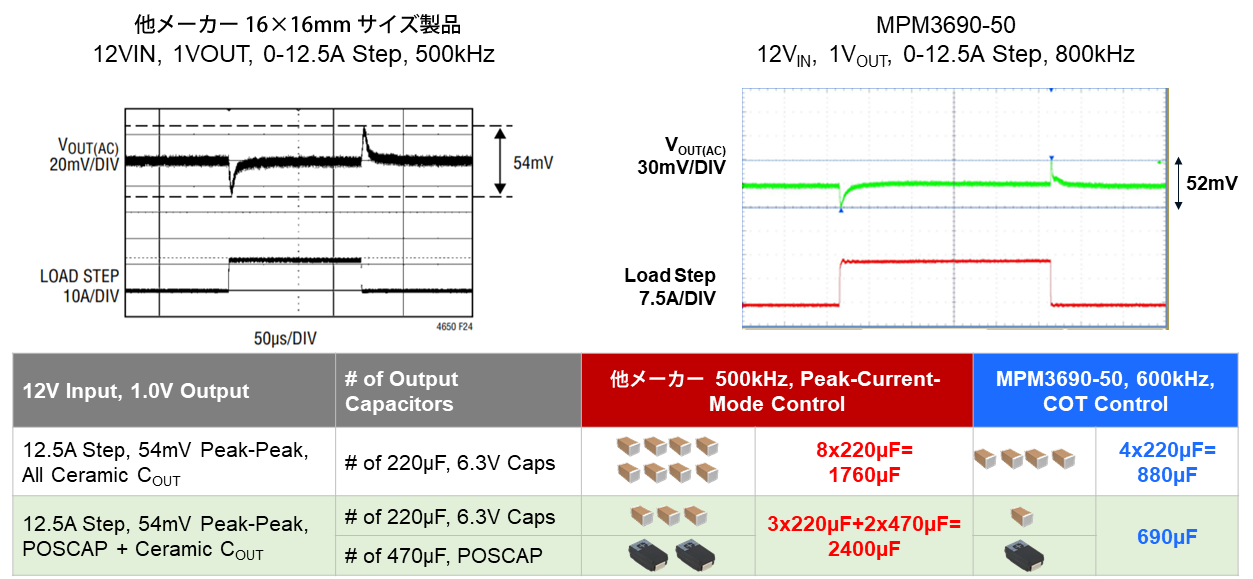

2. 出力コンデンサの数量削減が容易

電源ICの制御方式としてCOT方式を採用しているため、過渡応答が超高速です。同じ負荷変動を実現する場合でも必要な外付け出力コンデンサ容量が圧倒的に少なく済み、コスト低減・基板実装面積削減に役立ちます。

同等な過渡応答を実現しているにもかかわらず、MPSなら必要な出力コンデンサ値は他メーカー比で1/2~1/3以下で済みます。

資料ダウンロード

TECHブログ (電源)

TECHブログ PICK UP

【アナログ回路豆知識】一般的な降圧型DC/DCの電源ICを用いたマイナス電源回路の作り方(実践的な回路例)

- マイナス電源回路の作り方について解説しています

- アナログ系半導体を使った具体的な回路例をお伝えする「アナログ回路豆知識」。今回は、「マイナス電源回路」の作り方と題してお送りします。

専用の設計部品を使用するのではなく、一般的な降圧型DC/DCの電源ICを用いてマイナス電源回路を構築します。

MPSのことなら

PALTEKにご相談ください!

- Advanet

- Advantech

- AMD

- ATP Electronics

- AudioCodes

- Bellnix

- Congatec

- EFCO

- GSI Technology

- iBASE Technology

- Macom Technology Solutions

- MaxLinear

- MEAN WELL

- Microchip Technology

- Micron Technology

- Monolithic Power Systems (MPS)

- Nexperia

- Plunify

- Siemens EDA(旧Mentor Graphics)

- SiTime

- TELEDYNE FLIR

- Toppan Technical Design Center