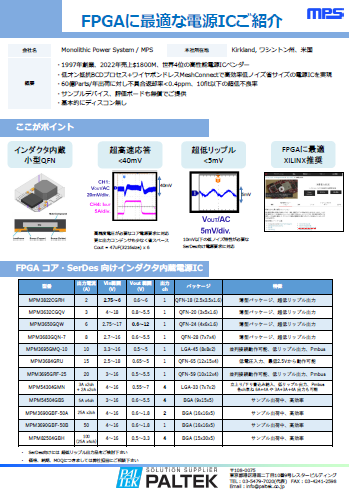

Monolithic Power Systems/モノリシック パワーシステムズ

FPGAに最適な電源IC

インダクタ内蔵・小型QFNパッケージ

基板設計の困りごと基板サイズをより小さく

FPGA基板の高機能化が進んでいて、搭載される部品点数は増加、基板サイズは小さくすることが求められる。

FPGAが搭載される基板の高機能化が進んでいます。

物理的な観点では、基板に搭載される部品数が増えること、より基板サイズを小さくすること事、またはその両方が含まれます。

搭載される部品数が増えると基板の実装密度が高くなるので、基板の配線の自由度が小さくなります。

逆に電源部分の基板実装面積が小さくなれば、基板の配線に費やせる面積が増えるので、より余裕を持った基板設計が可能です。

パッケージの小型化に加えて電源の周辺部品数の削減も行えれば、大きな基板実装面積削減が狙えます。これは、より基板サイズを小さくする事に対しても有効です。

MPSの電源モジュールICなら解決出来ます!

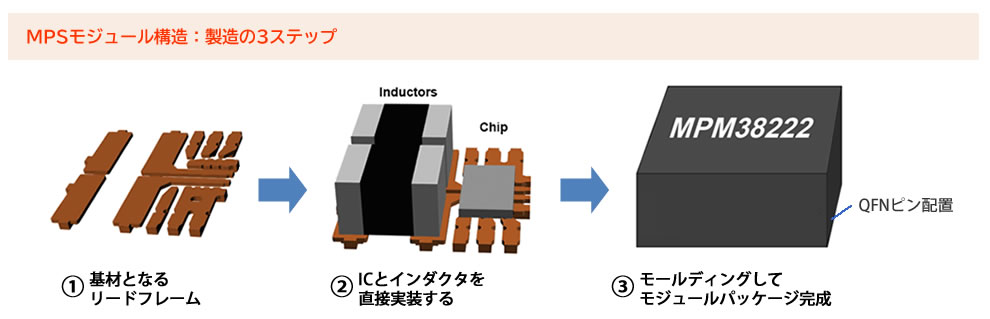

MPSの電源モジュールICのメリット①

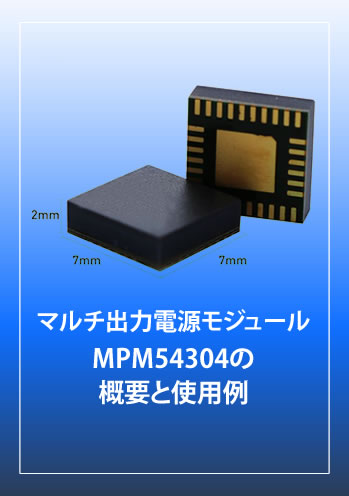

インダクタ内蔵・小型QFNパッケージ

- 高信頼で低コスト、低ノイズ

- 基板実装検査が容易

- 工夫されたピン配置

- パッケージサイズが小型

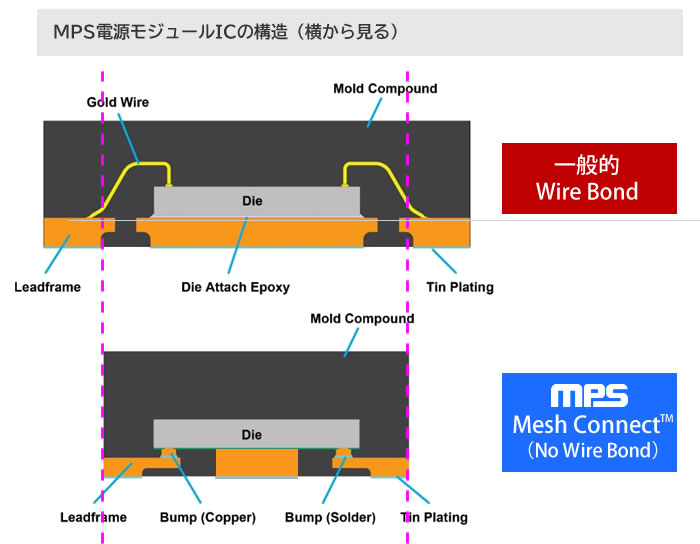

1. 高信頼で低コスト、低ノイズ

通常のIC内部で使われる金属リードフレームを電源モジュールICの基材に採用しています。このリードフレーム上にDCDC-ICやインダクタなど各部品を直接接合するMesh-Connect構造を取るためにシンプルで高信頼なパッケージを低価格で実現しています。直接接合するためワイヤボンディングに起因するL成分/インダクタ成分を排除出来るため、低ノイズ化も同時に実現します。

2. 基板実装検査が容易

MPSの電源モジュールICの多くのパッケージはQFNです。 X線検査機が必須なLGA/BGAパッケージの基板実装検査工程に比べて検査が容易です。またLGA/BGAパッケージの実装不具合の際に必要なリワーク設備も不要です。

3. 工夫されたピン配置

MPSの電源モジュールICの出荷試験が容易になるピン配置のため、出荷時の検証時間短縮を実現します。ノイズ対策も考慮したピン配置になっています。

4. パッケージサイズが小型

ワイヤボンディング不要なMesh-Connect構造のため、パッケージ横方向の退避エリアが削除できます。一般的なワイヤボンド品に比べ、同じダイサイズでもパッケージを小型にする事が可能です。

資料ダウンロード

TECHブログ (電源)

TECHブログ PICK UP

【アナログ回路豆知識】一般的な降圧型DC/DCの電源ICを用いたマイナス電源回路の作り方(実践的な回路例)

- マイナス電源回路の作り方について解説しています

- アナログ系半導体を使った具体的な回路例をお伝えする「アナログ回路豆知識」。今回は、「マイナス電源回路」の作り方と題してお送りします。

専用の設計部品を使用するのではなく、一般的な降圧型DC/DCの電源ICを用いてマイナス電源回路を構築します。

MPSのことなら

PALTEKにご相談ください!

- Advanet

- Advantech

- AMD

- ATP Electronics

- AudioCodes

- Bellnix

- Congatec

- EFCO

- GSI Technology

- iBASE Technology

- Macom Technology Solutions

- MaxLinear

- MEAN WELL

- Microchip Technology

- Micron Technology

- Monolithic Power Systems (MPS)

- Nexperia

- Plunify

- Siemens EDA(旧Mentor Graphics)

- SiTime

- TELEDYNE FLIR

- Toppan Technical Design Center