モデルベースデザイン(MBD)を活用したモータ制御のFPGA実装 第2回 -具体例-

― 文:MathWorks Japan プリンシパルHDLプロダクトスペシャリスト 松本 充史 氏

目次

前回こちらの記事でモータ制御におけるFPGAの活用方法について、概念的な説明をしました。

今回はモータ制御アルゴリズムをFPGAに実装する具体例を紹介します。

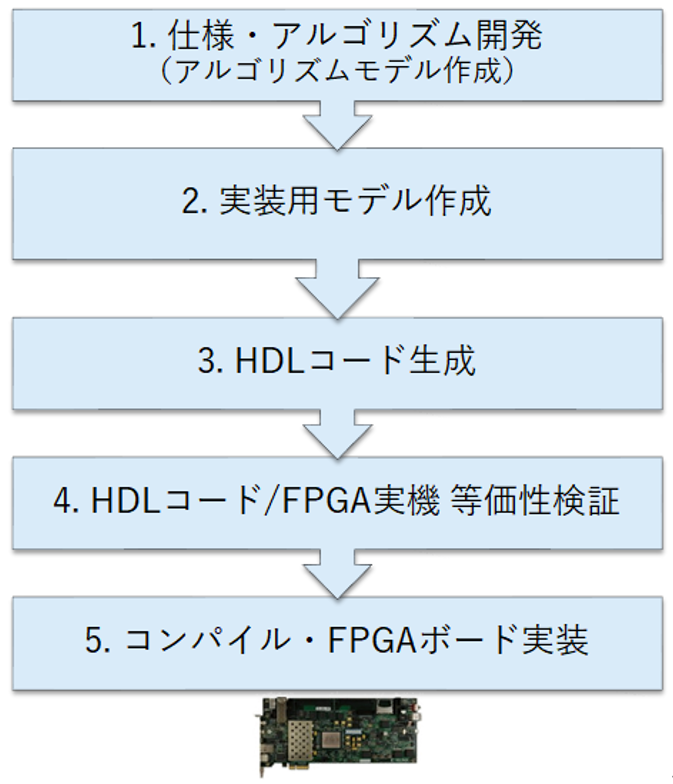

設計フロー

モデルベースデザインによるFPGA実装フローは大まかに示すと以下のようになります。

まず、要求仕様で示されている内容や、エンジニアの頭の中にある機能アイデアなどをモデル化し、実現可能性をシミュレーションで確認します。

それを実装用モデル、HDLコードへと手動または自動で段階的に変換していき、最終的にはFPGA実機に実装します。手動・自動に関わらず、変換したらシミュレーション結果を比較し、等価性を担保しながら開発を進めます。

1. 仕様・アルゴリズム開発

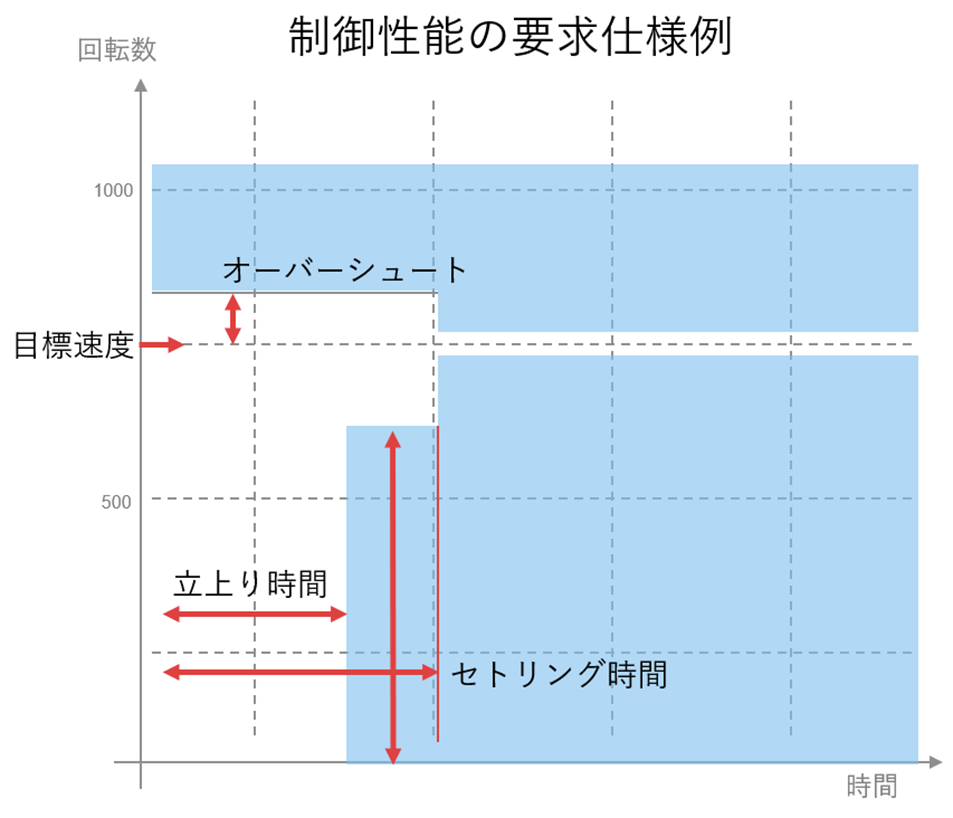

フローの最初のステップは仕様・アルゴリズム開発です。ここではまず設計対象が含まれるシステムをモデル化して、要求性能を定義し、システムとしての応答をシミュレーションで解析します。

本TECHブログではこのモデルを「アルゴリズム モデル」と呼ぶことにしましょう。アルゴリズム モデルでは、プラントモデル、コントローラ、外乱など要求仕様を満たすために考慮が必要な要素を含めたシステムモデルを作成して、シミュレーションにより、要求達成可否を十分に解析します。基本的には、ここで設計したものと等価なアルゴリズムがFPGAに実装されることになるため、ここでの要求の定義やシミュレーションによる達成・未達の解析は非常に重要です。

下の例では、モータの速度制御におけるオーバーシュート量や立ち上り/セトリング時間などを定義して、それをコントローラやプラントモデルで構成されるシミュレーションによって、達成可否を確認します。

さらに対外乱性能に対して評価します。下図で示す例では、負荷トルク変動を与え、回転数が必要以上に低下しないかを評価しています。

ここで作成するアルゴリズム モデルは、機能と演算精度を切り分けて評価できるよう、FPGAデバイスに実装する固定小数点データ型ではなく、演算誤差がほとんどない倍精度浮動小数点(double型)に設定します。

2. 実装用モデル作成

Simulink®ブロックの中でアドオン製品のHDL Coderを用いてHDLコード生成に対応しているブロックは限定されています。前のステップで作成したモデルの中で、HDLコード生成に対応していないブロックを対応したブロックに置き換えます。

Simulink®標準ライブラリやDSP System Toolboxなどのアドオン製品で対応しているブロックは、それぞれHDL CoderやHDL Supportライブラリに格納されています。

またここでは、演算精度を、FPGA実装することを考慮した固定小数点データ型に変更します。

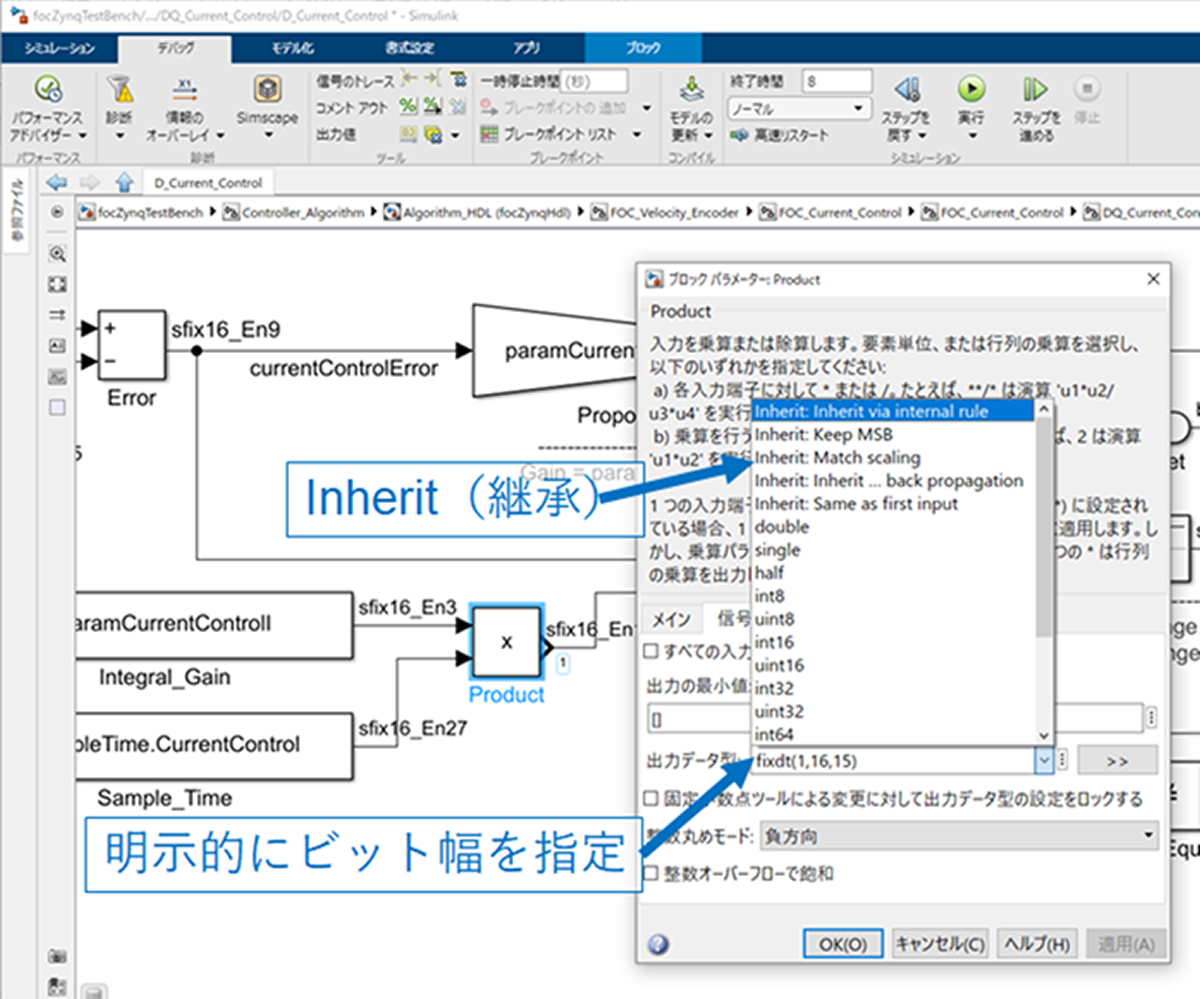

各ブロックにはデータ型設定のタブがあり、任意のビット幅でのデータ型設定ができるようになっています。全ブロックに対してデータ型設定を行う必要はなく、Inherit設定では、入力信号のデータ型に応じて出力信号のデータ型が自動的に変わるようになっています。

また、固定小数点化による意図しないオーバーフローや精度劣化に対しては、固定小数点ツールと呼ばれる、演算精度要求に対する自動最適化機能があります。適宜これらの自動設定と明示的なデータ型設定を使い分けて、設定作業を省力化できるため、VHDL/Verilogコードを記述するよりもはるかに楽に設計できます。

実装用モデルを作成する際には、アルゴリズムモデルと等価性を担保しながら行います。

ただし、固定小数点化を行うと演算誤差が発生し、完全等価とはなりませんので、許容誤差や要求仕様の達成・未達という観点で行います。このステップで決まった固定小数点データ型での実装用モデル単体(プラントやアナログ回路など周辺要素を含まない)の動作は、FPGA実機とビット単位で完全等価となるため、ここでの要求仕様の達成可否は、最終的なFPGA実機の完成度を考えると非常に重要になります。

3. HDLコード生成

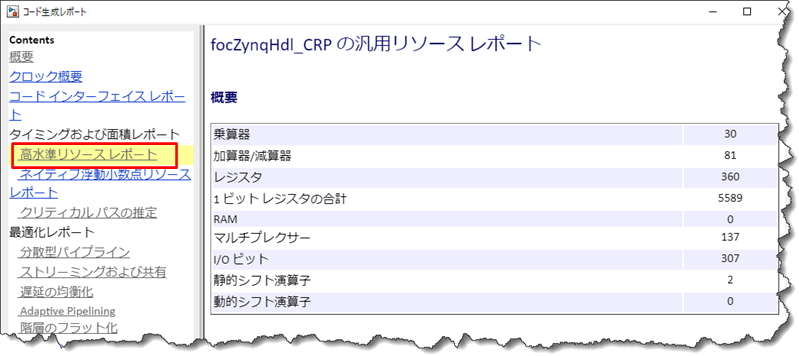

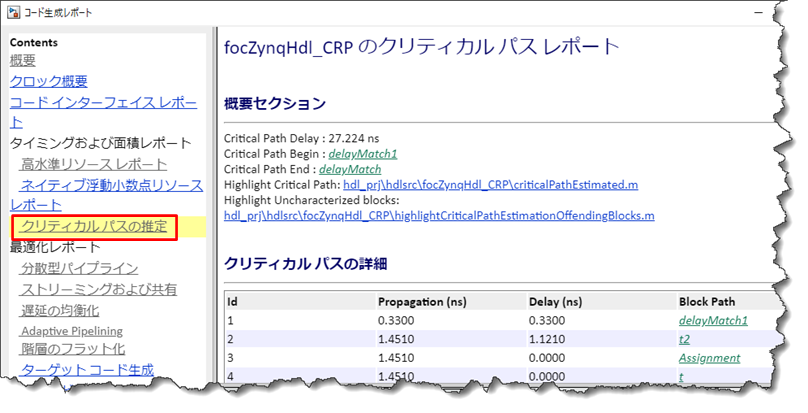

実装用モデルが完成したら、HDLコード生成を試しに行ってみます。HDLコード生成後に表示される「コード生成レポート」から、回路リソースの規模や達成可能なFPGAクロック周波数を推測することができます。

「高水準リソースレポート」からは、必要となるDSPブロックやFFの個数がわかるので、ターゲットとしているFPGAのリソースをオーバーしていないかどうかで確認します。

また、クロック周波数に関しては、最大遅延回路パスを示す「クリティカルパスの推定」の値から逆算します。

リソース数がオーバーしているときは、時分割リソース共有を行って、使用するFPGAの回路リソースを削減します。クロック周波数が未達の場合は、Flip-Flop回路素子に相当するDelayブロックを追加挿入してパイプラン段数を追加します。

これらの値はあくまでHDL Coderが推定した結果ですので、最終的にはステップ5で行う、FPGAツールのコンパイル結果から判断します。

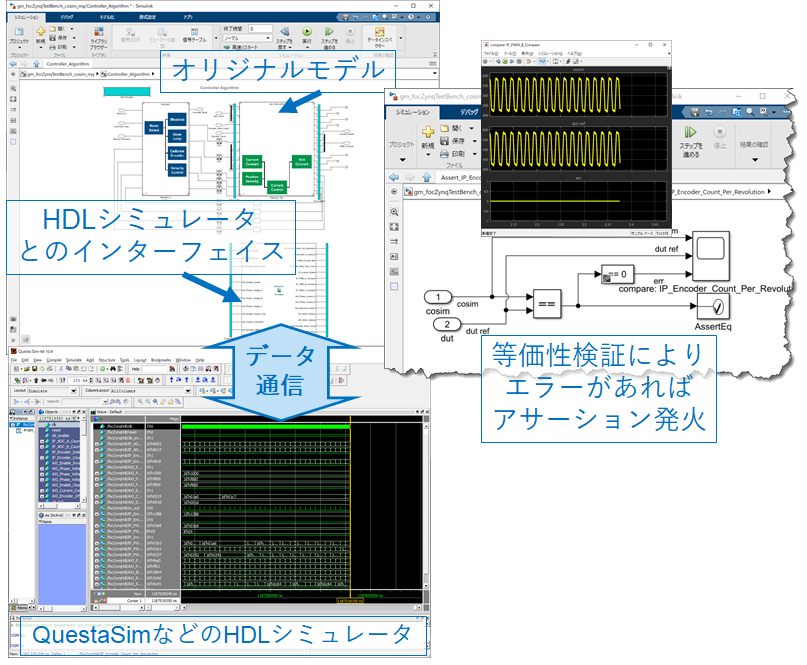

4. HDLコード/FPGA実機検証

このステップではツールの自動変換が正しく実施されたか確認を行います。

まずHDL Coderが正しくコードを生成したか検証します。そのためには、HDLコードを実行するHDLシミュレータと、信号入力や期待値との照合を行うテストベンチを担うSimulink®を連携してシミュレーション(コ・シミュレーション)を行います。

何らかの不具合により、HDL Coderが生成したコードが等価性を保っていない場合、ユーザが作成したオリジナルモデルの出力と、HDLコード間で生じる誤差により、エラーが発生します。

さらにFPGAボード実機でもFPGA-in-the-Loop機能を用いて同様のことを行います。FPGAツールによるコンパイル(論理合成)時に等価性に欠陥が生じてしまった場合には、ここでエラーを検出することができます。

HDLコード生成やFPGAツールによるコンパイルは、非常に低い確率でしか不具合が発生しないので、念のための検証作業の意味合いが強いです。

一方で、ハンドコーディングのHDLコードに対してHDLコ・シミュレーションやFPGA-in-the-Loopによる等価性検証を行うと、不具合発見確率は非常に高く、より有効性も高いといえます。

従来、ハンドコーディングでHDLコードを書きながら並行して固定小数点化を行うと、等価性の欠如が固定小数点化による誤差なのか、HDLコードの記述間違いによる機能的な不具合なのか区別がつかないことがありました。そうならないよう、モデルベースデザインでは、継続的かつ段階的に等価性をチェックしながら作業を進めていき、等価性を確実に担保することができるようになっています。

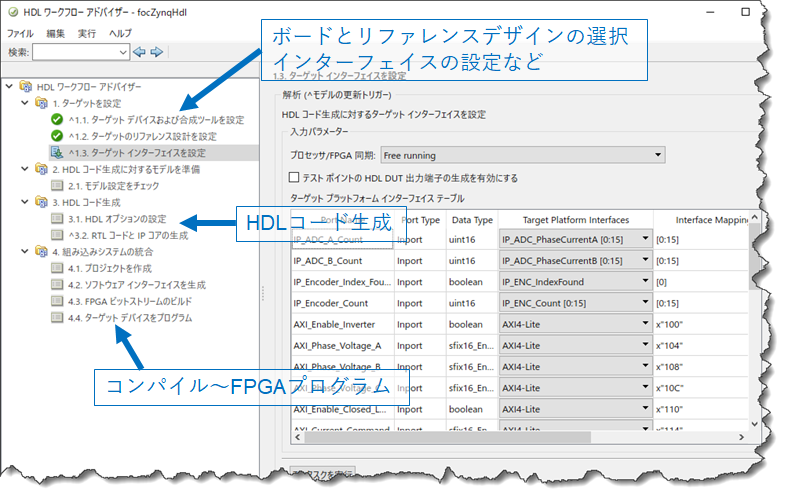

5. コンパイル・FPGAボード実装

所望の機能を、満足のいく回路性能(動作周波数、回路リソース)でHDLコード生成できる見込みが立ったら、Xilinx社のVivado®などのFPGAツールと連携を行うHDLワークフローアドバイザーを起動して、FPGA実機への実装を行います。

下図に示すように、HDLワークフローアドバイザー上では、FPGAボード、リファレンス・デザイン、インターフェイスの設定、HDLコード生成、コンパイル、デバイスのプログラムを順に行います。

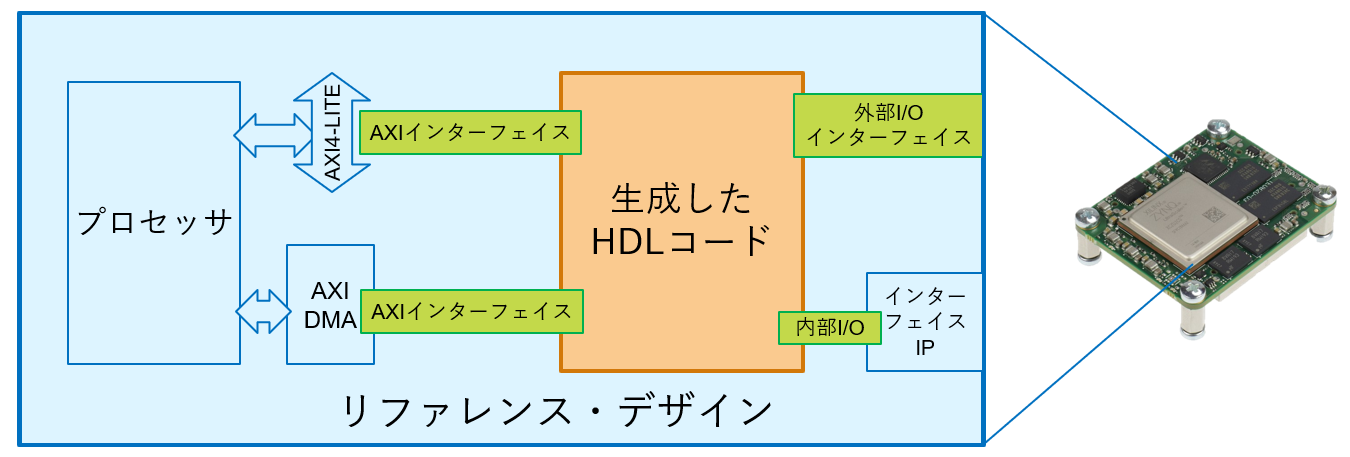

HDLワークフローアドバイザーを使用して開発ボードに実装する際には、予めリファレンス・デザインを準備しておきます。リファレンス・デザインは下図に示すように、FPGAやSoCデバイスの外部・内部I/OインターフェイスやAXIインターフェイスを定義したファイルです。

主要な開発ボードに対しては、無償でダウンロード・インストールできるハードウェア・サポート・パッケージでリファレンス・デザインを提供しています。

本TECHブログで使用しているサンプルモデルでは、Trenz Electronic GmbH社が販売する、「Trenz Electronic Motor Control Development Kit Support from Simulink」を使用して、Xilinx社のZynq® UltraScale+™ MPSoCを搭載したモータ制御用ボードに対して実装しています。

本TECHブログでは、FPGA実装に着目して説明していますが、このモデルにはプロセッサに実装するアルゴリズムも含まれており

- SoC FPGAデバイスのPS側にCコード生成し、モータの速度制御

- PL側にHDLコード生成し、モータの電流制御

を実装しています。

実機検証

FPGA-in-the-Loopでは非リアルタイムで、FPGAの単体機能検証は実施済みですが、最終段階としてリアルタイムで、プロセッサとインターフェイスを含むFPGAを、プラントも含めた閉ループで統合検証を行います。

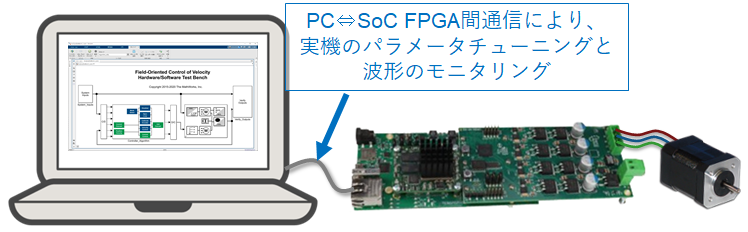

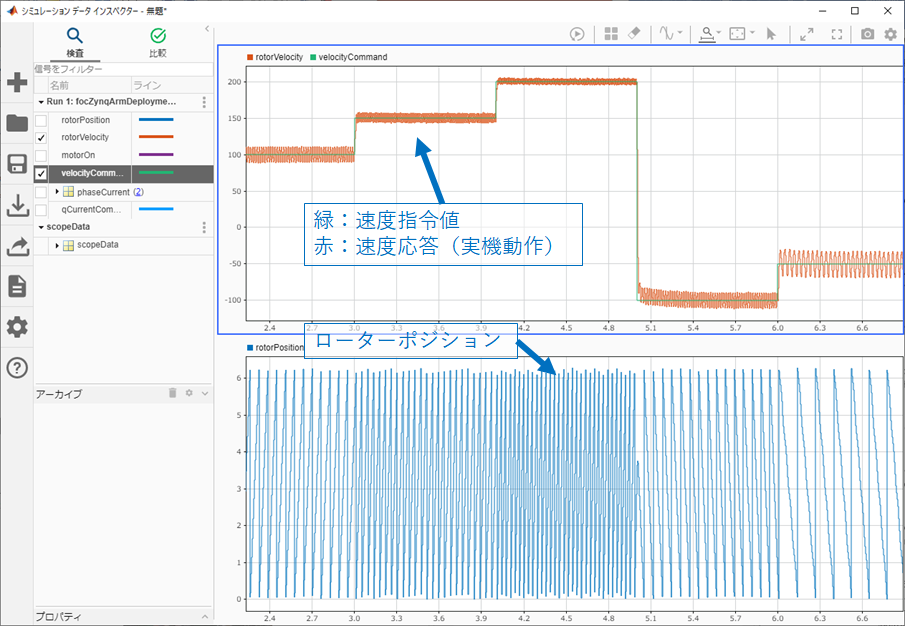

エクスターナルモードを使用して、MathWorks社が開発するPC上のMATLABとSoCデバイスが通信しながら実機の動作検証を行います。

エクスターナルモードは、ターゲット デバイスのプロセッサとPC間で双方向の通信を行うことで、パラメータの調整と、動作結果のログを取る動作モードです。

ログは実行後、可視化して、シミュレーション結果と比較することができます。

最後に

本TECHブログではモータの速度制御を題材に、モデルベースデザインによる具体的な開発ステップについて説明しました。この手法では、モータ制御などのアルゴリズムを手戻りやバグの混入を極力削減して、要求性能を確実に満足するFPGA実装を行うことができます。試してみたいと思われましたら、PALTEKまたはMathWorks社までご相談ください。

参考資料

- HDL Coder製品ページ

- モータ制御向けHDL実装ガイドラインおよびサンプルファイル:これからHDL Coderを使用してモータ制御のFPGA実装を行う方向けの利用ガイド

告知

2021年12月2日(木)に、実際にモデルベースデザインによるFPGA/ASIC設計フローを体験することができるハンズオン体験会「モデルベースデザインによるFPGA/ASIC実装【オンライン無料体験会】」を開催します。ご興味お持ちの方は、こちらからお申し込みください。

執筆者紹介

MathWorks Japan プリンシパルHDLプロダクトスペシャリスト 松本 充史 氏

電子機器メーカーにて信号処理アルゴリズム開発、電子回路設計に従事後、MATLABの国内代理店にアプリケーションエンジニアとして入社し、信号処理・画像処理、C、HDLコード生成などを担当。現在は主にFPGA/ASIC実装分野のアプリケーションエンジニアとして、ユーザのサポート、機能やユーザビリティ向上のための活動を中心に行っている。