モデルベースデザイン(MBD)を活用したOFDM方式ソフトウェア無線(SDR)のRFSoC実装

― 文:MathWorks Japan シニアアプリケーションエンジニア 中村 勝氏

本ブログでは、ソフトウェア無線機の開発を大幅に加速いただくための手法として、モデルベースデザイン(MBD)とXilinx社のRFSoCボードを併用した開発ソリューションを紹介します。そのあとに、OFDM送受信機の具体的実装例も併せて紹介します。

目次

はじめに

日本でも5Gがようやく普及期に入り、工場やケーブルテレビなどでの ローカル5G の商業利用にも大きな期待が寄せられています。一方、研究開発の領域では既に次世代の6G(Beyond 5G)への取り組みが各国の研究機関・企業で進められており、5Gでの ビームフォーミング を利用した Massive MIMO や OFDM(Orthogonal Frequency Division Multiplexing) といった多重化技術の更なる高度化・高速化に取り組まれています。

このような次世代の無線技術の研究開発を進める上で ソフトウェア無線(SDR:Software Defined Radio) 開発用プラットフォームの利用は欠かせません。近年、 FPGA 内蔵SoC(System On Chip)デバイスにRFインターフェースも内蔵したRFSoCと呼ばれるデバイスが利用可能となり、これを搭載した市販評価ボードを利用することで実ハードウェアについては新たに開発することなくソフトウェア無線の研究開発から試作評価まで行えるようになりました。

しかし、ソフトウェア無線機を実際に開発するとなると、仕様検討から始まって信号処理アルゴリズムの作成とシミュレーション評価、実装に向けたアルゴリズムのハード/ソフトへの切り分け、ハード/ソフトそれぞれのコーディングと検証、検証済みコードの評価ボードへの実装と実機評価に至るまでの膨大な作業が必要となります。

従来、これらの多岐にわたる作業は複数の人が異なる開発環境で進めることが多かったため、作業間で等価性が保たれずに当初の設計仕様と試作機の実際の機能・性能が一致しないという課題が多々見られます。

そこで、本ブログではこのような状況を改善し、ソフトウェア無線機の開発を大幅に加速いただくための手法としてモデルベースデザイン(MBD)とRFSoCボード(Xilinx社のZynq® UltraScale+™ RFSoC ZCU111 評価キット)を併用した開発ソリューションをOFDM送受信機の具体的実装例と共に紹介します。

ソフトウェア無線(SDR)の市販評価ボードを用いた開発フローと課題

ソフトウェア無線の実装対象ハードウェアとしてRFSoCやRFインターフェースを備えたFPGA内蔵SoCを搭載した評価ボードを用いる場合、実ハードウェア自体の開発は不要となる一方で、SoC内のFPGAに書込むハードウェア回路情報とプロセッサ上で走るソフトウェアの開発と検証が主要開発課題となるため、以下に示すステップで開発が進められているのではないでしょうか。

- (1) 開発仕様の検討作成

- (2) 仕様を元にした信号処理などのアルゴリズム作成とシミュレーションによる検証

- (3) 実RF込みのアルゴリズム検証(計測器などでRF伝搬路を含む受信信号を生成し検証)

- (4) アルゴリズムを元にした実装用HDL/Cコードの作成及び検証

- (5) 実装用HDL/CコードのFPGA内蔵SoC評価ボードへの実装

- (6) FPGA内蔵SoC評価ボードによるソフトウェア無線機の実機検証と特性評価

以上の作業を実際に進める際は、技術領域が多岐に渡るためにこれらの作業を複数メンバーで分担して、次のようにそれぞれ別々の環境で行われる場合が多いようです。

- アルゴリズム担当者:MATLAB®でアルゴリズム作成と検証

- HW担当者:Verilog/VHDLでHDLコードを作成して論理シミュレータで検証後SoC内のFPGA部に実装

- SW担当者:Cコードを作成してSoC内のプロセッサ部に実装してソフトウェア無線機単体での動作検証

- システム評価担当者:複数の無線機を用い実環境で通信特性の評価

しかし、このようなフローで開発を進めると、アルゴリズム担当者が作成・検証したMATLABコードをHW/SW担当者が活用せず、実装用HDL/Cコードを改めて作成するため、仕様の伝達ミスやバグの混入により両者間の等価性が保てないリスクが内在する可能性があります。

また、領域毎の開発環境が異なるため基準となるMATLABコードと実装用HDL/Cコード間の等価性を検証することもとても困難で工数もかかるという課題があります。

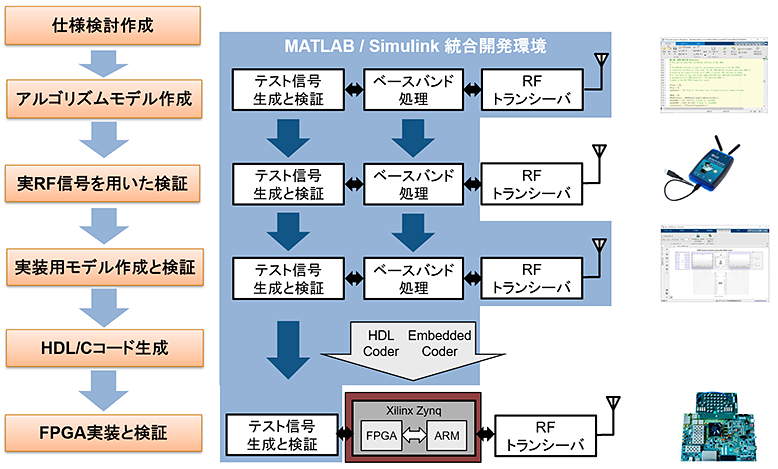

モデルベースデザイン(MBD)を併用したソフトウェア無線(SDR)の開発フロー

以上の開発フロー上の課題を解決し、開発効率を大幅に改善するための対応策として、異なる技術領域にわたる開発環境を1つに統合し、各ステップでの開発物を再利用して次ステップの開発物を可能な限り自動生成し、ステップ間での等価性も自動で検証できるようにしていくことが効果的です。

これを実現する具体的な統合開発環境としてMATLAB、Simulink®を利用したモデルベースデザイン(MBD)による開発ソリューションを以下に紹介します。

MATLAB、Simulinkを用いたソフトウェア無線の開発フローはおよそ次のとおりです。

- (1) 開発仕様の検討作成

- (2) アルゴリズムのモデル化とシミュレーションによる検証

- (3) 実RF信号を用いたアルゴリズム検証

- (4) 実装用モデルの作成と元アルゴリズムとの等価検証

- (5) 実装モデルからのHDL/Cコードの自動生成

- (6) 実装用HDL/CコードのFPGA内蔵SoC評価ボードへの実装と実機検証

出典:MathWorks Japan

MBDによるOFDM方式ソフトウェア無線のRFSoC実装例の紹介

以降のパートでは、ソフトウェア無線の開発の一例としてOFDM送受信機を題材として、前記開発フローにある開発仕様の作成からRFSoCボードへの実装に至る各ステップの内容について概要を紹介します。

(1) 開発仕様の検討作成

無線通信分野では相互接続が必須なため、携帯などの商用通信では詳細な仕様が標準規格として規定されています。そのため、6Gなどの次世代無線機の研究開発では開発ターゲットの仕様として既存の5Gなどの標準規格をベースにこれを改良する形で進むことが期待されます。幸いMATLABではLTE、5G、WLANの各規格に準拠したシミュレーション用のMATLAB関数や参照例を含むToolboxが用意されており、これらをベースに改良を加えていくことで次世代の無線方式や独自方式の研究開発を進めることが可能です。

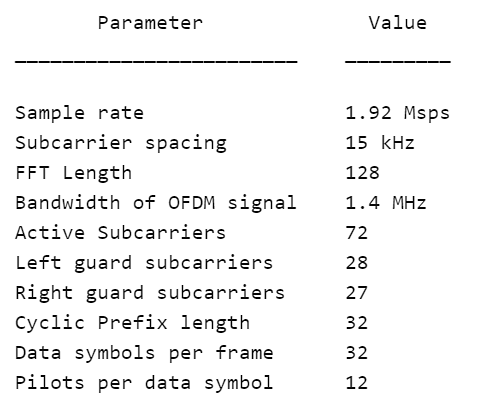

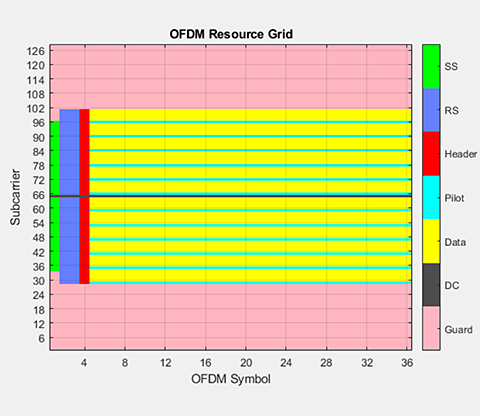

ここでは、Toolbox内の例として提供されているOFDM送受信用MATLAB関数を利用してOFDM送受信機の仕様を決めていきます。本MATLAB関数の主要パラメータ及びリソースグリッドは以下のとおりで、このサンプル自体は特定の規格に準拠したものではありません。シンボルのサンプルレートは1.92Msps、FFT長は128に設定しています。また、サブキャリア毎の変調方式は16QAMとし、符号化率は1/2とします。

出典:MathWorks HDL OFDM Transmitter

https://jp.mathworks.com/help/wireless-hdl/ug/hdlofdmtransmitter.html (参照 2022/02/09)

(2) アルゴリズムのモデル化とシミュレーションによる検証

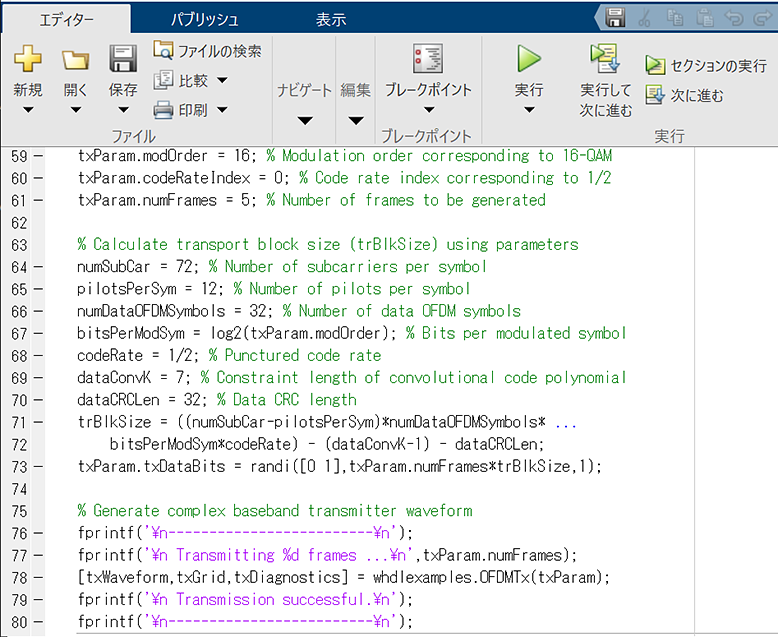

前節でふれたOFDM送受信用MATLAB関数と仕様パラメータ、及び新たに特性評価のため白色ガウス雑音を生成するMATLAB関数も用い、OFDM送受信機と雑音源のアルゴリズムをモデル化した送受信システム全体のMATLABスクリプトを作成します。

作成するといっても今回の例ではOFDMのアルゴリズム自体は既にMATLAB関数として用意されているため、次のようにOFDMTx関数に対して必要なパラメータを指定するだけでOFDM送信機の信号生成が可能です。

出典:MATLABエディタ

同様にしてこの信号にhdlawgn関数で生成した白色ガウス雑音を加算した信号を受信信号とし、これをOFDM受信機のアルゴリズムを実装したOFDMRx関数に入力することで受信データが再生されます。

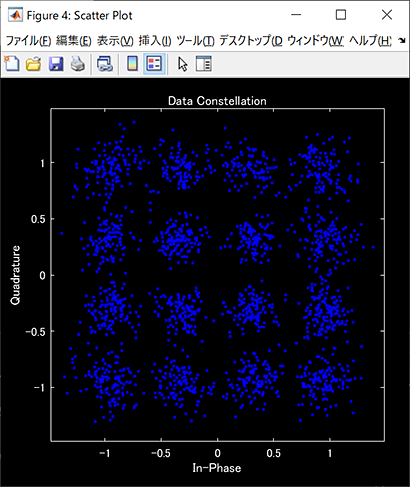

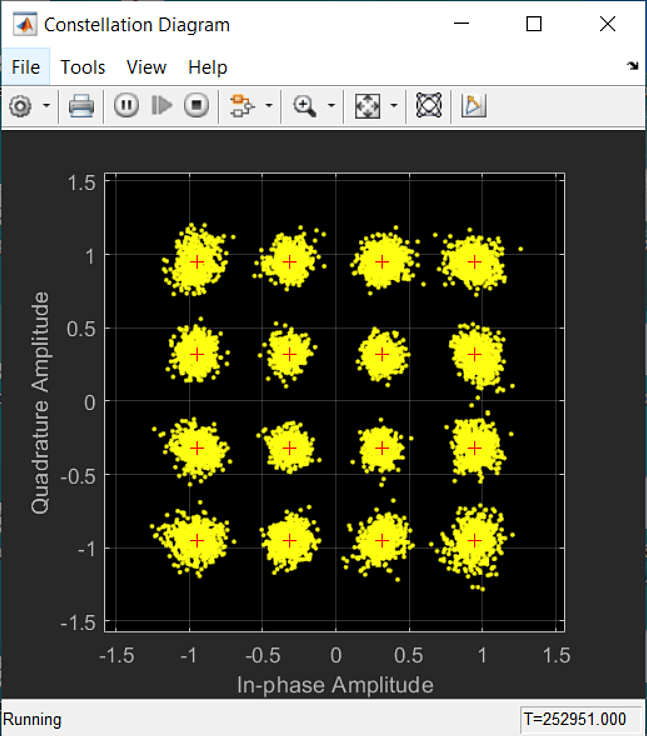

このスクリプトでシミュレーションを行うことで、雑音源に対して指定したSN比と送受信データから求めた誤り率を用いてSN比に対するBER特性について評価、検証を行うことができます。シミュレーションの結果の例としてSN比を15dBとした場合のOFDM受信復調後の16QAMのコンステレーション図を次に示します。

出典:MathWorks Japan

(3) 実RF信号を用いたアルゴリズム検証

前節では白色ガウス雑音のみの簡易な伝搬路を含む送受信システム全体をMATLABスクリプトで記述し、これをシミュレーションしてOFDM送受信アルゴリズムの動作検証と特性評価を行いました。

しかし、実際の伝搬路には送受信機間の伝搬路以外にRFデバイスやアンテナも含まれるためこれらの特性についても考慮が必要ですし、空間伝搬路自体も場所によって伝搬特性が大きく異なり様々な干渉による劣化も生じるため、作成したアルゴリズムが実際の伝搬環境でも所望の動作をすることを実装開発フェーズに移る前に検証しておくことが場合によっては必要となります。

そのための方法としてPCに直接つながるRFデバイスを利用してPC上のMATLABで生成したベースバンド信号を無線帯域で送信する一方、無線帯域で受信した信号をRFデバイスでベースバンド信号に変換してMATLABで受信し、受信したベースバンド信号を後程MATLAB上のアルゴリズムを用いて復調する、という手段がハードウェアサポートパッケージとして数種類用意されています。

これらのパッケージを利用することで、例えば次図のようなソフトウェア無線用モジュール(ADALM-PLUTO)やXilinx社のZynq®ボードを利用して実RF信号をMATLABから送信したり、逆に実RF信号をMATLABで受信したりすることができるため、実RF信号を利用してOFDM送受信機のアルゴリズム検証を進めることが可能です。

実RF信号を用いたシミュレーションで所望の特性が得られるようになったら、その際のMATLABアルゴリズムを実装開発の基準アルゴリズムにします。

出典:MathWorks Communications Toolbox Support Package for Analog Devices ADALM-Pluto Radio

https://jp.mathworks.com/matlabcentral/fileexchange/61624-communications-toolbox-support-package-for-analog-devices-adalm-pluto-radio (参照 2022/02/09)

(4) 実装用モデルの作成と元アルゴリズムとの等価検証

前節で確定したOFDM送受信機のアルゴリズムを基準として、ここからは実装用モデルの作成に移ります。

アルゴリズムモデルでは本来時系列の送受信信号を時間概念のない行列形式のフレーム単位で表記していましたが、実ハードウェアでは送受信信号は時系列サンプルデータとなるため、実装用モデルとアルゴリズムモデル間では内部のアーキテクチャが大きく異なります。

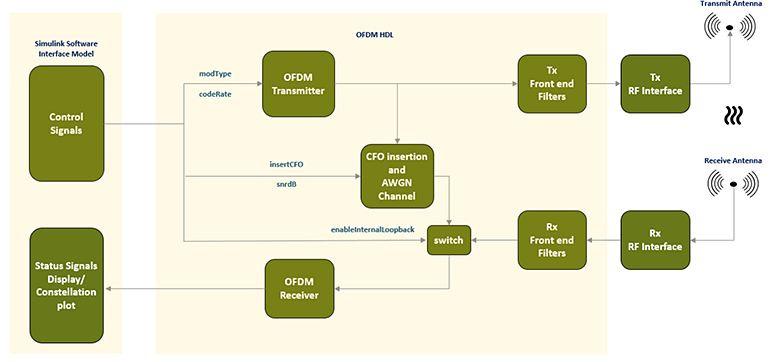

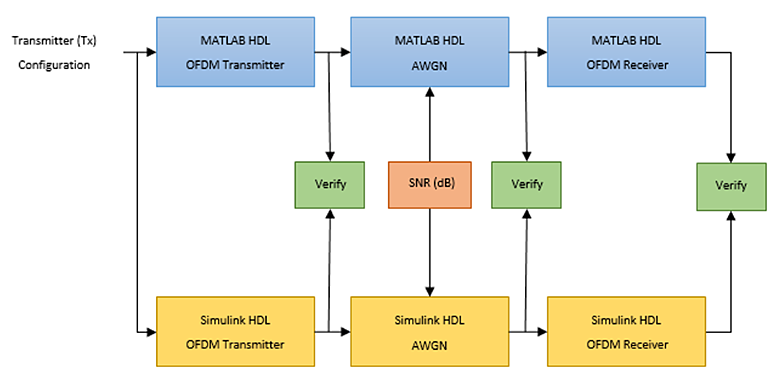

そのため、実装モデルも時間概念を考慮したサンプルベースで改めて作成する必要が有るため、Simulink®というブロック線図の環境でモデルを作成します。後で基準アルゴリズムとの等価検証を行えるように実装モデルの構成としては次図のようにOFDM送信機、白色ガウス雑音生成部、OFDM受信機に分けて実装モデルを作成します。またRFとのインターフェース用の接続ポートも追加します。

※画像クリックで大きな画像が表示されます。

出典:MathWorks OFDM Transmit and Receive Using Xilinx RFSoC Device

https://jp.mathworks.com/help/supportpkg/xilinxsoc/ug/OFDMTransmitandReceiveUsingXilinxRFSoCDevice.html

(参照 2022/02/09)

実装モデルの作成では、基準アルゴリズムを参考にしてフレームベースの処理をサンプルベースのブロックによる処理に置換えていき、適宜シミュレーションにより等価性をチェックして不一致箇所をデバッグします。

次のように基準アルゴリズムでシミュレーションした際の関数毎の入出力信号のログを保存しておき、これと作成した実装モデル上の対応する信号と比較することで等価性のチェックを行います。

出典:MathWorks HDL OFDM MATLAB References

https://jp.mathworks.com/help/wireless-hdl/ug/hdlofdmmatlabreferences.html (参照 2022/02/09)

基準アルゴリズム全体に対するモデル作成が終わり、最終出力の等価性まで確認できたら浮動小数点モデルの完成となりますが、ハードウェア実装する場合は回路規模や動作速度の面で固定小数点の方が有利な場合が多いので、詳細は述べませんが浮動小数点モデル各部のデータ型を固定小数点ツールにより最適な固定小数点型に自動変換します。

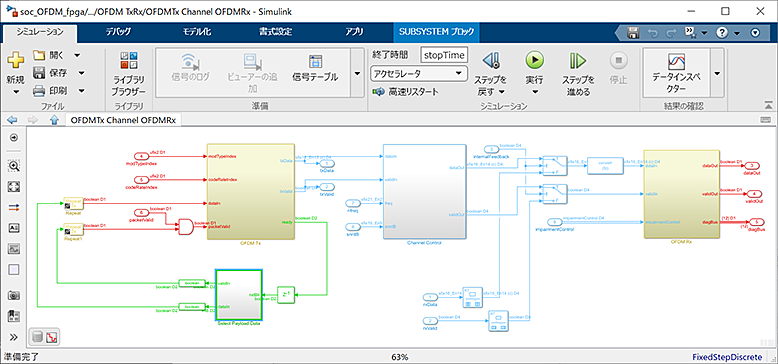

固定小数点変換後の基準アルゴリズムに対応した実装モデルを次に示します。3つ並んだ大きなサブシステムが左からOFDM送信機、白色ガウス雑音生成部、OFDM受信機に対応します。

※画像クリックで大きな画像が表示されます。

出典:MathWorks Japan

このモデルにより基準アルゴリズムに対応した実装モデルは完成しましたが、これをRFSoC搭載ボードに実装するためには、RF帯域ADC/DACとのインターフェースや動作時に必要となるパラメータ制御用インターフェース、動作結果をPC側で観測するためのネットワークインターフェースなどの周辺部がまだ足りません。

そこで、次にRFSoCのADC/DACに対応したブロックなどを含むSoC Blocksetを利用して周辺部を含めた実装モデル化を行います。今回のサンプルでは本Blocksetが提供する以下のブロックを使用します。

- RF Data Converter:RFSoCのADC/DACをモデル化したブロック

- UDP Write:UDPパケットの送信に用いるネットワーク通信用ブロック

- Mem Channel:ネットワーク処理にARMプロセッサも使用するためFPGA側の受信信号をARMプロセッサ側にDMA転送する際に使用するブロック

- Mem Controller:受信信号を外部メモリに記録するためのメモリ制御ブロック

- Register Write:FPGA内レジスタ値をARMプロセッサから設定するためのブロック

SoC Blocksetが提供するこれらのブロックはシミュレーションへの対応に加えて対象ボードは限定されますがHDL又はCいずれかの実装にも対応可能です。

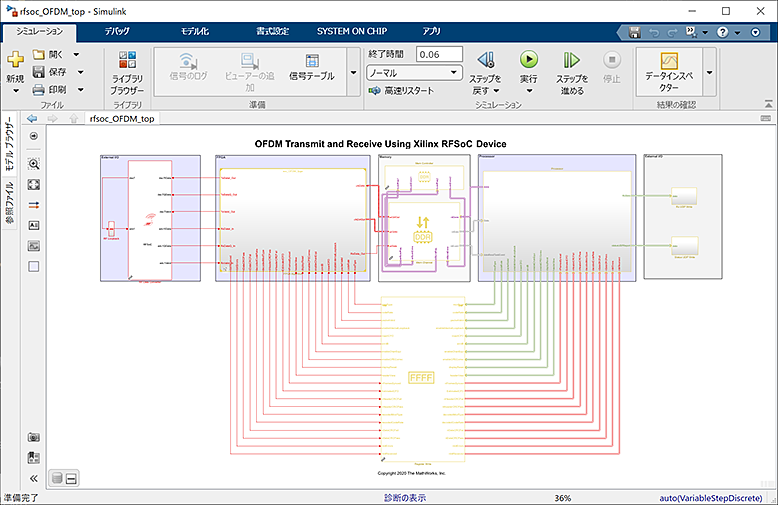

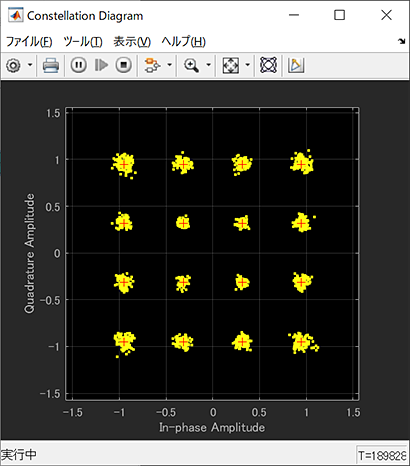

これらを用いて作成したRFSoCシステム全体の実装モデルとシミュレーション結果のコンステレーションを次に示します。実装後もコンステレーションを観測できるように受信波形をUDP Writeブロックで別のモニター用モデルに転送し、転送先モデルでコンステレーションを表示させた結果です。

※画像クリックで大きな画像が表示されます。

出典:MathWorks Japan

出典:MathWorks Japan

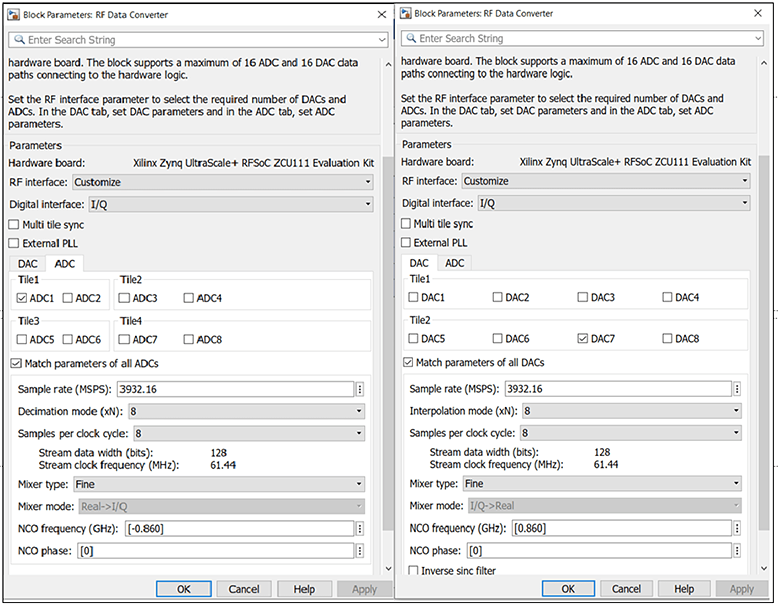

RF Data Converterブロックを開くと次のようにRFSoCデバイスが提供するI/Qミキサの利用の有無、Zynq® UltraScale+™ RFSoC ZCU111 評価キットでは最大8CHのADC/DACに対応しますが、実際に使用するADC/DACの選択などADC/DAC制御に必要なパラメータをモデル上で設定できるようになっており、後のコード生成の際に生成コードに反映されます。

出典:MathWorks HDL OFDM MATLAB References https://jp.mathworks.com/help/wireless-hdl/ug/hdlofdmmatlabreferences.html (参照 2022/02/09)

(5) 実装モデルからのHDL/Cコードの自動生成

前節でRFSoCボード(Xilinx社のZynq® UltraScale+™ RFSoC ZCU111 評価キット)への実装用モデルが完成したので、このモデルからHDL/Cコードを自動生成します。

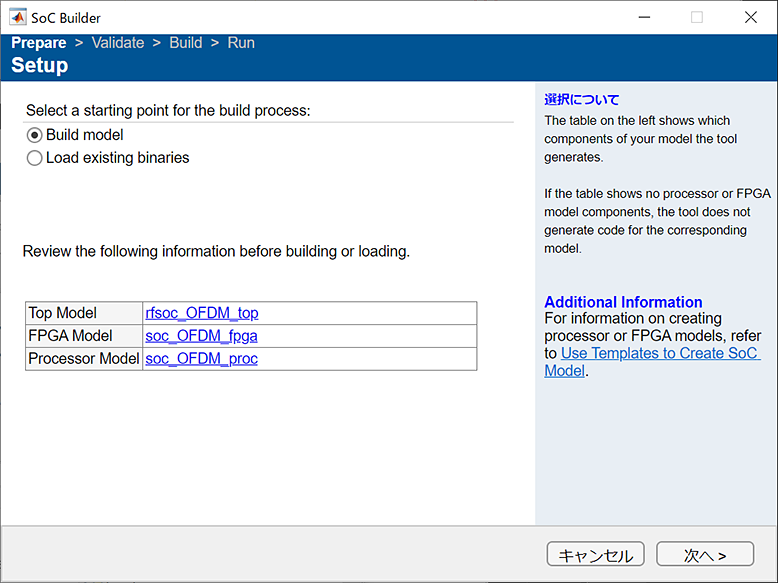

FPGA内蔵SoC向けのHDLコード生成では通常HDL Coderが用意するIPコア生成ワークフローを用いますが、今回はSoC Blocksetが提供するハード/ソフト間をつなぐMem Channelブロックなどを使用しているため、本ブロックセットが用意するコード生成ワークフローを提供するSoC Builderを使用して、HDL/Cの両方のコード生成とビルドを行います。

SoC Builderを起動すると次の画面が開くので指示に従って設定していくとバックグラウンドでHDL Coder及びEmbedded Coderが動作してHDL/Cコードが生成され、更にFPGA合成ツールやクロスコンパイラが呼び出されてSoC内蔵FPGAをプログラムするためのビットストリームファイルとSoC内蔵ARMプロセッサ用バイナリ実行ファイルがビルドされます。

出典:SoC Builder

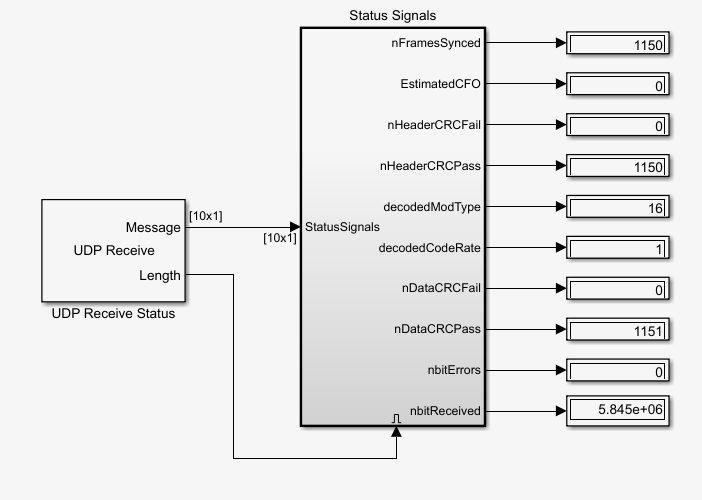

(6) 実装用HDL/CコードのFPGA内蔵SoC評価ボードへの実装と実機検証

時間のかかるFPGA合成終了後、RFSoCボード(Xilinx社のZynq® UltraScale+™ RFSoC ZCU111 評価キット)とMATLAB搭載PCをイーサネットで接続し電源を入れ、SoC Builder上のLoad and Runを実行することでビルドされたビットストリームファイルとプロセッサ用実行ファイルをRFSoCデバイスに転送します。

転送されたビットストリームファイルはRFSoC内部のFPGA部に書込まれる一方、プロセッサ用実行ファイルは内蔵ARMプロセッサに転送されてMATLABとの連携が可能なExternalモード又は単体動作モードで起動され、次の動作結果例のようにボード全体としての動作を開始します。

出典:MathWorks OFDM Transmit and Receive Using Xilinx RFSoC Device

https://jp.mathworks.com/help/supportpkg/xilinxsoc/ug/OFDMTransmitandReceiveUsingXilinxRFSoCDevice.html

(参照 2022/02/09)

出典:MathWorks OFDM Transmit and Receive Using Xilinx RFSoC Device

https://jp.mathworks.com/help/supportpkg/xilinxsoc/ug/OFDMTransmitandReceiveUsingXilinxRFSoCDevice.html

(参照 2022/02/09)

まとめ

本ブログではモデルベースデザイン(MBD)を用いた場合のソフトウェア無線機の開発フローについてOFDM送受信機を具体例に用いて各作業ステップでの実施内容を紹介しました。

このモデルベースデザインを用いた開発フローとRFSoC評価ボードを併用した手法は、上流の実装用モデルの段階で基準アルゴリズムとの等価性を検証でき、実装用モデルからモデルと等価な動作をする実装用HDL/Cコードを自動生成して実装まで行えるため、不具合の発生を抑止し、開発を加速できる手法です 。

今回紹介したOFDM送受信機の具体例は参考資料のリンク先にあるSoC Blockset Support Package for Xilinx Devicesというサポートパッケージの例として提供していますので、MATLAB/Simulink®の評価版と対応するRFSoCボード及び関連FPGAツールを用意することでお試しいただけます。

ここで紹介した手法を取り入れる際には是非、PALTEK社またはMathWorks社までご相談ください。

参考資料

SoC Blockset Support Package for Xilinx Devicesのダウンロードリンク

執筆者紹介

MathWorks Japan シニアアプリケーションエンジニア 中村 勝氏

電子機器メーカーにて無線通信の研究開発に携わり無線インターフェースの開発に従事した後、MathWorks Japanに入社し、現在はHDL実装分野のアプリケーションエンジニアとしてお客様のFPGA/ASIC開発業務に対するMBDワークフローの導入支援活動を主に行っている。