SystemVerilogの基礎知識(検証編)【その3:関数past、onehot / onehot0】

みなさん、こんにちは。

SystemVerilogは、「記述の簡略化」、「その簡略化によって防げる記述ミス」、「解析にかかる時間削減」などのメリットがありますので、お使いいただくことで設計品質を上げることが可能になります。

前回のブログ SystemVerilog の基礎知識(検証編)【その2:関数rose・fell・stable】では、信号の変化を判定する関数として、$rose、 $fell、$stableの記述例について紹介しました。

今回は前回の続きで$past、$onehot / $onehot0 について以下に記載していきます。

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。

目次

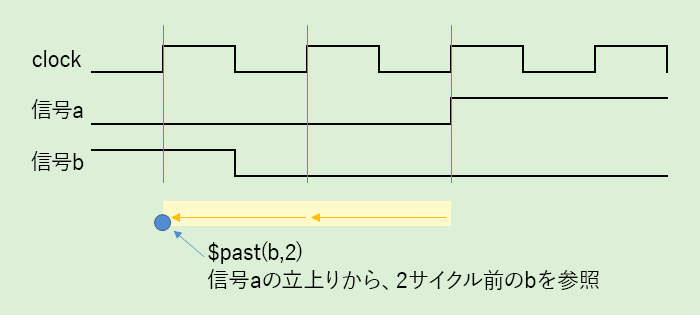

$past()

$past()は、指定サイクル数前(数分さかのぼって)の値を参照します。またサイクル数を指定しなかった場合、1サイクルと見なします。

信号aの立上り検出時、信号bの値(2サイクル前)が“1”であるか判断します

記述例

property p_past(clock,a,b);

@(posedge clock) $rose(a)|->$past(b,2)==1;信号aの立上り信号bの2サイクル前が“1”

endproperty$onehot / $onehot0

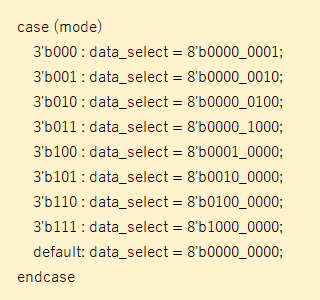

$onehot / $onehot0は、BUS信号のどれか1bitだけが“1”である判断です。

セレクタ回路で使用する関数として、$onehot / $onehot0 があります。

セレクタ回路なので、複数bitに1があるのはNG、どれか1bitの1が期待値です。

- ※

- $onehot0は、ALL0の判断も行えます。

記述例

property p_onehot0(clock,data_select);

@(posedge clock) $onehot0(data_select[7:0]);

endpropertyこのようなセレクタ記述に対して、判断を行います。

などがあります。他にもありますが、別の機会に紹介させていただきます。

ここからは、サンプル記述を載せていきます。

絶対この記述でなくてはいけない!ということではないので、あくまで参考程度としてください。

参考(サンプル記述)

- ※

- クロックposedgeで見ているが、negedgeでも可能、必要に応じて対応しましょう。

1. 信号aと信号bが接続されている

always_comb begin

sva_connect:assert(a===b);

end2. 信号aが8サイクルのレベルである

property p_sample1(clock,a);

@(posedge clock) $rose(a)|=>$stable(a)[*8-1]##1$fell(a);

endproperty3. 信号aを3サイクルシフトし、信号bと一致する

property p_sample2(clock,a,b);

@(posedge clock) a|->##3b;

endproperty4. 信号aが1の間、信号bが1にならない(0のまま)

property p_sample3(clock,a,b);

@(posedge clock) a|->~b;

endproperty5. 信号aが1の間、信号bが変化しない

property p_sample4(clock,a,b);

@(posedge clock) a|=>$stable(b);

endproperty6. 信号aの立ち上がりから5サイクル後に信号bが変化する

property p_sample5(clock,a,b);

@(posedge clock) $rose(a)|->##5$changed(b);

endpropertyおわりに

いかがでしたでしょうか。SystemVerilogの基礎知識についてご理解いただければ幸いです。

設計をするにあたって、検証は必ず行うものです。

検証には、時間をかける必要があり、使いこなせたら結構便利なので、検証時間の短縮に利用できると思います。

あとは、他の参考文献で調べるなど独自で勉強してSystemVerilogを活用していきましょう。

弊社ではFPGA設計や回路図設計、レイアウト設計、ソフトウェア設計、筐体設計などを受託開発しています。

サービス内容をWEBサイトに掲載していますので、ぜひご覧ください。

FPGAの活用に際して設計検討などありましたら、お気軽にお問い合わせください。

最後までお付き合いいただきありがとうございました。

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。