SystemVerilogの基礎知識(検証編)【その2:関数rose・fell・stable】

みなさん、こんにちは。

SystemVerilogは、「記述の簡略化」、「その簡略化によって防げる記述ミス」、「解析にかかる時間削減」などのメリットがありますので、お使いいただくことで設計品質を上げることが可能になります。

SystemVerilogの基礎知識(検証編)【その1:概要】では、主に即時アサーションと並列アサーションの2種あることを記載しました。

アサーションを書くために文法がたくさんあり、全部を使いこなせれば言うことなしですが、これだけ知っていれば検証できるのでは? と思い、よく使用する関数の記述例をあげていきますので、参考にしていただけたらと思います。

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。

目次

- $rose()

- - 記述例 レベルの場合

- $fell()

- - 記述例 レベルの場合

- - 記述例 パルスの場合

- $stable()

- - 記述例

- おわりに

信号の変化を判定する関数として、$rose、$fell、$stableがあります。

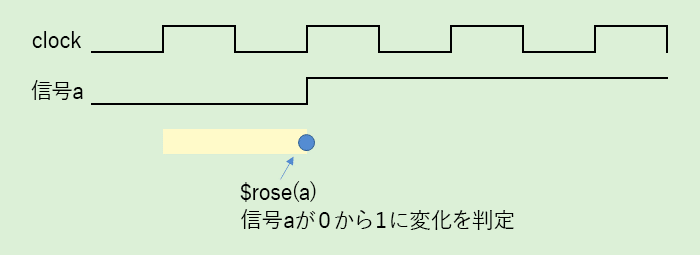

$rose()

$rose()は、ある信号の立上りの判定をします

記述例 レベルの場合

property p_rose(clock,a);

@(posedge clock) $rose(a);clockに同期して、立上りを判定する

endproperty$fell()

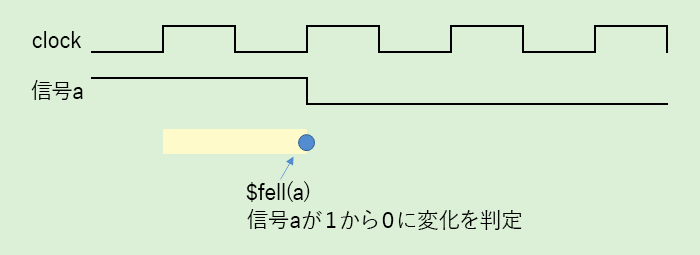

$fell()は、ある信号の立下りの判定をします

記述例 レベルの場合

property p_fell(clock,a);

@(posedge clock) $fell(a);clockに同期して、立下りを判定する

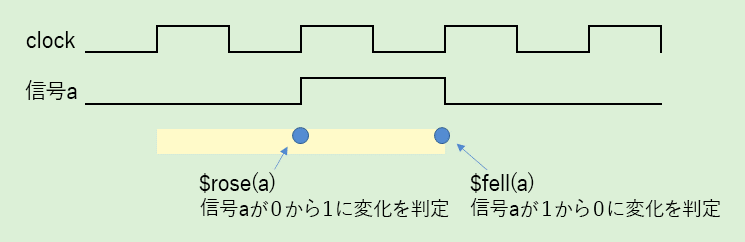

endproperty記述例 パルスの場合

property p_pulse(clock,a);

@(posedge clock) $rose(a)|=>$fell(a);clockに同期して、1サイクルのパルスを判定する

endproperty記述中の |=> は、1サイクル後を表します。

ちなみに、同タイミングは |-> で表します。

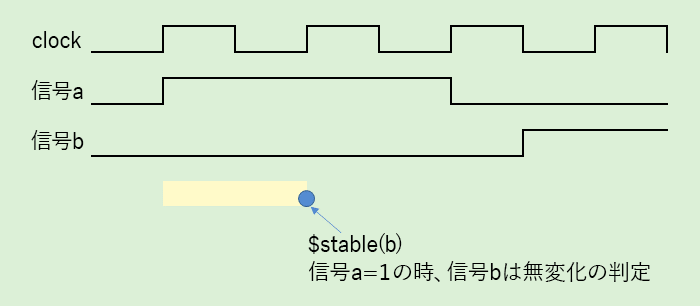

$stable()

$stable()は、ある信号の無変化を判定します

記述例

信号a=1の時、信号bは無変化

property p_stable(clock,a,b);

@(posedge clock) a|=>$stable(b);信号a=1の時、信号bは無変化を判定する

endproperty記述中の |=> は、1サイクル後を表します。

ちなみに、同タイミングは |-> で表します。

おわりに

いかがでしたでしょうか。SystemVerilogの基礎知識についてご理解いただければ幸いです。

以上が信号の立上り、立下り、ある条件+信号の無変化の判定についての内容になります。

nサイクル間の条件や前値の条件を参照比較判定するような記述に関しては、次回以降でお伝えできればと思います。

弊社ではFPGA設計や回路図設計、レイアウト設計、ソフトウェア設計、筐体設計などを受託開発しています。

サービス内容をWEBサイトに掲載していますので、ぜひご覧ください。

FPGAの活用に際して設計検討などありましたら、お気軽にお問い合わせください。

最後までお付き合いいただきありがとうございました。

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。