SystemVerilogの基礎知識(検証編)【その5:typedef】

みなさん、こんにちは。

SystemVerilogは、「記述の簡略化」、「その簡略化によって防げる記述ミス」、「解析にかかる時間削減」などのメリットがありますので、お使いいただくことで設計品質を上げることが可能になります。

今回は、Packageの続きで、typedefについて記載します。

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。

目次

- 1. typedefとは

- 2. パッケージの利用

- 3. 実装例:カウンタ設計

- 3.1 パターン1:4ビット出力

- 3.2 パターン2:8ビット出力

- 4. テストベンチの作成

- 5. シミュレーション結果

- 6. おわりに

1. typedefとは

typedefは、ユーザー定義型です。ユーザーが任意のデータタイプを定義でき、パッケージ内で宣言できるので、複数のファイルで参照することができます。

記述の工夫で、見やすさ、記述の修正のしやすさが出てきます。

【記述例:typedef】

example3_pkg.sv

package example3_pkg;

typedef logic ex_type;

endpackage2. パッケージの利用

パッケージファイル名は、example3_pkg

typedef定義を使用し、ユーザータイプ “ex_type” としています。

単純ですが、カウンタ記述でPackageを使用していきます。

今回は、TOPファイルを2種類用意し、それぞれのパターンについて述べていきます。

3. 実装例:カウンタ設計

3.1 パターン1:4ビット出力

- 出力を4bit

- 任意のクロック使用

- リセット解除後、インクリメント開始

3.2 パターン2:8ビット出力

- 出力を8bit

- 任意のクロック使用

- リセット解除後、インクリメント開始

4. テストベンチの作成

前項で紹介した2種類の動作確認を行います。

example3_top1.sv

module example3_top1 (

output example3_pkg::ex_type [3:0] count,

input example3_pkg::ex_type clock, reset );

always @(posedge clock, posedge reset)

if (reset) begin

count <= 0;

end else begin

count <= count + 1;

end

endmodule本RTLでは、output example3_pkg::ex_type [3:0] count, としているので出力は4bitになります。

example3_top2.sv

import example3_pkg::ex_type;

module example3_top2 (

output ex_type [7:0] count,

input ex_type clock, reset );

always @(posedge clock, posedge reset)

if (reset) begin

count <= 0;

end else begin

count <= count + 1;

end

endmodule本RTLでは、output ex_type [7:0] count, としているので出力は8bitになります。

- ※

- enample3_top1との違いは、出力bitもそうですが、importする方法で記述しています。

【動作確認用のテストベンチ】

example3_tb.sv

`timescale 1ns/1ps

`default_nettype none // Do not to infer wiring.

module example3_tb ();

//---------------------------------//

reg reset; // Active-H

initial begin reset = 1'b1; end

always #(800)begin reset = 1'b0;end

reg clock;

initial begin clock = 1'b0;end

always #(12.5)begin clock = ~clock;end

//---------------------------------//

example3_top1 u_example3_top1 (

.reset ( reset ),

.clock ( clock ),

.count ( ));

example3_top2 u_example3_top2 (

.reset ( reset ),

.clock ( clock ),

.count ( ));

//---------------------------------//

endmodule

`default_nettype wire- ※

- リセット時間、クロック周期は任意

先ほど記載したTOPファイル2種類を同時に確認したいので、本テストベンチには、example3_top1、example3_top2を見ています。

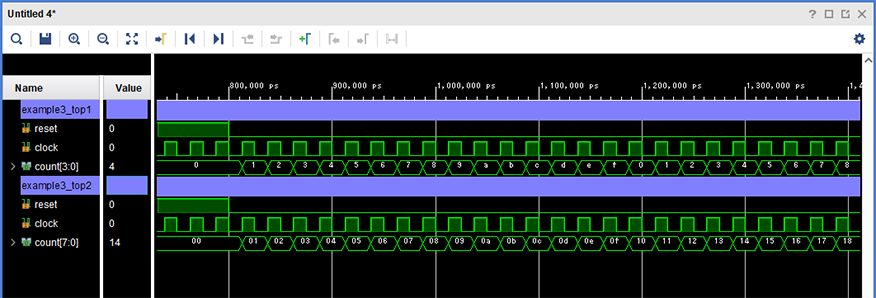

5. シミュレーション結果

シミュレーション結果は、以下になります。

ここで、example3_top1では、4bit出力のため、0x0~0xFのカウンタ値が繰り返されています。

example3_top2では、8bit出力のため、0x00~0xFFのカウンタ値が繰り返されます。(波形には見えていません。)

Vivadoに読み込ませたファイルは、以下の4種になります。

- example3_pkg.sv

- example3_top1.sv

- example3_top2.sv

- example3_tb.sv

シミュレーションを実行すると、期待動作していることが確認できます。

Package化することで、ファイルの行数の削減、見やすさの工夫ができますので、参考にしていただけますと幸いです。

6. おわりに

いかがでしたでしょうか。SystemVerilogの基礎知識についてご理解いただければ幸いです。

弊社ではFPGA設計や回路図設計、レイアウト設計、ソフトウェア設計、筐体設計などを受託開発しています。

サービス内容をWEBサイトに掲載していますので、ぜひご覧ください。

FPGAの活用に際して設計検討などありましたら、お気軽にお問い合わせください。

最後までお付き合いいただきありがとうございました。

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。