【アナログ回路豆知識】ESD測定回路とESD外部保護回路例

電気回路は集積化が進んでいますが、ダイオードやトランジスタ、MOS FETなどのディスクリート部品は、ICの周辺回路や各IC間の接続部に使われ、まだまだなくてはならない存在です。

アナログ回路設計の中でこれらディスクリート部品を使った具体的な回路例などの情報を、「アナログ回路豆知識」と題してお伝えしていきたいと思います。

まず、第1回目は「ESD測定回路とESD外部保護回路例」です。 ESD(静電気)は半導体の破壊につながる最も大きな要因と言えるものなので、設計の中でこの対策について考慮が必要です。では、具体的にお話ししてまいります。

ESD保護回路

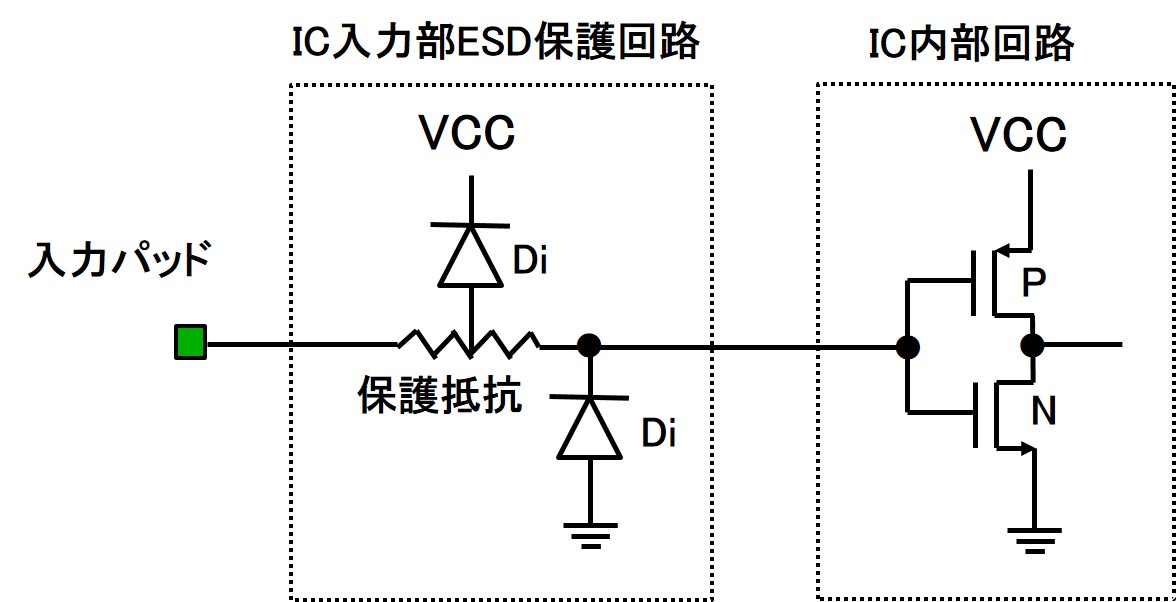

IC内部にはESD保護回路がチップのボンデングパットと内部回路との間に組み込まれており、ICの入出力端子に加わるESDサージから内部回路の破壊を防止しています。

図1にICのESD保護回路の一例を示しています。

入力端子に加わるサージ電圧はこのESD保護回路の抵抗とダイオードによってVCCあるいはGNDにクランプされて、IC内部回路にサージ電圧が加わらないようになっています。

通常ICのESD耐圧は機械モデルで200V以上、人体モデルで2000V以上を保証しています。

図1 ESD保護回路例

ESD測定回路

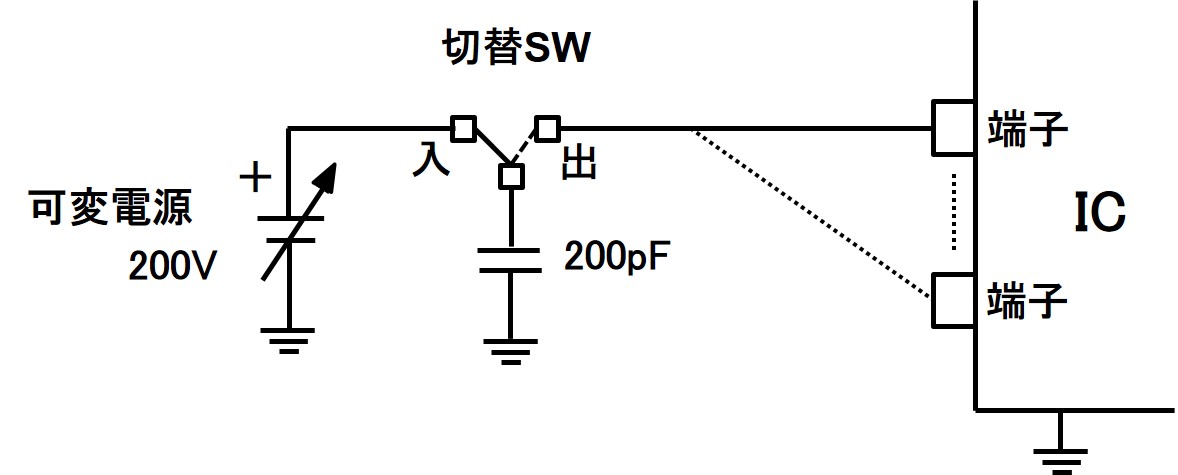

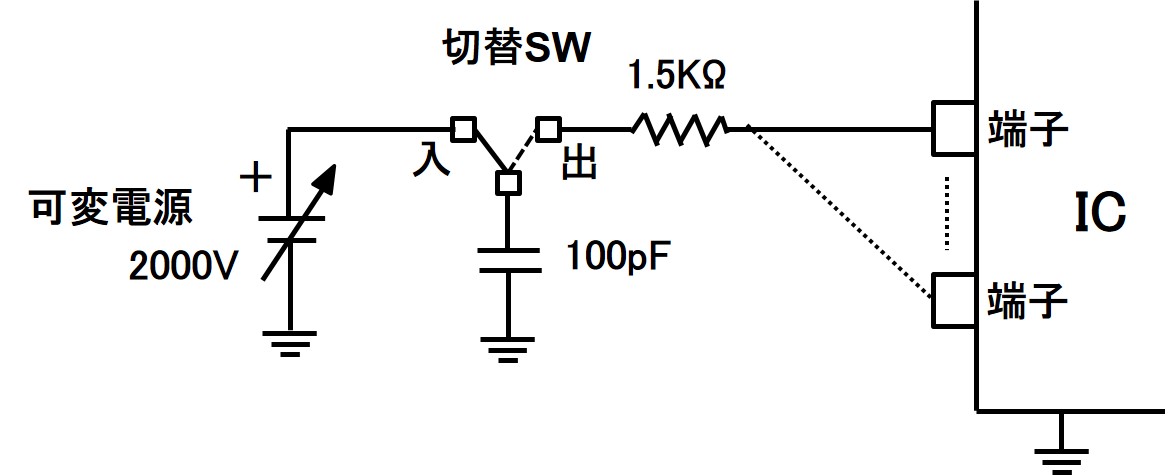

図2a、図2bにESD(静電耐圧)測定回路を記載しています。

図2a機械モデルで測定動作を説明します。

まず切替SWを入側に接続して、200pFコンデンサに200Vを充電します。

そして切替SWの出とICの測定端子間を接続して、次に切替SWを出側に切替え200pFコンデンサに充電された200Vを測定端子に印加します。

このような測定動作をICの全端子について行い、その後ICテスターで動作チェックを行います。

正常動作すれば、その印加電圧でESD耐圧をクリアしたことになります。

もし動作不良となったときは、動作不良になる1ステップ前の低い印加電圧がESD耐圧となります。

実際の測定はいきなり高い200Vを印加するのではなく低い印加電圧から開始します。

ESDは通常200V以上

ESDは通常200V以上

全ての端子に順次印加して行きICの動作チェックを行う。

動作不良になる1ステップ前の印加電圧がESD電圧となる。

図2a ESD(静電耐圧)測定回路 機械モデル(MM)

ESDは通常2000V以上

ESDは通常2000V以上

全ての端子に順次印加して行きICの動作チェックを行う。

動作不良になる1ステップ前の印加電圧がESD電圧となる。

図2b ESD(静電耐圧)測定回路 人体モデル(HBM)

ESD破壊と対策例

電子機器のPC基板やモジュールにICを実装後、構造・配置・取扱上の理由からICの入出力端子に高いESDが加わりICを破壊する可能性があります。

そのようなときは、ESD保護用ダイオードやバリスタをICの入出力端子近くの信号線とGND間に挿入することで解決できます。

ESD保護素子

この説明ではNexperia社のESD保護用ダイオードPESD5V0C1USF、サージ吸収TVSダイオードPTVS5V0Z1USKP、PTVS5V0S1URとPanasonic社チップ形積層バリスタEZJZ0V80010を例に説明します。

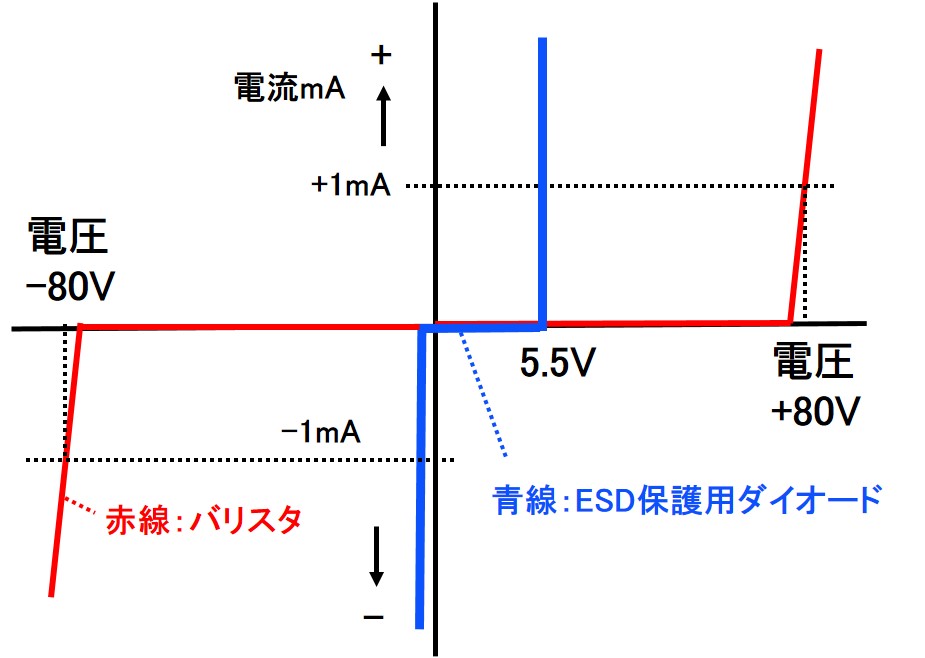

図3にESD保護用ダイオードPESD5V0C1USFとEZJZ0V80010バリスタの電圧-電流特性を掲載しています。

電気的特性を比較すると、

PESD5V0C1USFは、Vbr電圧がmin5.5Vtyp9Vと低くまたIppmがmax9A、端子間容量Cd(Ct)がtyp0.45pFとなっています。

一方バリスタEZJZ0V80010は、バリスタ電圧(保護電圧)がtyp±80Vと高く端子間容量がtyp0.8pFと小さくなっています。

ここでは、端子間容量の小さい製品を選択しています。

その理由は通常ICの入力端子容量がtyp3~5pF程度のため、大きな端子容量の保護素子を挿入して信号線の信号波形が鈍るのを防止するためです。

ESD保護用ダイオードやバリスタは各社から発売されており、保護電圧の種類や端子間容量が1pF、5pF、15pF、数100pF、数1000pFなど多くの製品がありますので、信号のスピードや端子間容量値を気にしない電源ラインなどの用途に応じて使い分けできます。

サージ吸収TVSダイオードPTVS5V0Z1USKP、PTVS5V0S1URなどは、高速性を要求しない低速動作でサージ吸収を兼ねた応用回路に採用されます。

ESD保護用ダイオード

ESD保護用ダイオード

Nexperia社 PESD5V0C1USF

VBRmin5.5Vtyp9V@IR1mA、端子間容量Ct:typ0.45pF

図3 ESD保護用ダイオードPESD5V0C1USFとEZJZ0V80010バリスタの電圧-電流特性

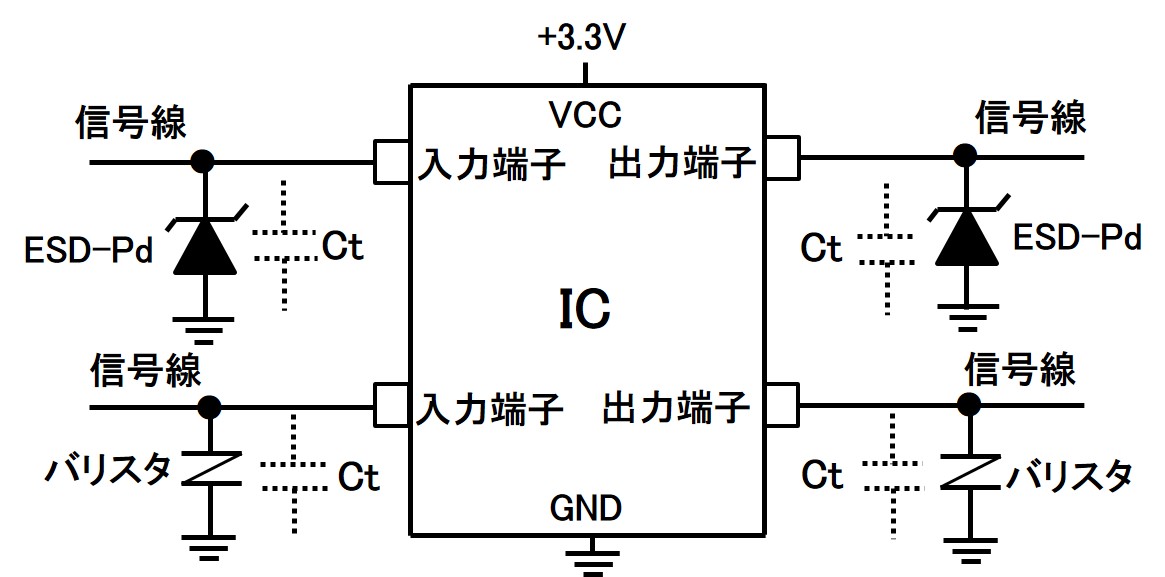

対策応用回路例

図4に応用回路例を掲載しています。

図4から信号線に加わったESDは、挿入したESD保護用ダイオードやバリスタを通してGNDに放電され、ICの端子に加わるESD電圧は挿入したVbr電圧やバリスタ電圧にクランプされます。

従って上記クランプ電圧が、ICの入出力端子のESD耐圧以下で十分低ければICをESDから保護できます。

PESD5V0C1USFはクランプ電圧がmin5.5V / typ9Vとなっているので、クランプ電圧を低く設定する場合に適しています。

このクランプ電圧はICの動作電圧より余裕を見て数V高く設定する必要があります。min+5.5Vtyp9V製品ならば、動作電圧が3.3V以下のIC回路に使用できます。

EZJZ0V80010は端子間容量がtyp0.8pFと小さいので超高速信号ライン用やバリスタ電圧(クランプ電圧)がtyp±80Vとなっていますので±電源のアナログ回路などに適しています。

最大許容回路電圧、即ちバリスタに連続して印加できる最大電圧値が10Vとなっていますので、ICの動作電圧は10V未満で使用することになります。動作電圧が5V以下なら問題ありません。

ESD-Pd:ESD保護用ダイオード PESD5V0C1USF

ESD-Pd:ESD保護用ダイオード PESD5V0C1USF

Ct:端子間容量

(バリスタ推奨例)

Panasonic EZJD0V80010

最大許容回路電圧:DC10V

バリスタ電圧 公称±80V@1mA

端子間容量Ct:typ0.8pF/max1.0pF @f=1MHz

図4 ESD保護用ダイオードとバリスタを挿入した応用回路例

■注意

・ICによっては特定の端子において機械モデルで200V、人体モデルで2000Vをクリアできない製品がある可能性があります。

・個々のICのESD保護回路は、特許がありメーカーから公開されていませんので不明です。

図1はESD保護回路の一例です。

まとめ

今回はESD保護回路に使う部品として、

このうちESD保護用ダイオード、

https://www.paltek.co.jp/

次回のアナログ回路豆知識は、「バイポーラトランジスタの応用回路例」についてお伝えします。