Zynq® UltraScale+™ MPSoC PetaLinux® FSBL起動時のQSPI CLOCKの変更方法

皆さん、こんにちは。

本ブログはPetaLinux® 2020.2を使用する際、AMD社のZynq® UltraScale+™ MPSoC FSBLを起動したときのQSPI CLOCKの変更方法や、PetaLinux®の環境でFSBLを変更する方法を紹介したいと思います。

このブログは「FPGA設計ブログ一覧」の

5. プログラミング(FPGAへの書き込み)の

ひとつです。

目次

はじめに

PetaLinux® ツールは、AMD社のプロセッシング システム上でエンベデッド Linux ソリューションをカスタマイズ、ビルド、およびデプロイするために必要なものをすべて提供します。

設計生産性の加速を目的とするこのソリューションは、AMD社のハードウェア設計ツールと連動し、Versal®、Zynq® UltraScale+™ MPSoC、Zynq®-7000 SoC、および MicroBlaze™ 向けの Linux システム開発を容易にします。

背景

デフォルトではFSBLのQSPI分周数は8です。Zynq® UltraScale+™ MPSoCのQSPI CLOCK最高設定は300Mhz、FSBL起動時QSPIデバイスのCLOCK周波数300/8=37.5Mhzになります。

次の方法で、FSBL起動時のQSPI動作周波数カスタマイズが可能です。

手順

1. 希望のQSPI動作周波数を決定

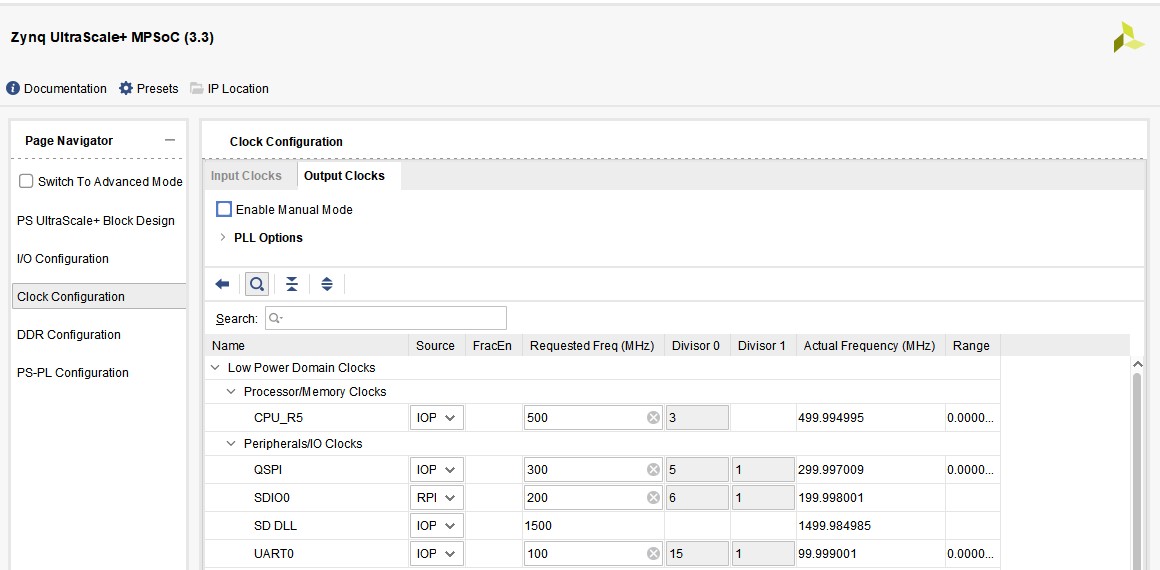

①および②の設定周波数を算出します

- ①

- FSBLの分周数(2から256)

- ②

- Vivado® GUI Zynq® UltraScale+™ MPSoC → CLOCK configuration → Peripherals/IO Clocks → QSPI

QSPI動作周波数=②/①になります。

2. FSBLのソースをローカルに保存

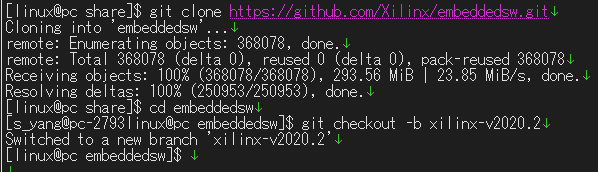

git clone https://github.com/Xilinx/embeddedsw.git

cd embeddedsw

git checkout -b xilinx-v2020.2出典:ubuntu18.04の画面キャプチャ

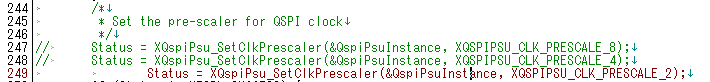

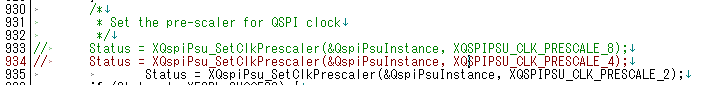

3. 以下の保存したファイルを開き、必要に応じて変更

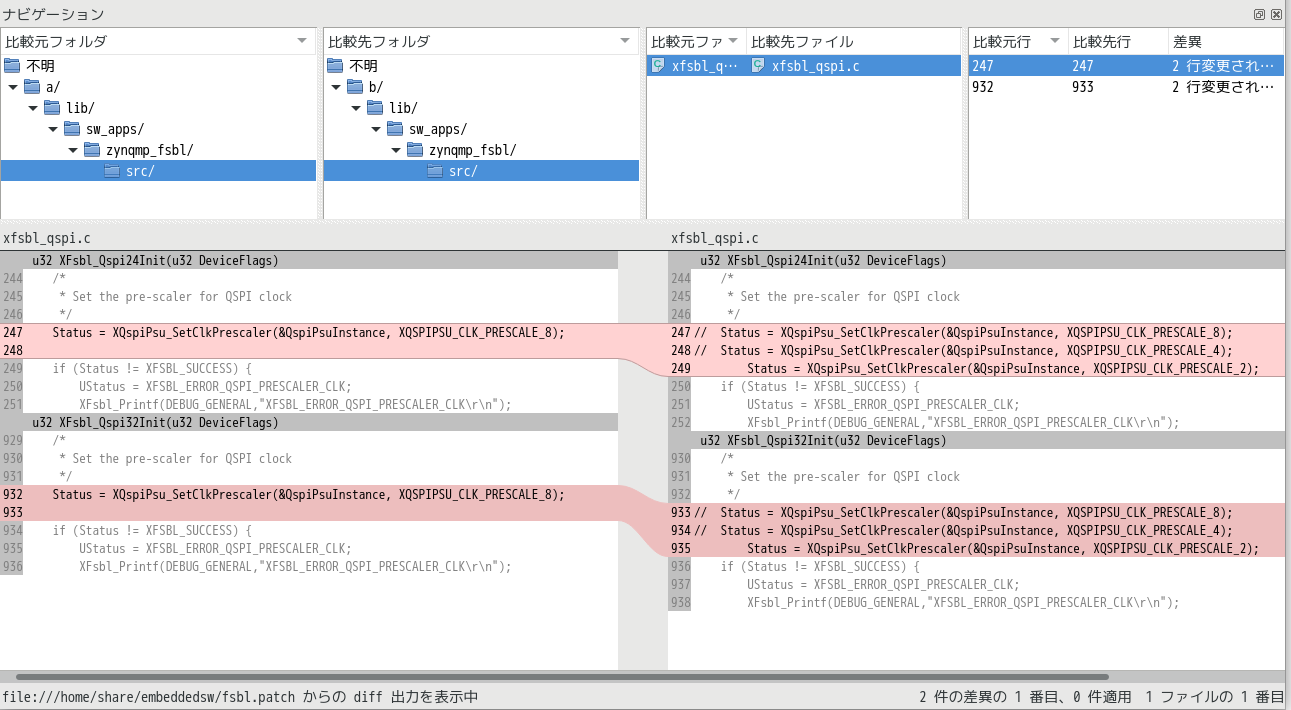

/embeddedsw/lib/sw_apps/zynqmp_fsbl/src /xfsbl_qspi.cを開きます。

XQspiPsu_SetClkPrescaler(&QspiPsuInstance, XQSPIPSU_CLK_PRESCALE_8)を探して、必要に応じて変更します。

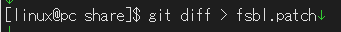

4. git diff > fsbl.patch コマンドで fsbl.patch を生成する

出典:ubuntu18.04の画面キャプチャ

出典:ubuntu18.04の画面キャプチャ

5. Vivado® GUIで Zynq® UltraScale+™ MPSoC を開き、必要に応じてQSPIの設定周波数を変更する

出典:Vivado® ML Edition

6. 参考

以前のブログ PetaLinux®の環境でFSBLを変更する方法を参考に、FSBLを再ビルドすることで、QSPIは期待した動作周波数でFSBLをBOOTすることができます。

おわりに

弊社ではFPGA設計や回路図設計、レイアウト設計、ソフトウェア設計、筐体設計などを受託開発しています。サービス内容をWEBサイトに掲載していますので、ぜひご覧ください。

FPGAの活用に際して設計検討などありましたら、お気軽にお問い合わせください。

最後までお付き合いいただきありがとうございました。